Reference Manual ADuCM356

REGISTER DETAILS: SPI0/SPI1

analog.com Rev. A | 249 of 312

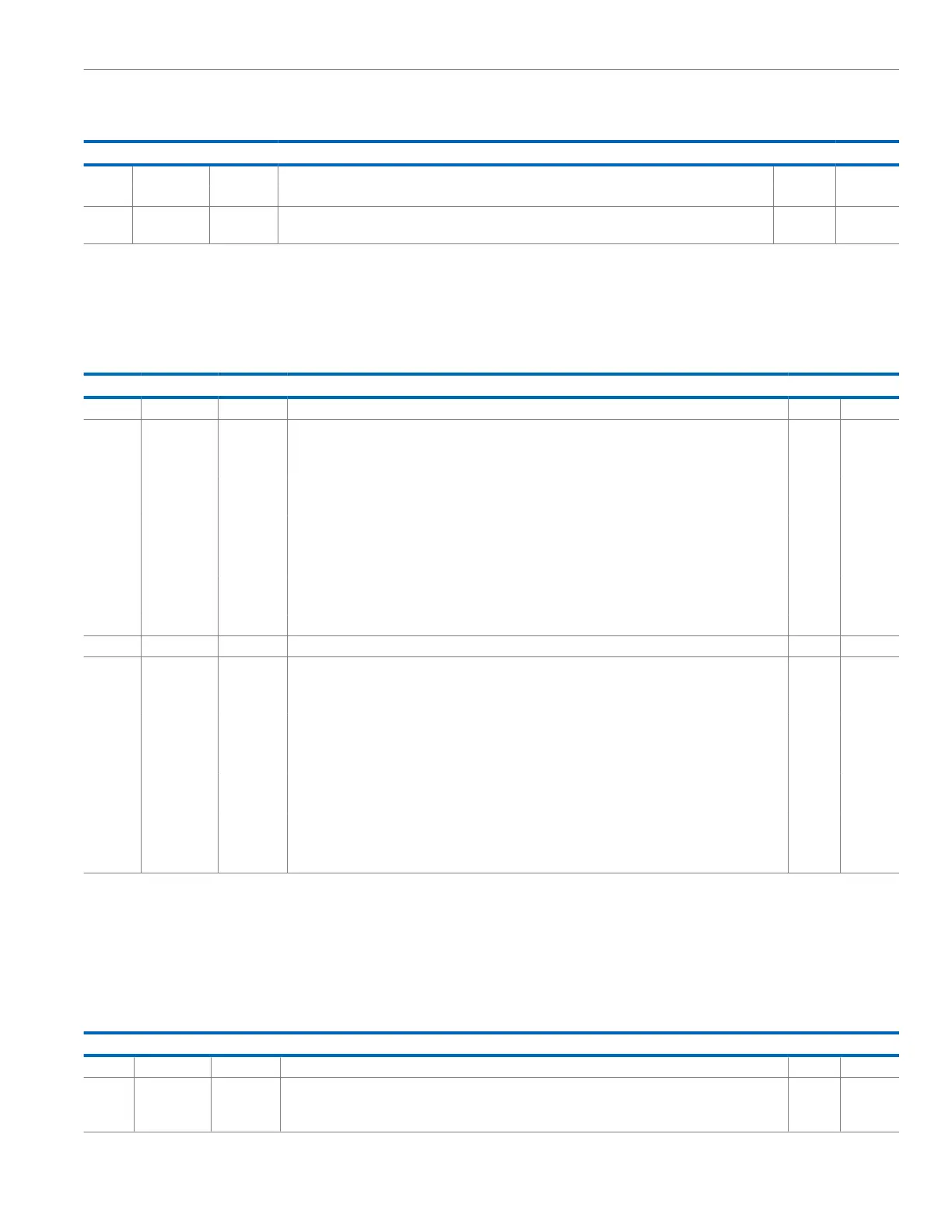

Table 313. Bit Descriptions for SPI0_DMA, SPI1_DMA (Continued)

Bits Bit Name Settings Description Reset Access

0 Disable transmit DMA interrupt.

1 Enable transmit DMA interrupt.

0 EN Enable DMA for Data Transfer. Set by user code to start a DMA transfer. Cleared by user code at the

end of DMA transfer. This bit must be cleared to prevent extra DMA requests to the µDMA controller.

0x0 R/W

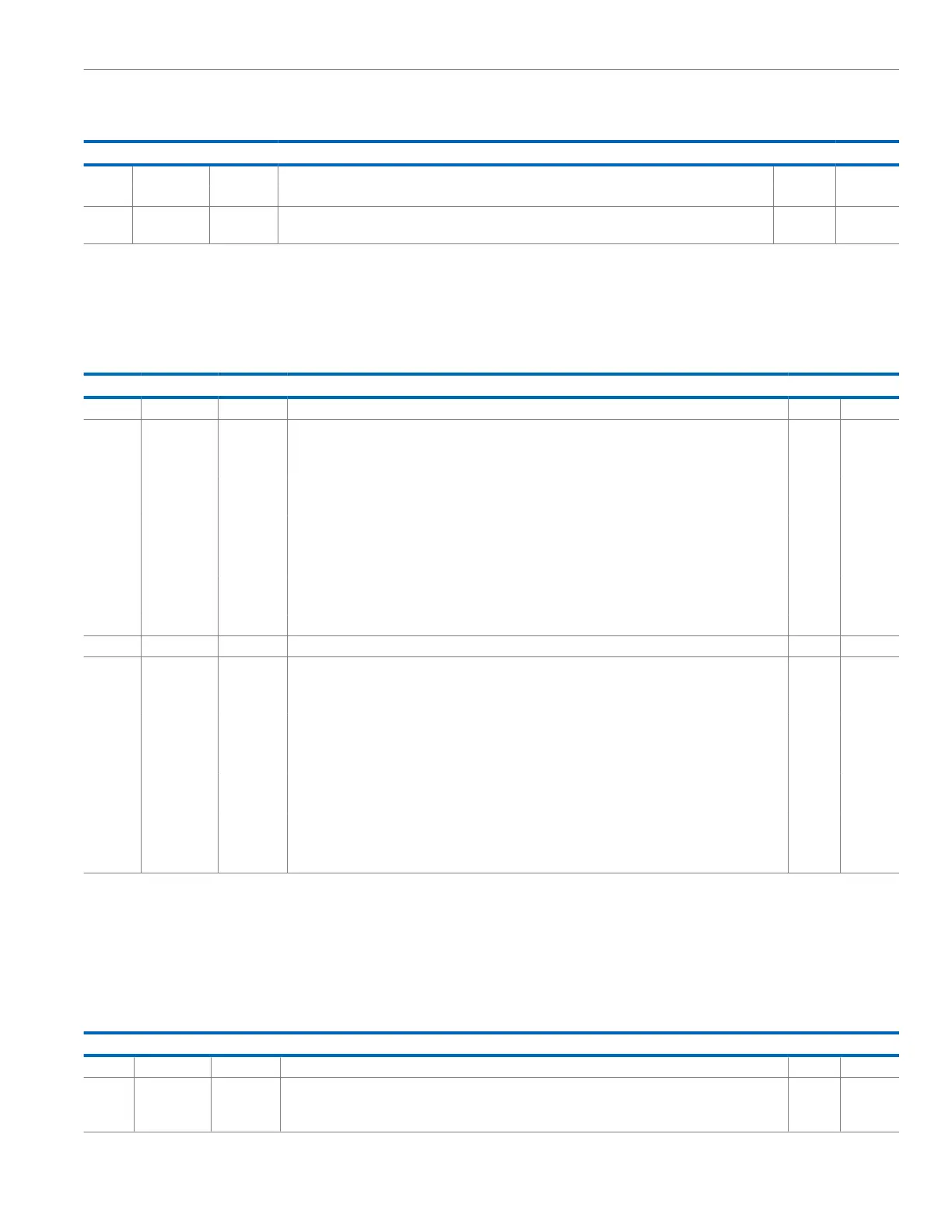

FIFO STATUS REGISTERS

Address: 0x40004020, Reset: 0x0000, Name: SPI0_FIFO_STAT

Address: 0x40024020, Reset: 0x0000, Name: SPI1_FIFO_STAT

Table 314. Bit Descriptions for SPI0_FIFO_STAT, SPI1_FIFO_STAT

Bits Bit Name Settings Description Reset Access

[15:12] Reserved Reserved. 0x0 R

[11:8] RX SPI Receive FIFO Status. This field specifies the number of bytes in the receive FIFO when the DMA is

disabled. In DMA mode, these bits refer to the number of half words in the receive FIFO.

0x0 R

0000 Receive FIFO empty.

0001 1 valid byte or half word in the receive FIFO.

0010 2 valid bytes or half words in the receive FIFO.

0011 3 valid bytes or half words in the receive FIFO.

0100 4 valid bytes or half words in the receive FIFO.

0101 5 valid bytes or half words in the receive FIFO.

0110 6 valid bytes or half words in the receive FIFO.

0111 7 valid bytes or half words in the receive FIFO.

1000 8 valid bytes or half words in the receive FIFO. Receive FIFO full.

[7:4] Reserved Reserved. 0x0 R

[3:0] TX SPI Transmit FIFO Status. This field specifies the number of bytes in the transmit FIFO when DMA is

disabled. In DMA mode, these bits refer to the number of half words in the transmit FIFO.

0x0 R

0000 Transmit FIFO empty.

0001 1 valid byte or half word in the transmit FIFO.

0010 2 valid bytes or half words in the transmit FIFO.

0011 3 valid bytes or half words in the transmit FIFO.

0100 4 valid bytes or half words in the transmit FIFO.

0101 5 valid bytes or half words in the transmit FIFO.

0110 6 valid bytes or half words in the transmit FIFO.

0111 7 valid bytes or half words in the transmit FIFO.

1000 8 valid bytes or half words in the transmit FIFO. Transmit FIFO full.

READ CONTROL REGISTERS

Address: 0x40004024, Reset: 0x0000, Name: SPI0_RD_CTL

Address: 0x40024024, Reset: 0x0000, Name: SPI1_RD_CTL

This register is only used in initiator mode.

Table 315. Bit Descriptions for SPI0_RD_CTL, SPI1_RD_CTL

Bits Bit Name Settings Description Reset Access

[15:9] Reserved Reserved. 0x0 R

8 THREEPIN 3-Pin SPI Mode. This field specifies if the SPI interface has a bidirectional data pin (3‑pin interface) or

dedicated unidirectional data pins for transmit and receive (4-pin interface). This bit is only valid in read

command mode and when SPIx_FLOW_CTL, Bits[1:0] = 0b01. If 3-pin mode is selected, the MOSI pin

0x0 R/W

Loading...

Loading...