Reference Manual ADuCM356

REGISTER DETAILS: DMA

analog.com Rev. A | 176 of 312

PER CHANNEL INVALID DESCRIPTOR CLEAR REGISTER

Address: 0x40010050, Reset: 0x00000000, Name: INVALIDDESC_CLR

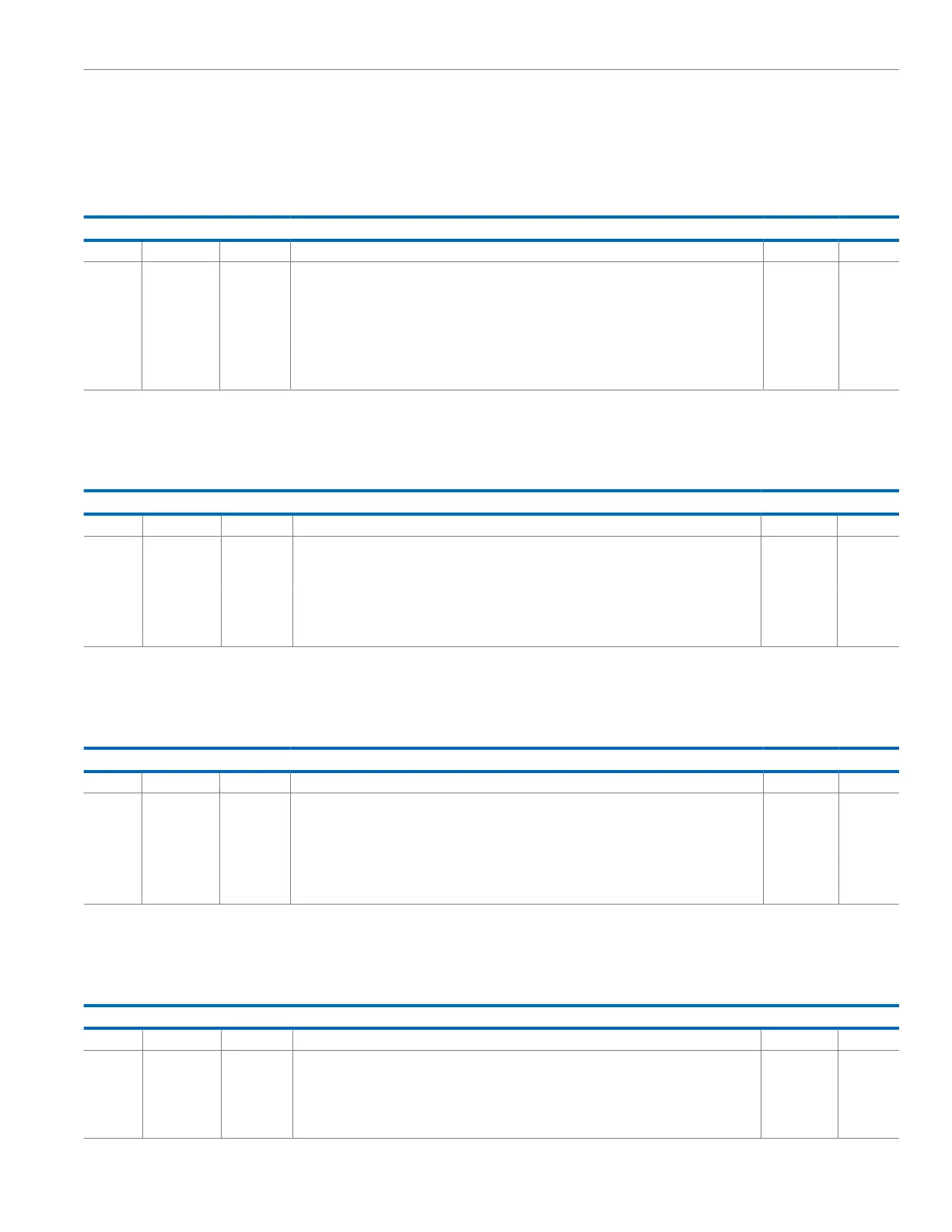

Table 212. Bit Descriptions for INVALIDDESC_CLR

Bits Bit Name Settings Description Reset Access

[31:24] Reserved Reserved. 0x00 R

[23:0] CHAN Per Channel Invalid Descriptor Status and Per Channel Invalid Descriptor Status Clear. This

register is used to read and clear the per channel DMA invalid descriptor status. The per channel

invalid descriptor status is set if the controller reads an invalid descriptor (whose cycle control is

0b000). If the controller reads invalid cycle control for a channel, that channel is automatically

disabled by the controller. The other channels are unaffected. Write 1 to clear bits.

0x000000 R/W1C

0 When read as 0, no invalid cycle control has occurred. When written as 0, no effect.

1 When read as 1, an invalid cycle control is pending. When written as 1, bit is cleared.

CHANNEL BYTES SWAP ENABLE SET REGISTER

Address: 0x40010800, Reset: 0x00000000, Name: BS_SET

Table 213. Bit Descriptions for BS_SET

Bits Bit Name Settings Description Reset Access

[31:24] Reserved Reserved. 0x00 R

[23:0] CHAN Byte Swap Status. This register is used to configure a DMA channel to use byte swap. Each bit of

the register represents the corresponding channel number in the DMA controller. Bit 0 corresponds

to DMA Channel 0. Bit M − 1 corresponds to DMA Channel M – 1.

0x000000 R/W

0 When read as 0, Channel C byte swap is disabled. When written as 0, no effect.

1 When read as 1, Channel C byte swap is enabled. When written as 1, byte swap on Channel C is

enabled.

CHANNEL BYTES SWAP ENABLE CLEAR REGISTER

Address: 0x40010804, Reset: 0x00000000, Name: BS_CLR

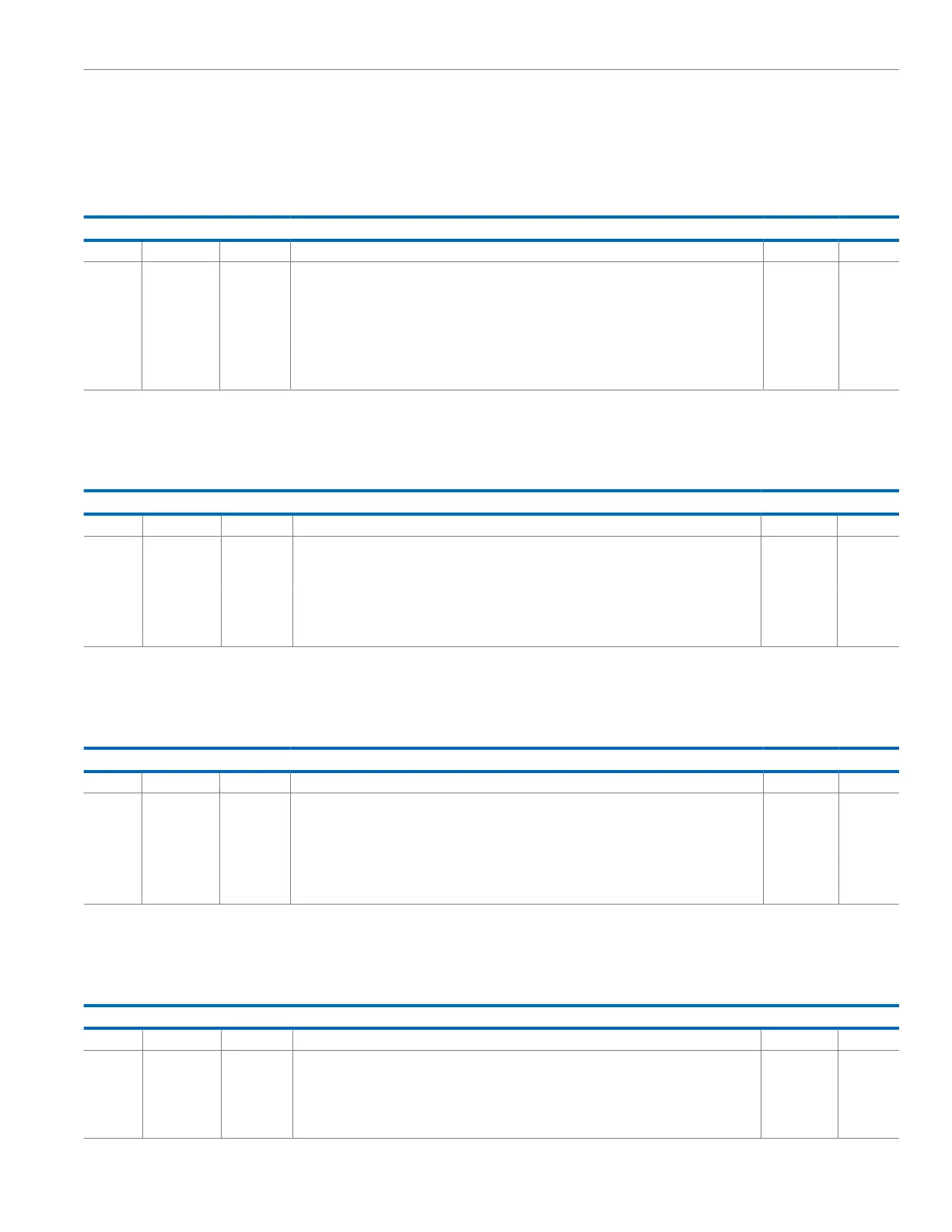

Table 214. Bit Descriptions for BS_CLR

Bits Bit Name Settings Description Reset Access

[31:24] Reserved Reserved. 0x00 R

[23:0] CHAN Disable Byte Swap. The BS_CLR write only register enables the user to configure a DMA channel

to not use byte swapping and use the default operation. Each bit of the register represents the

corresponding channel number in the DMA controller. Bit 0 corresponds to DMA Channel 0. Bit M −

1 corresponds to DMA Channel M – 1.

0x000000 W

0 No effect. Use the BS_SET register to enable byte swap on Channel C.

1 Disables byte swap on Channel C.

CHANNEL SOURCE ADDRESS DECREMENT ENABLE SET REGISTER

Address: 0x40010810, Reset: 0x00000000, Name: SRCADDR_SET

Table 215. Bit Descriptions for SRCADDR_SET

Bits Bit Name Settings Description Reset Access

[31:24] Reserved Reserved. 0x00 R

[23:0] CHAN Source Address Decrement Status and Configure Source Address Decrement. The

SRCADDR_SET register is used to configure the source address of a DMA channel to decrement

the address instead of incrementing the address after each access. Each bit of the register

represents the corresponding channel number in the DMA controller. Bit 0 corresponds to DMA

Channel 0. Bit M − 1 corresponds to DMA Channel M – 1.

0x000000 R/W

Loading...

Loading...