Reference Manual ADuCM356

REGISTER DETAILS: SYSTEM RESETS

analog.com Rev. A | 37 of 312

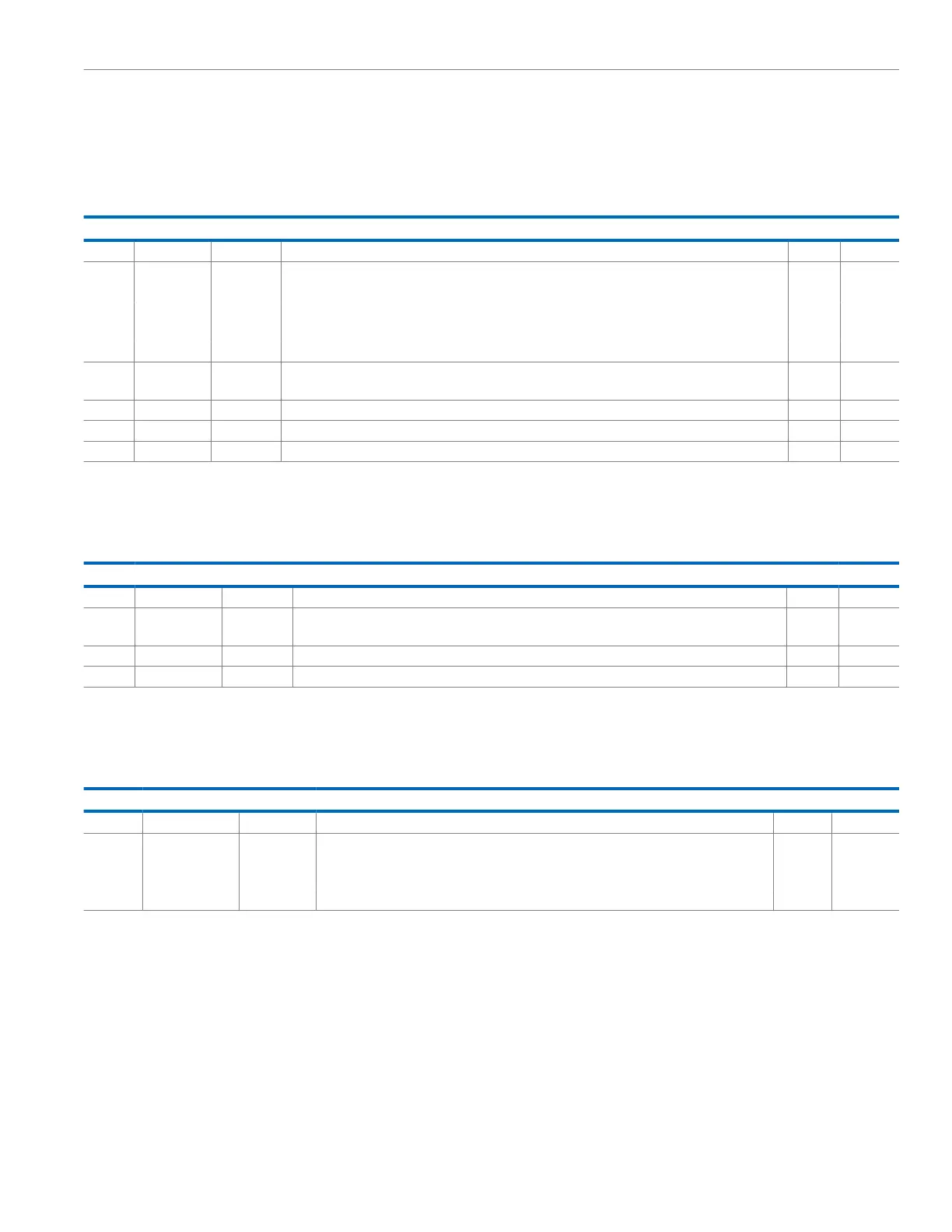

DIGITAL DIE RESET STATUS REGISTER

Address: 0x4004C040, Reset: 0x000000XX, Name: RST_STAT

Table 37. Bit Descriptions for RST_STAT

Bits Bit Name Settings Description Reset Access

[15:6] Reserved Reserved. 0x0 R

[5:4] PORSRC POR Source for Digital Die. This bit contains additional details after a POR occurs. R/W

00 POR triggered because DVDD drops below POR threshold.

01 POR triggered because DVDD drops below POR threshold.

10 POR triggered because DVDD_REG supply drops below 1.08 V.

11 POR triggered because DVDD_REG drops below fail-safe.

3 SWRST Software Reset. Set automatically to 1 when the Arm Cortex-M3 system reset is generated. Cleared by

writing 1 to the bit.

0x0 R/W1C

2 Reserved Reserved. 0x0 R/W1C

1 EXTRST External Reset. Set automatically to 1 when an external reset occurs. Cleared by writing 1 to the bit. 0x0 R/W1C

0 POR POR. Set automatically when a POR occurs. Cleared by writing 1 to the bit. 0x0 R/W1C

ALWAYS ON RESET STATUS REGISTER

Address: 0x400C0A40, Reset: 0x000X, Name: RSTSTA

Table 38. Bit Descriptions for RSTSTA

Bits Bit Name Settings Description Reset Access

[15:3] Reserved Reserved. 0xX R

2 WDRST Watchdog Timeout. Set automatically to 1 when a watchdog timeout occurs. Cleared by writing 1 to the

bit.

0xX R/W1C

1 EXTRST External Reset. Set automatically to 1 when an external reset occurs. Cleared by writing 1 to the bit. 0xX R/W1C

0 POR AFE POR. Set automatically when a POR occurs. Cleared by writing 1 to the bit. 0xX R/W1C

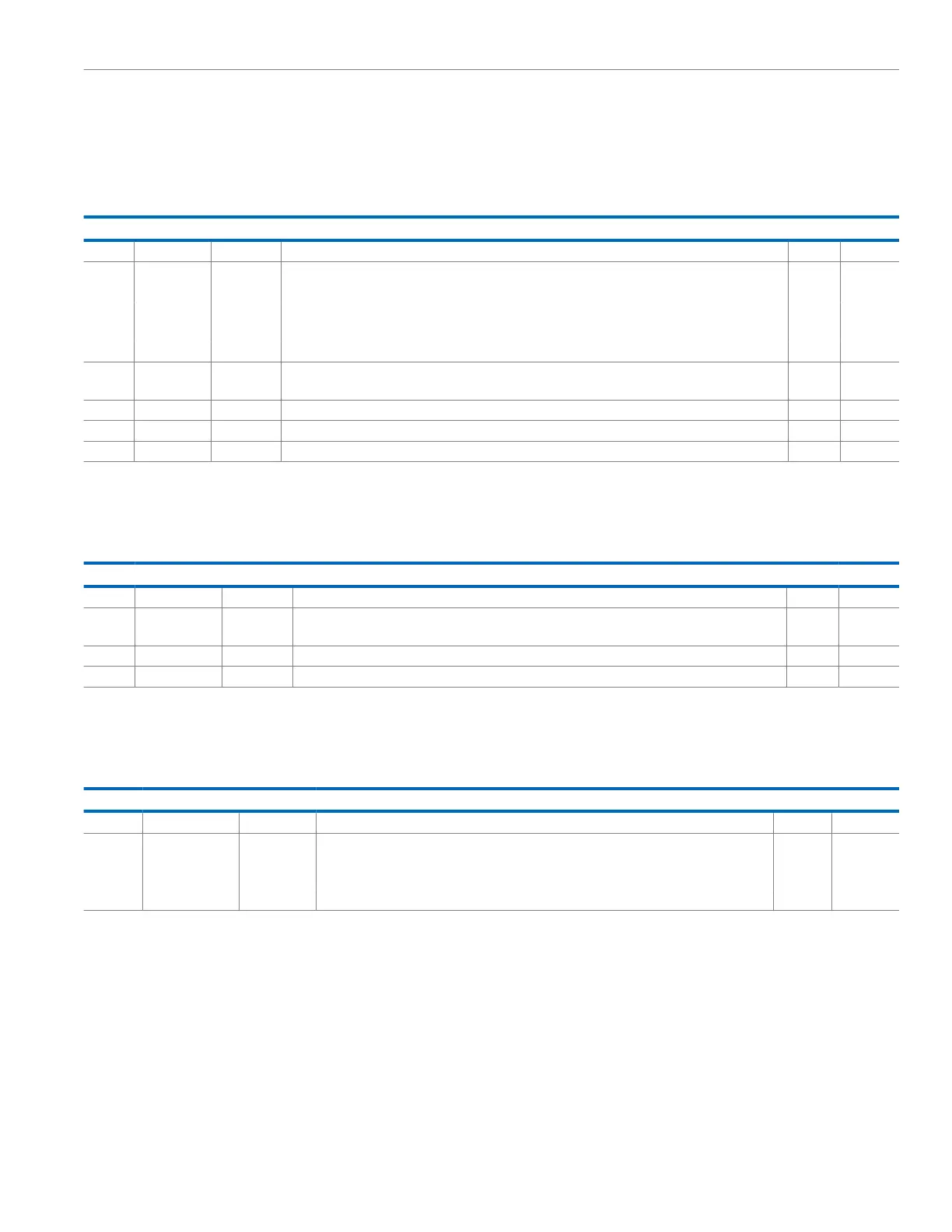

ANALOG DIE STATUS REGISTER

Address: 0x40007008, Reset: 0x0000, Name: AFEDIESTA

Table 39. Bit Descriptions for AFEDIESTA

Bits Bit Name Settings Description Reset Access

[15:1] Reserved Reserved. 0x0 R

0 AFEDIESTA Status of AFE to Digital Die Communication Status After a Reset Sequence. Always read this bit

after every reset.

0x0 R

0 Analog die trimming and calibration has been confirmed.

1 Analog die is not configured correctly and must not be used.

Loading...

Loading...