Reference Manual ADuCM356

REGISTER SUMMARY: SPI0/SPI1

analog.com Rev. A | 243 of 312

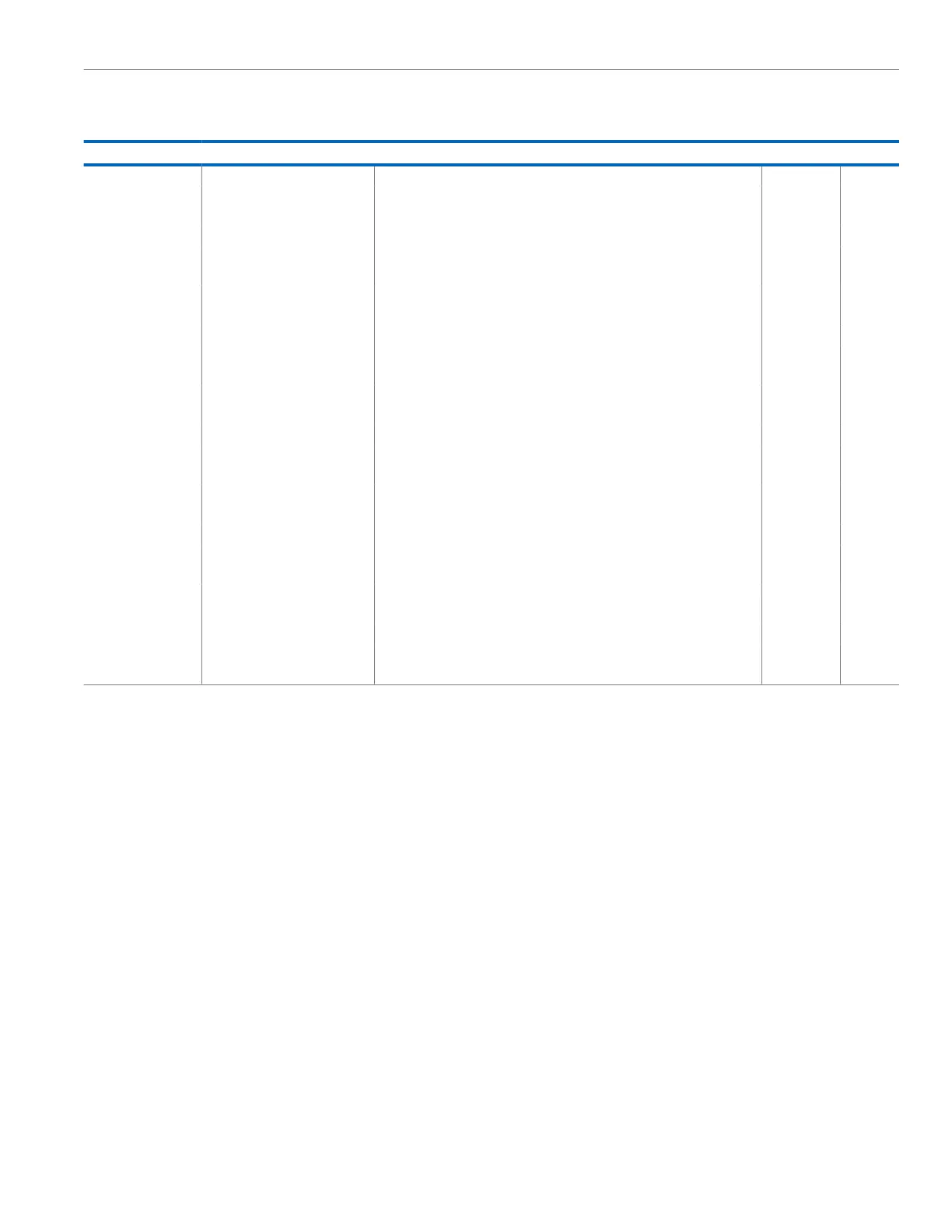

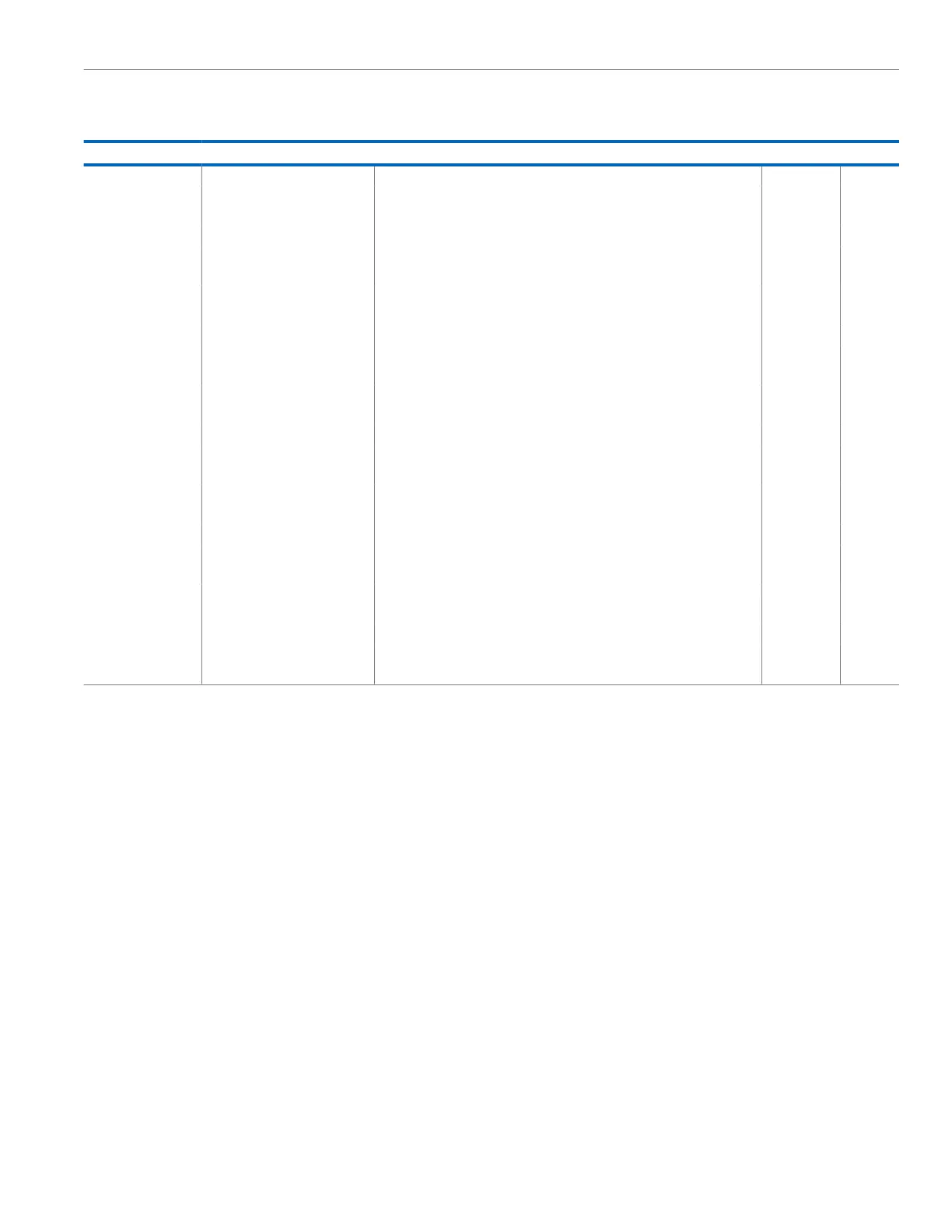

Table 305. SPI Register Summary

Address Name Description Reset Access

0x40004000 SPI0_STAT Status 0x0800 R

0x40004004 SPI0_RX Receive 0x0000 R

0x40004008 SPI0_TX Transmit 0x0000 W

0x4000400C SPI0_DIV Baud rate selection 0x0000 R/W

0x40004010 SPI0_CTL Configuration 0x0000 R/W

0x40004014 SPI0_IEN Interrupt configuration 0x0000 R/W

0x40004018 SPI0_CNT Transfer byte count 0x0000 R/W

0x4000401C SPI0_DMA DMA enable 0x0000 R/W

0x40004020 SPI0_FIFO_STAT FIFO status 0x0000 R

0x40004024 SPI0_RD_CTL Read control 0x0000 R/W

0x40004028 SPI0_FLOW_CTL Flow control 0x0000 R/W

0x4000402C SPI0_WAIT_TMR Wait timer for flow control 0x0000 R/W

0x40004034 SPI0_CS_OVERRIDE Chip select override 0x0000 R/W

0x40024000 SPI1_STAT Status 0x0800 R

0x40024004 SPI1_RX Receive 0x0000 R

0x40024008 SPI1_TX Transmit 0x0000 W

0x4002400C SPI1_DIV Baud rate selection 0x0000 R/W

0x40024010 SPI1_CTL Configuration 0x0000 R/W

0x40024014 SPI1_IEN Interrupt configuration 0x0000 R/W

0x40024018 SPI1_CNT Transfer byte count 0x0000 R/W

0x4002401C SPI1_DMA DMA enable 0x0000 R/W

0x40024020 SPI1_FIFO_STAT FIFO status 0x0000 R

0x40024024 SPI1_RD_CTL Read control 0x0000 R/W

0x40024028 SPI1_FLOW_CTL Flow control 0x0000 R/W

0x4002402C SPI1_WAIT_TMR Wait timer for flow control 0x0000 R/W

0x40024034 SPI1_CS_OVERRIDE Chip select override 0x0000 R/W

Loading...

Loading...