Reference Manual ADuCM356

REGISTER SUMMARY: DMA

analog.com Rev. A | 170 of 312

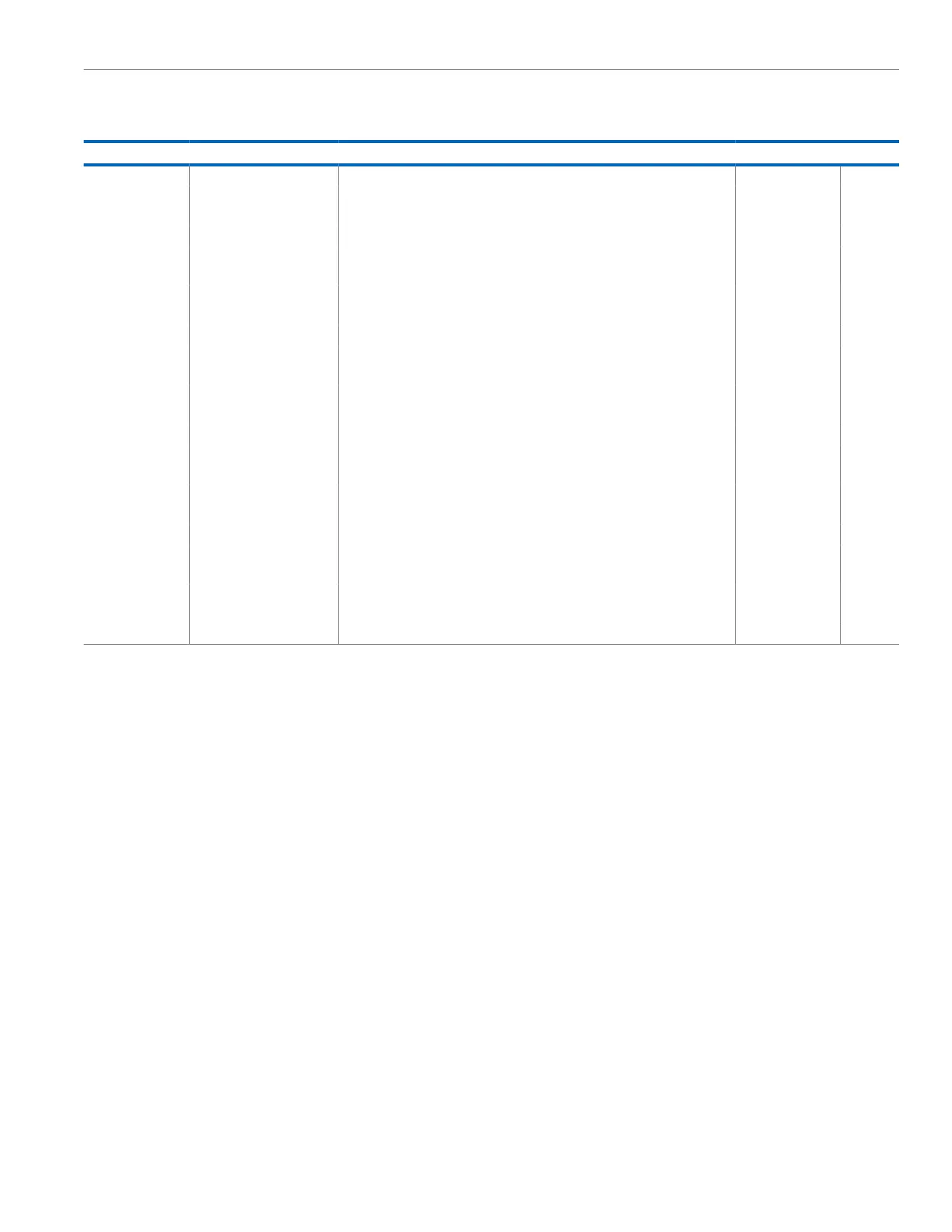

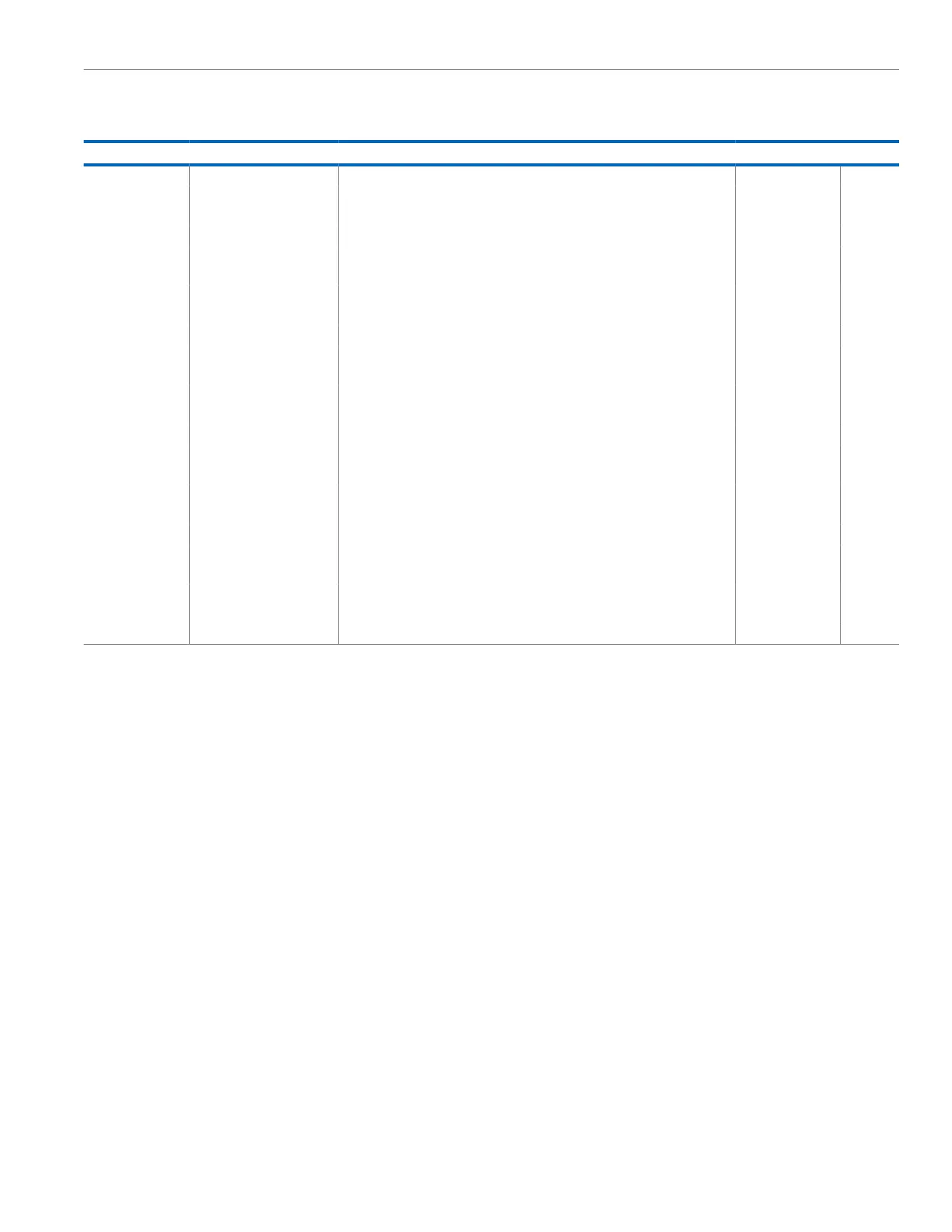

Table 196. DMA Register Summary

Address Name Description Reset Access

0x40010000 STAT Status 0x00180000 R

0x40010004 CFG Configuration 0x00000000 W

0x40010008 PDBPTR Channel primary control data base pointer 0x00000000 R/W

0x4001000C ADBPTR Channel alternate control data base pointer 0x00000200 R

0x40010014 SWREQ Channel software request 0x00000000 W

0x40010020 RMSK_SET Channel request mask set 0x00000000 R/W

0x40010024 RMSK_CLR Channel request mask clear 0x00000000 W

0x40010028 EN_SET Channel enable set 0x00000000 R/W

0x4001002C EN_CLR Channel enable clear 0x00000000 W

0x40010030 ALT_SET Channel primary alternate set 0x00000000 R/W

0x40010034 ALT_CLR Channel primary alternate clear 0x00000000 W

0x40010038 PRI_SET Channel priority set 0x00000000 W

0x4001003C PRI_CLR Channel priority clear 0x00000000 W

0x40010048 ERR_CLR Bus error clear 0x00000000 R/W

0x4001004C ERRCHNL_CLR Per channel bus error 0x00000000 R/W

0x40010050 INVALIDDESC_CLR Per channel invalid descriptor clear 0x00000000 R/W

0x40010800 BS_SET Channel bytes swap enable set 0x00000000 R/W

0x40010804 BS_CLR Channel bytes swap enable clear 0x00000000 W

0x40010810 SRCADDR_SET Channel source address decrement enable set 0x00000000 R/W

0x40010814 SRCADDR_CLR Channel source address decrement enable clear 0x00000000 W

0x40010818 DSTADDR_SET Channel destination address decrement enable set 0x00000000 R/W

0x4001081C DSTADDR_CLR Channel destination address decrement enable clear 0x00000000 W

0x400C2008 FIFO_CON FIFO configuration 0x00001010 R/W

0x400C206C DATAFIFORD Data FIFO read 0x00000000 R

Loading...

Loading...