Reference Manual ADuCM356

REGISTER DETAILS: FLASH CACHE CONTROLLER (FLCC)

analog.com Rev. A | 197 of 312

USER CONFIGURATION REGISTER

Address: 0x40018030, Reset: 0x00000000, Name: UCFG

User key is required. Write to this register to enable user control of DMA and autoincrement features. When user code has finished accessing

this register, write arbitrary data to the key register to reassert protection.

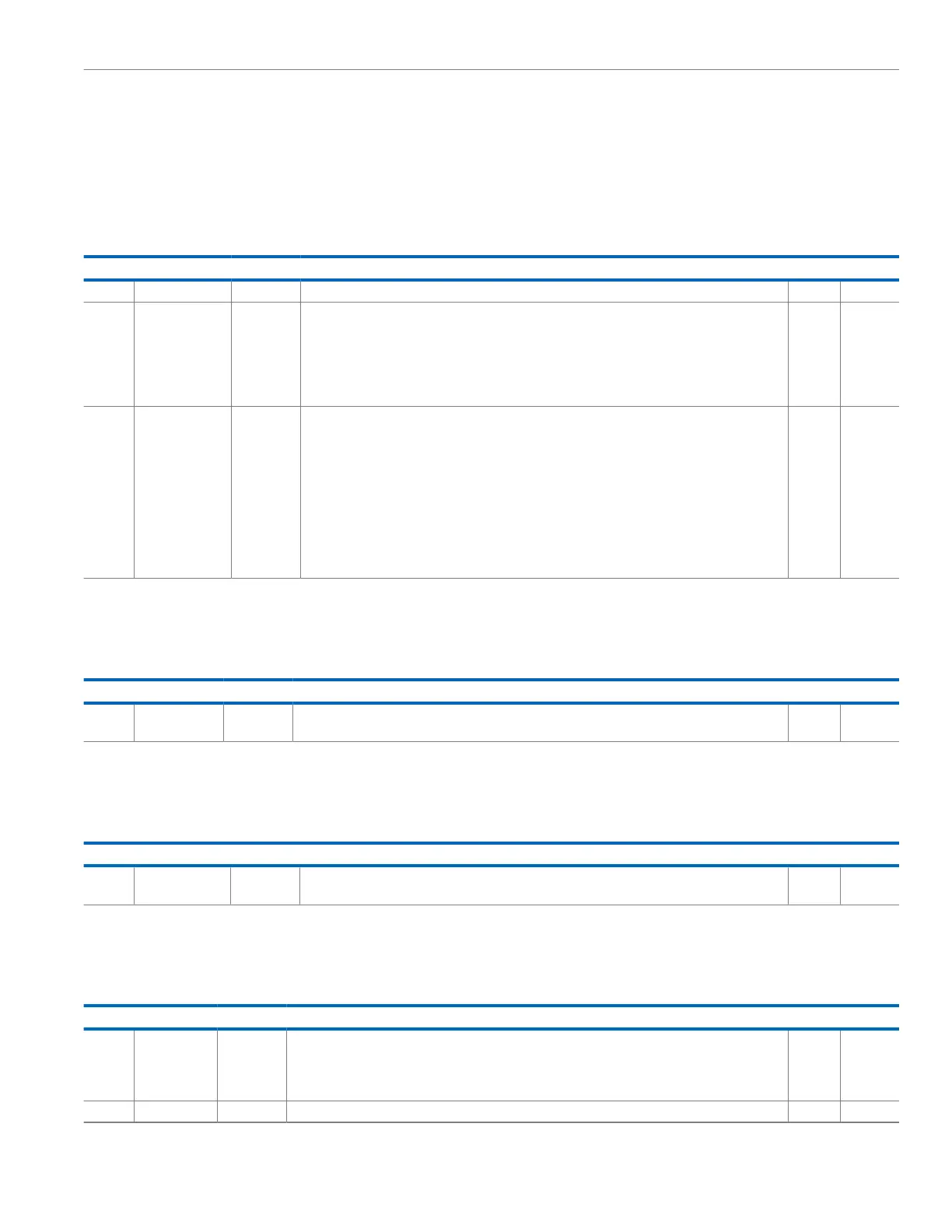

Table 236. Bit Descriptions for UCFG

Bits Bit Name Settings Description Reset Access

[31:2] Reserved Reserved. 0x0 R

1 AUTOINCEN Automatic Address Increment for Keyhole Access. When this bit is set, KH_ADDR automatically

increments by 0x8 during each write command or after each read command, enabling user code to

write a series of sequential flash locations without having to manually set the flash address for each

write. The KH_ADDR register is incremented, and can be observed by user code when STAT, Bit 5

is asserted during a write command or after a read command. When this bit is set, user code cannot

directly modify KH_ADDR.

0x0 R/W

0 KHDMAEN Keyhole DMA Enable. The flash controller interacts with the DMA controller when this bit is set.

Prior to setting this bit, write the starting address to the KH_ADDR register. Then configure the DMA

controller to write data to the KH_DATA1 register (address must be data word aligned), to always

write pairs of 32-bit words (R_POWER = 1), and to write an integer number of data pairs (for an

odd number of words, user code must write one word manually without the help of DMA). All DMA

writes automatically increment the target address (similar to the behavior of UCFG, Bit 1). The DMA

controller can only be used to write sequential addresses starting from the value of KH_ADDR. The

flash controller automatically begins write operations each time the DMA controller provides a pair

of words to write. Interaction with the DMA controller is designed to use burst writes, which can

significantly reduce overall programming time.

0x0 R/W

IRQ ABORT ENABLE (LOWER BITS) REGISTER

Address: 0x4001803C, Reset: 0x00000000, Name: ABORT_EN_LO

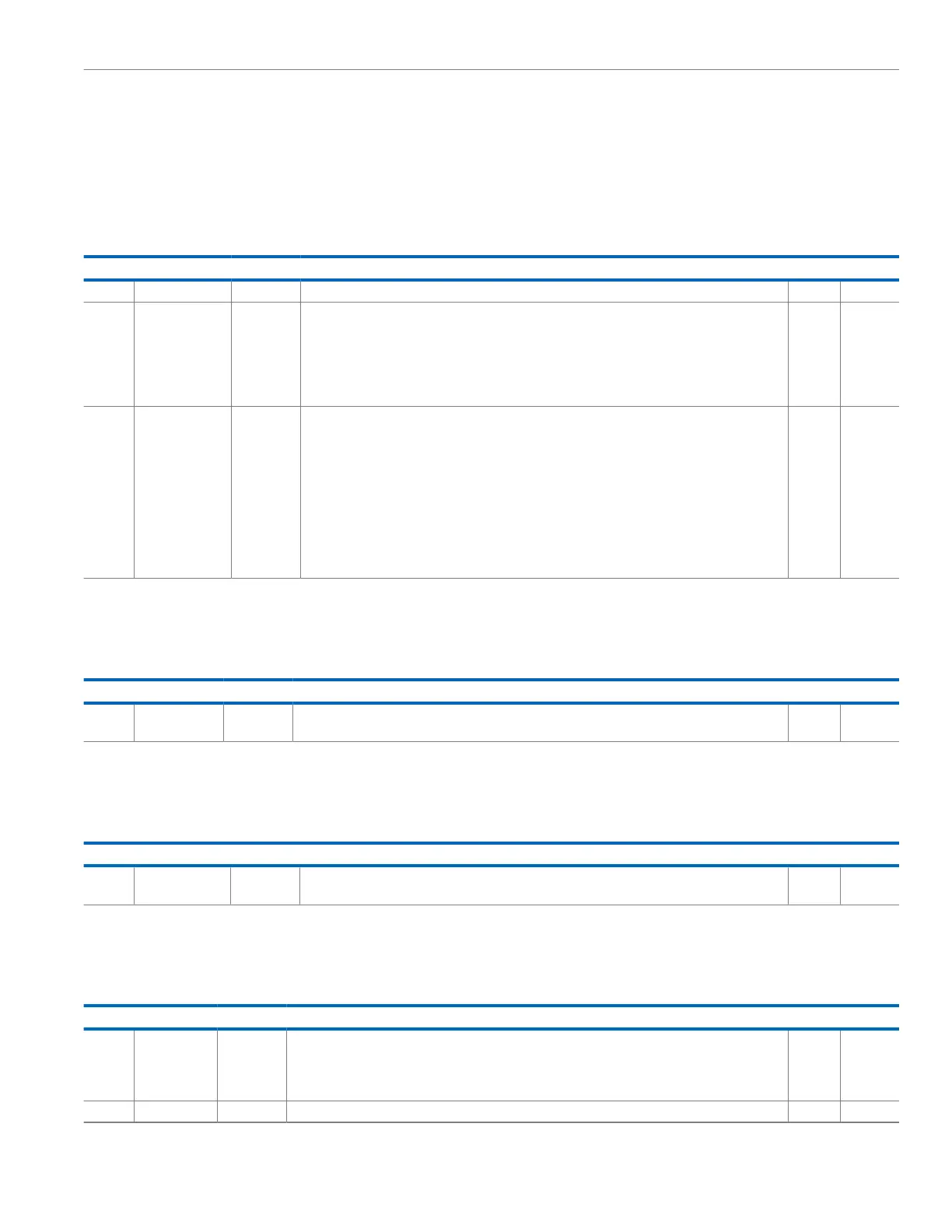

Table 237. Bit Descriptions for ABORT_EN_LO

Bits Bit Name Settings Description Reset Access

[31:0] VALUE[31:0] System IRQ Abort Enable. To allow a system interrupt to abort an ongoing flash command, write 1 to the

bit in this register corresponding with the desired system IRQ number.

0x0 R/W

IRQ ABORT ENABLE (UPPER BITS) REGISTER

Address: 0x40018040, Reset: 0x00000000, Name: ABORT_EN_HI

Table 238. Bit Descriptions for ABORT_EN_HI

Bits Bit Name Settings Description Reset Access

[31:0] VALUE[63:32] System IRQ Abort Enable. To allow a system interrupt to abort an ongoing flash command, write 1 to

the bit in this register corresponding with the desired system IRQ number.

0x0 R/W

ECC CONFIGURATION REGISTER

Address: 0x40018044, Reset: 0x00000002, Name: ECC_CFG

Table 239. Bit Descriptions for ECC_CFG

Bits Bit Name Settings Description Reset Access

[31:8] PTR ECC Start Page Pointer. Write Bits[31:8] of the start page address into Bits[31:8] of this register. This bit

is a byte address for any page in user flash. The bottom bits of this address are ignored by the flash

controller, forming a page address. When ECC is enabled and user code reads any address from within

the page specified, ECC functions are performed. Reads from less significant pages bypass ECC entirely.

0x0 R/W

[7:2] Reserved Reserved. 0x0 R

Loading...

Loading...