Reference Manual ADuCM356

REGISTER DETAILS: I

2

C

analog.com Rev. A | 232 of 312

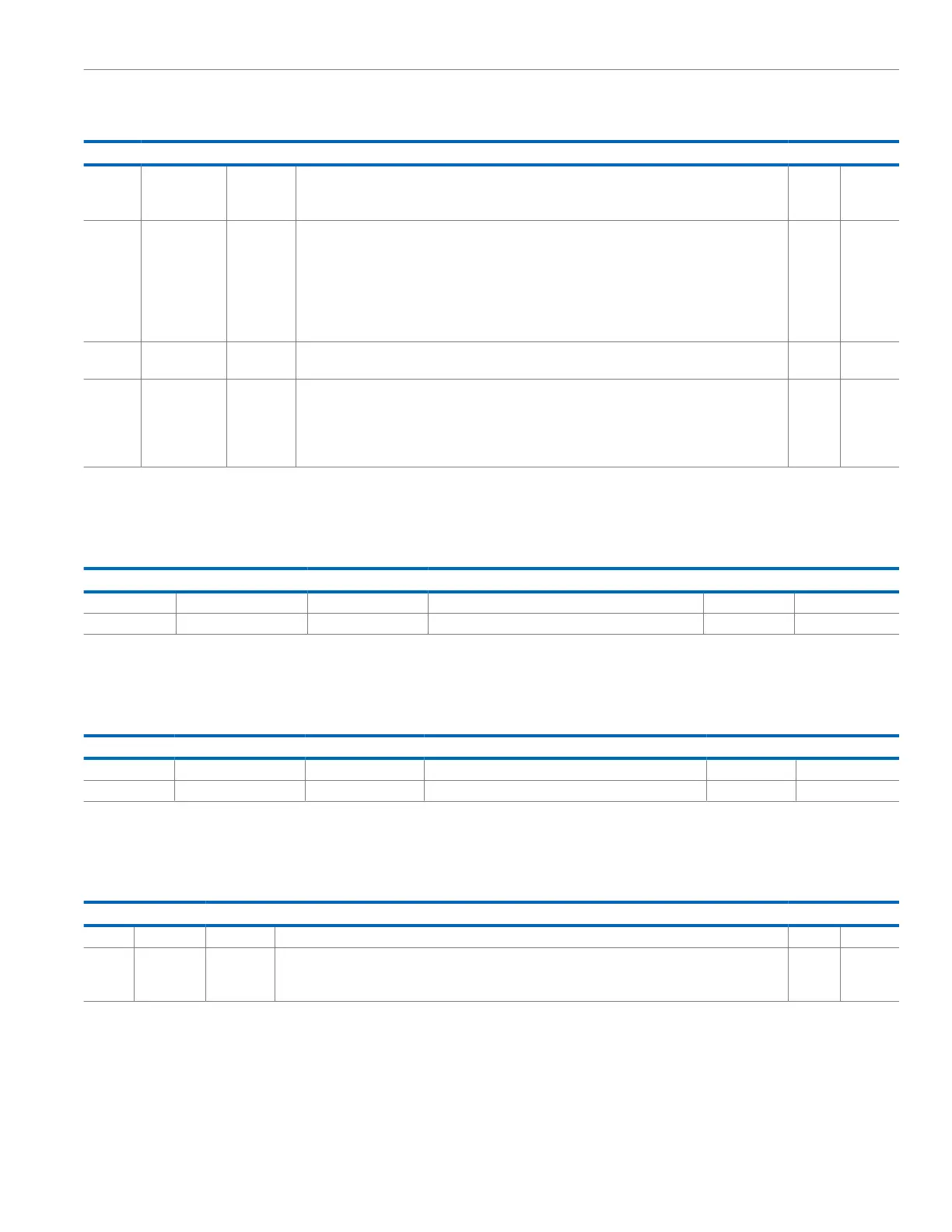

Table 293. Bit Descriptions for SSTAT (Continued)

Bits Bit Name Settings Description Reset Access

3 SRXREQ Target Receive Request. This bit asserts whenever the target receive FIFO is not empty. Read or flush

the target receive FIFO to clear this bit. This bit asserts on the falling edge of the I2C_SCL clock pulse

that clocks in the last data bit of a byte. This bit can drive an interrupt.

0x0 RC

2 STXREQ Target Transmit Request. If SCTL, Bit 5 = 0, this bit is set when the direction bit for a transfer is received

high. As long as the transmit FIFO is not full, this bit remains asserted. Initially, this bit is asserted on

the negative edge of the SCL pulse that clocks in the direction bit (if the device address matches). If

SCTL, Bit 5 = 1, this bit is set when the direction bit for a transfer is received high. As long as the

transmit FIFO is not full, this bit remains asserted. Initially, this bit is asserted after the positive edge of

the I2C_SCL pulse that clocks in the direction bit (if the device address matches). This bit is cleared on

a read of the SSTAT register.

0x0 RC

1 STXUR Target Transmit FIFO Underflow. This bit is set if an initiator requests data from the device, and the

transmit FIFO is empty for the rising edge of SCL.

0x0 RC

0 STXFSEREQ Target Transmit FIFO Status or Early Request. If SCTL, Bit 5 = 0, this bit is asserted whenever the

target transmit FIFO is empty. If SCTL, Bit 5 = 1, this bit is set when the direction bit for a transfer

is received high. This bit asserts on the positive edge of the I2C_SCL clock pulse that clocks in the

direction bit if the device address matches. This bit only asserts once for a transfer and is cleared when

read if SCTL, Bit 5 is asserted.

0x1 R/W

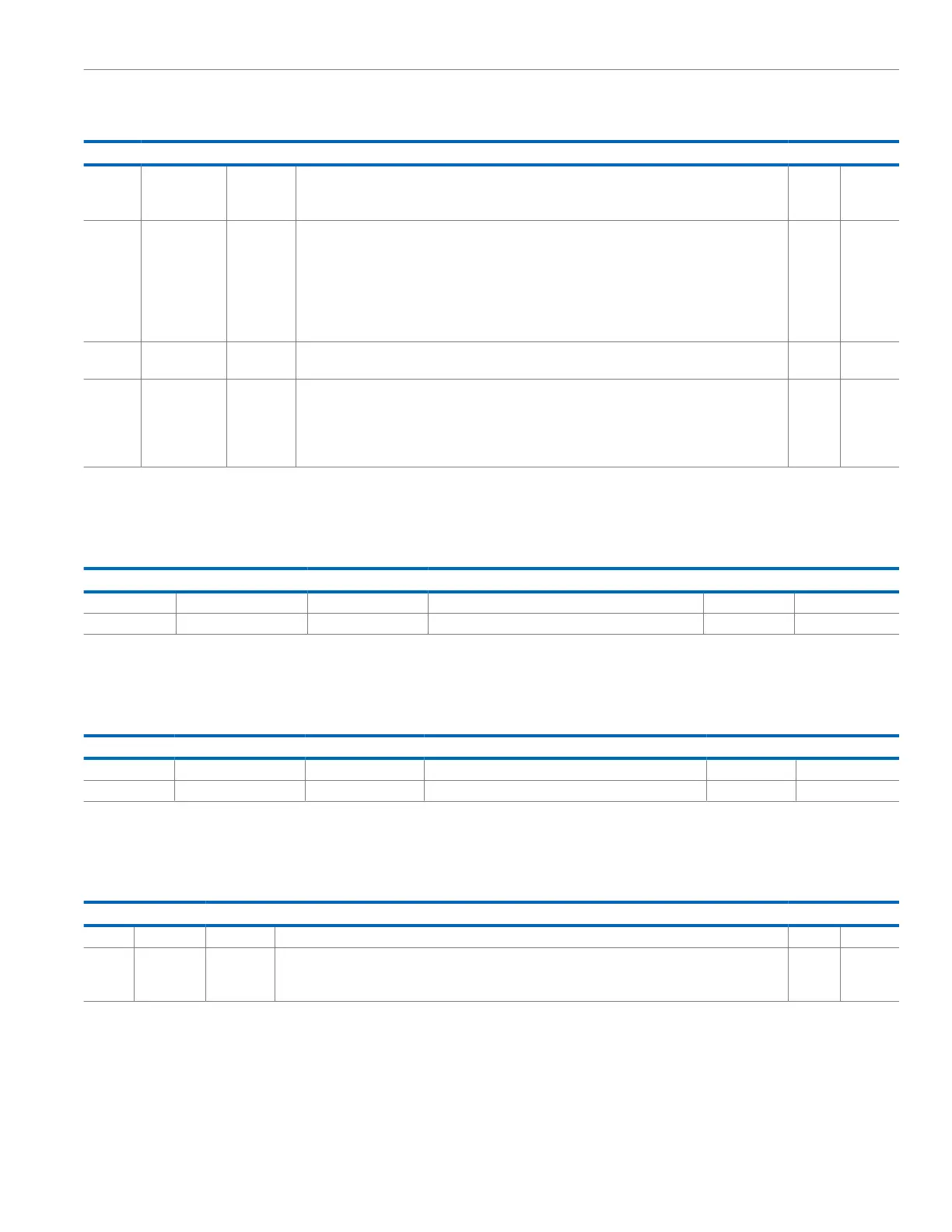

TARGET RECEIVE REGISTER

Address: 0x40003030, Reset: 0x0000, Name: SRX

Table 294. Bit Descriptions for SRX

Bits Bit Name Settings Description Reset Access

[15:8] Reserved Reserved. 0x0 R

[7:0] SRX Target Receive Register. 0x0 R

TARGET TRANSMIT REGISTER

Address: 0x40003034, Reset: 0x0000, Name: STX

Table 295. Bit Descriptions for STX

Bits Bit Name Settings Description Reset Access

[15:8] Reserved Reserved. 0x0 R

[7:0] ISTX Target Transmit Register. 0x0 R/W

HARDWARE GENERAL CALL ID REGISTER

Address: 0x40003038, Reset: 0x0000, Name: ALT

Table 296. Bit Descriptions for ALT

Bits Bit Name Settings Description Reset Access

[15:8] Reserved Reserved. 0x0 R

[7:0] ALT Target Alternative. This register is used in conjunction with SCTL, Bit 3 to match an initiator generating

a hardware general call. This register is used when an initiator device cannot be programmed with the

address of a target, and instead the target must recognize the address of the initiator.

0x0 R/W

FIRST TARGET ADDRESS DEVICE ID REGISTER

Address: 0x4000303C, Reset: 0x0000, Name: ID0

Loading...

Loading...