Reference Manual ADuCM356

REGISTER DETAILS: DIGITAL DIE WAKE-UP TIMER

analog.com Rev. A | 296 of 312

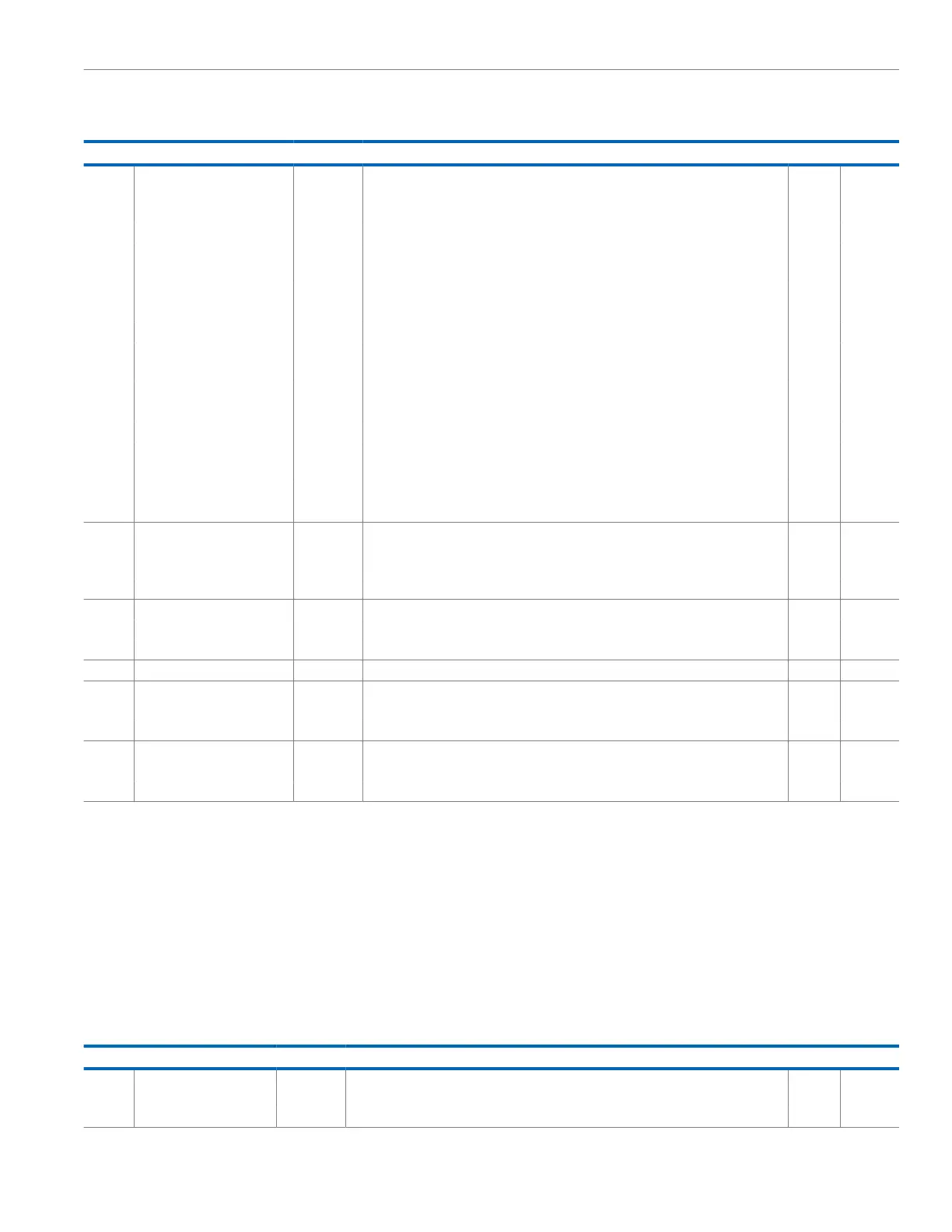

Table 388. Bit Descriptions for CR1 (Continued)

Bits Bit Name Settings Description Reset Access

MMRs. In contrast, RTC1 can prescale the clock by any power of two in the interval

Bits[15:0] to use as its time base.

0000 Prescale the WUT base clock by 2

0

= 1.

0001 Prescale the WUT base clock by 2

1

= 2.

0010 Prescale the WUT base clock by 2

2

= 4.

0011 Prescale the WUT base clock by 2

3

= 8.

0100 Prescale the WUT base clock by 2

4

= 16.

0101 Prescale the WUT base clock by 2

5

= 32.

0110 Prescale the WUT base clock by 2

6

= 64.

0111 Prescale the WUT base clock by 2

7

= 128.

1000 Prescale the WUT base clock by 2

8

= 256.

1001 Prescale the WUT base clock by 2

9

= 512.

1010 Prescale the WUT base clock by 2

10

= 1024.

1011 Prescale the WUT base clock by 2

11

= 2048.

1100 Prescale the WUT base clock by 2

12

= 4096.

1101 Prescale the WUT base clock by 2

13

= 8192.

1110 Prescale the WUT base clock by 2

14

= 16384.

1111 Prescale the WUT base clock by 2

15

= 32768.

4 CNTMOD60ROLLINTEN Enable for the WUT Modulo 60 Count Roll Over Interrupt Source, CNTMOD60ROLLINT

in SR2.

0x0 R/W

0 Disable CNTMOD60ROLLINT interrupt.

1 Enable CNTMOD60ROLLINT interrupt.

3 CNTROLLINTEN Enable CNTROLLINT in SR2 for the WUT Count Roll Over Interrupt Source. 0x0 R/W

0 Disable CNTROLLINT as an indicator of the WUT peripheral interrupt.

1 Enable CNTROLLINT as an indicator of the WUT peripheral interrupt.

2 Reserved Reserved. 0x0 R/W

1 PSINTEN Enable for the Prescaled Modulo 1 Interrupt Source PSINT in SR2. 0x0 R/W

0 Disable PSINT in SR2 as an indicator of the WUT peripheral interrupt.

1 Enable PSINT in SR2 as an indicator of the WUT peripheral interrupt.

0 CNTINTEN Enable for the WUT Count Interrupt Source, CNTINT in SR2. 0x0 R/W

0 Disable CNTINT in SR2 as an indicator of the WUT peripheral interrupt.

1 Enable CNTINT in SR2 as an indicator of the WUT peripheral interrupt.

STATUS 2 REGISTER

Address: 0x4000142C, Reset: 0xC000, Name: SR2

SR2 is a status register that further complements the status information provided by SR0 and SR1.

SR2 contains sticky interrupt sources optionally enabled via the CR1 register. These interrupt sources alert the CPU when the WUT count has

changed, when the prescaled gated clock that controls the advancement of the WUT count has activated, when a trim boundary has occurred,

when the 32-bit WUT count has rolled over, and when the modulo 60 version of the WUT count has rolled over.

All interrupt sources in SR2 are sticky, active high level signals. Each one can individually be cleared by writing a value of 0b1 to its bit position

in SR2.

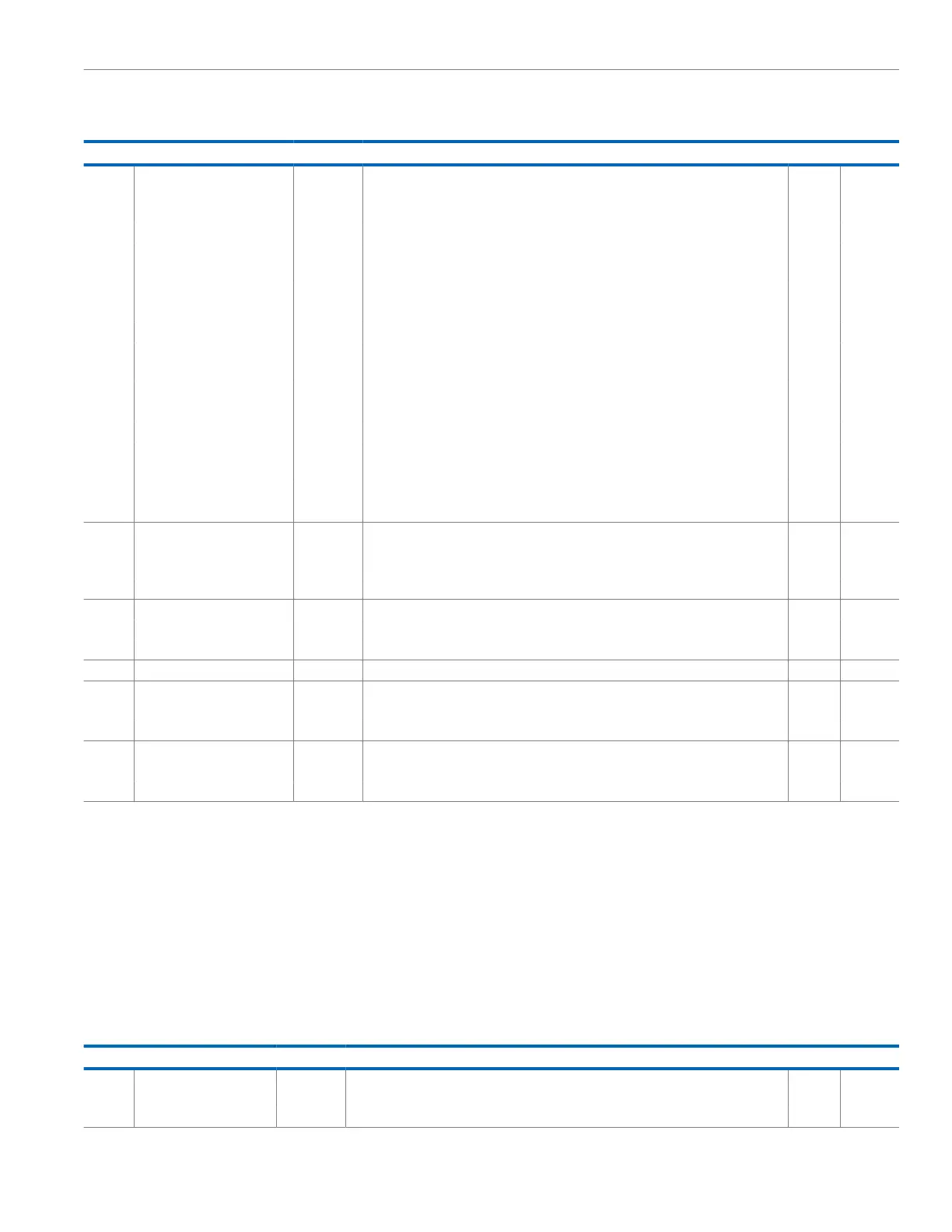

Table 389. Bit Descriptions for SR2

Bits Bit Name Settings Description Reset Access

15 WSYNCALM2MIR Synchronization Status of Posted Writes to ALM2. This bit indicates if the effects of a posted

write to ALM2 are visible to the CPU.

0x1 R

0 Results of a posted write to CR1 are not yet visible to the CPU.

Loading...

Loading...