Reference Manual ADuCM356

REGISTER DETAILS: UART

analog.com Rev. A | 257 of 312

TRANSMIT HOLDING REGISTER

Address: 0x40005000, Reset: 0x0000, Name: COMTX

COMRX and COMTX share the same address although they are implemented as different registers. If these registers are written to, the user

accesses the transmit holding register (COMTX). If these registers are read from, the user accesses the receive buffer register (COMRX).

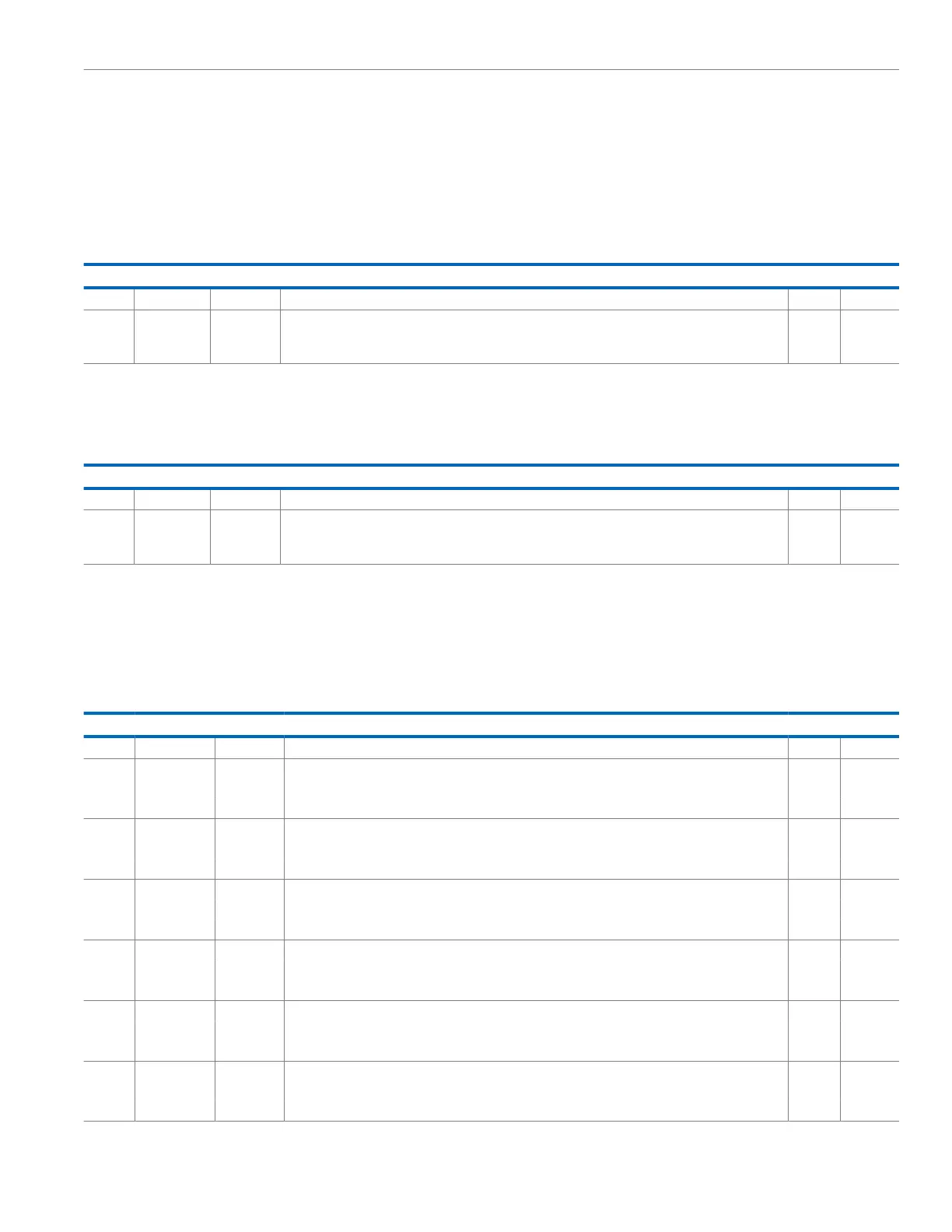

Table 321. Bit Descriptions for COMTX

Bits Bit Name Settings Description Reset Access

[15:8] Reserved Reserved. 0x0 R

[7:0] THR Transmit Holding Register. This is an 8-bit register to which the user can write the data to be sent. If

COMIEN, Bit 1 is set, an interrupt generates when COMTX is empty. If user code sets COMIEN, Bit 1 when

COMTX is already empty, an interrupt generates immediately.

0x0 W

RECEIVE BUFFER REGISTER

Address: 0x40005000, Reset: 0x0000, Name: COMRX

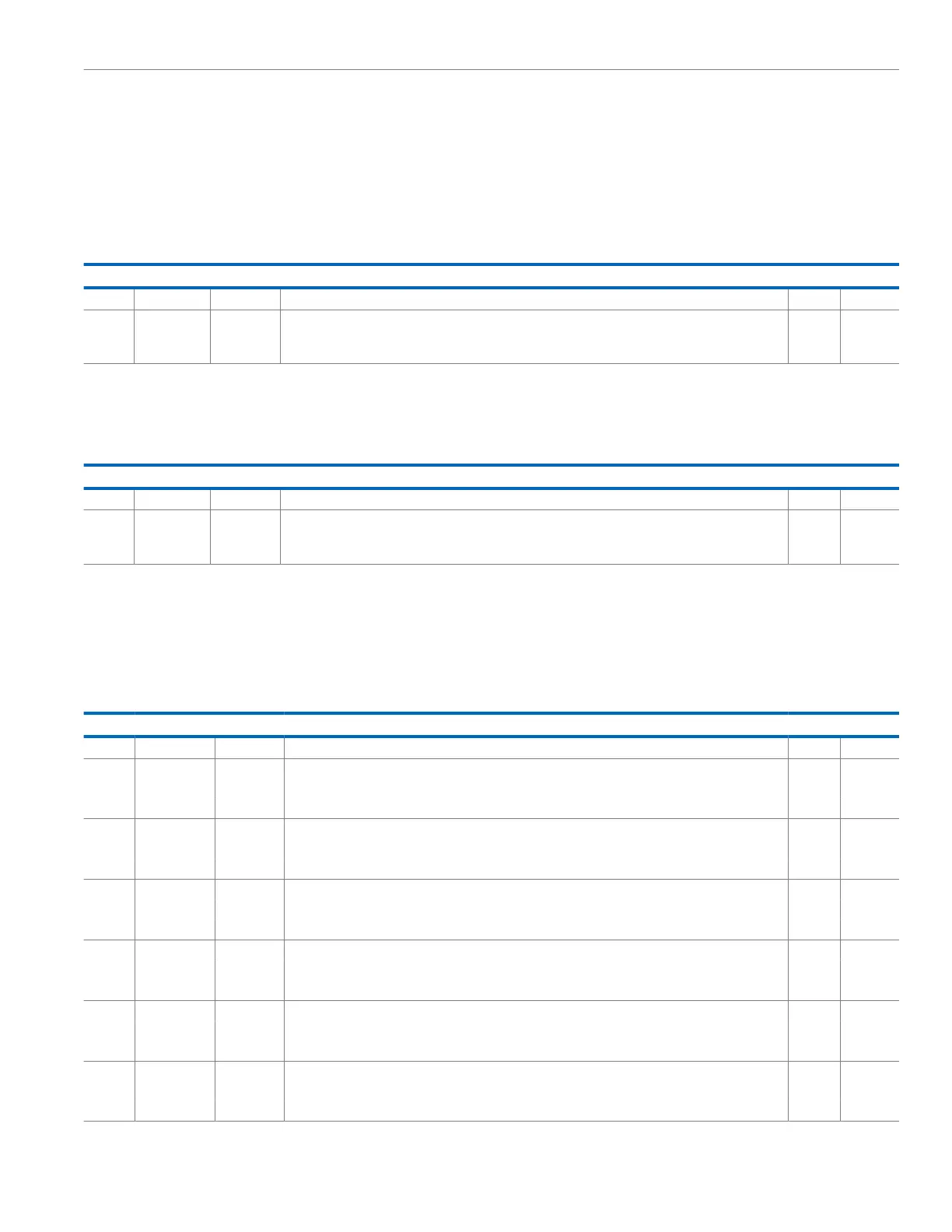

Table 322. Bit Descriptions for COMRX

Bits Bit Name Settings Description Reset Access

[15:8] Reserved Reserved. 0x0 R

[7:0] RBR Receive Buffer Register. This is an 8-bit register from which the user can read received data. If COMIEN,

Bit 0 is set, an interrupt generates when this register is fully loaded with the received data via the serial

input port. If user code sets the COMIEN, Bit 0 while COMRX is full, an interrupt generates immediately.

0x0 R

INTERRUPT ENABLE REGISTER

Address: 0x40005004, Reset: 0x0000, Name: COMIEN

COMIEN is the interrupt enable register that configures which interrupt source generates the interrupt. Only the lowest four bits in this register

enable interrupts. Bit 4 and Bit 5 enable UART DMA signals. The UART DMA channel and interrupt must be configured in the DMA block.

Table 323. Bit Descriptions for COMIEN

Bits Bit Name Settings Description Reset Access

[15:6] Reserved Reserved. 0x0 R

5 EDMAR DMA Requests in Receive Mode. 0x0 R/W

0 DMA requests disabled.

1 DMA requests enabled.

4 EDMAT DMA Requests in Transmit Mode. 0x0 R/W

0 DMA requests are disabled.

1 DMA requests are enabled.

3 EDSSI Modem Status Interrupt. Interrupt is generated when COMMSR, Bits[3:0] is set. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

2 ELSI Receive Status Interrupt. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

1 ETBEI Transmit Buffer Empty Interrupt. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

0 ERBFI Receive Buffer Full Interrupt. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

Loading...

Loading...