Reference Manual ADuCM356

DMA CONTROLLER

analog.com Rev. A | 161 of 312

DMA OPERATING MODES

The DMA controller has two buses, one connected to the system

bus shared with the Cortex-M3 core and the other connected to

16-bit peripherals. The DMA request can stop CPU access to the

system bus for several bus cycles, such as when the CPU and

DMA target the same destination (memory or peripheral). The DMA

controller fetches channel control data structures located in the

system memory to perform data transfers.

DMA capable peripherals, when enabled to use the DMA, can

request the DMA controller for a transfer. At the end of the program-

med number of DMA transfers for a channel, the DMA controller

generates a single cycle DMA_DONE interrupt corresponding to

that channel. The DMA_DONE interrupt indicates the completion of

the DMA transfer. Separate interrupt enable bits are available in the

NVIC for each of the DMA channels.

CHANNEL CONTROL DATA STRUCTURE

Every channel has two associated control data structures: primary

and alternate. For simple transfer modes, the DMA controller uses

either the primary or the alternate data structure. For more complex

data transfer modes, such as ping pong or scatter gather, the DMA

controller uses both the primary and alternate data structures. Both

control data structures occupy four 32-bit locations in the memory,

as detailed in Table 189. The entire channel control data structure is

described in Table 190.

Before the controller can perform a DMA transfer, the data structure

related to the DMA channel must be programmed at the designated

location in system memory, SRAM. The programming determines

the source and destination data size, number of transfers, and the

number of arbitrations. The contents of the designated memory

locations are as follows:

► The source end pointer memory location contains the end ad-

dress of the source data.

► The destination end pointer memory location contains the end

address of the destination data.

► The control data configuration memory location contains the

channel configuration control data.

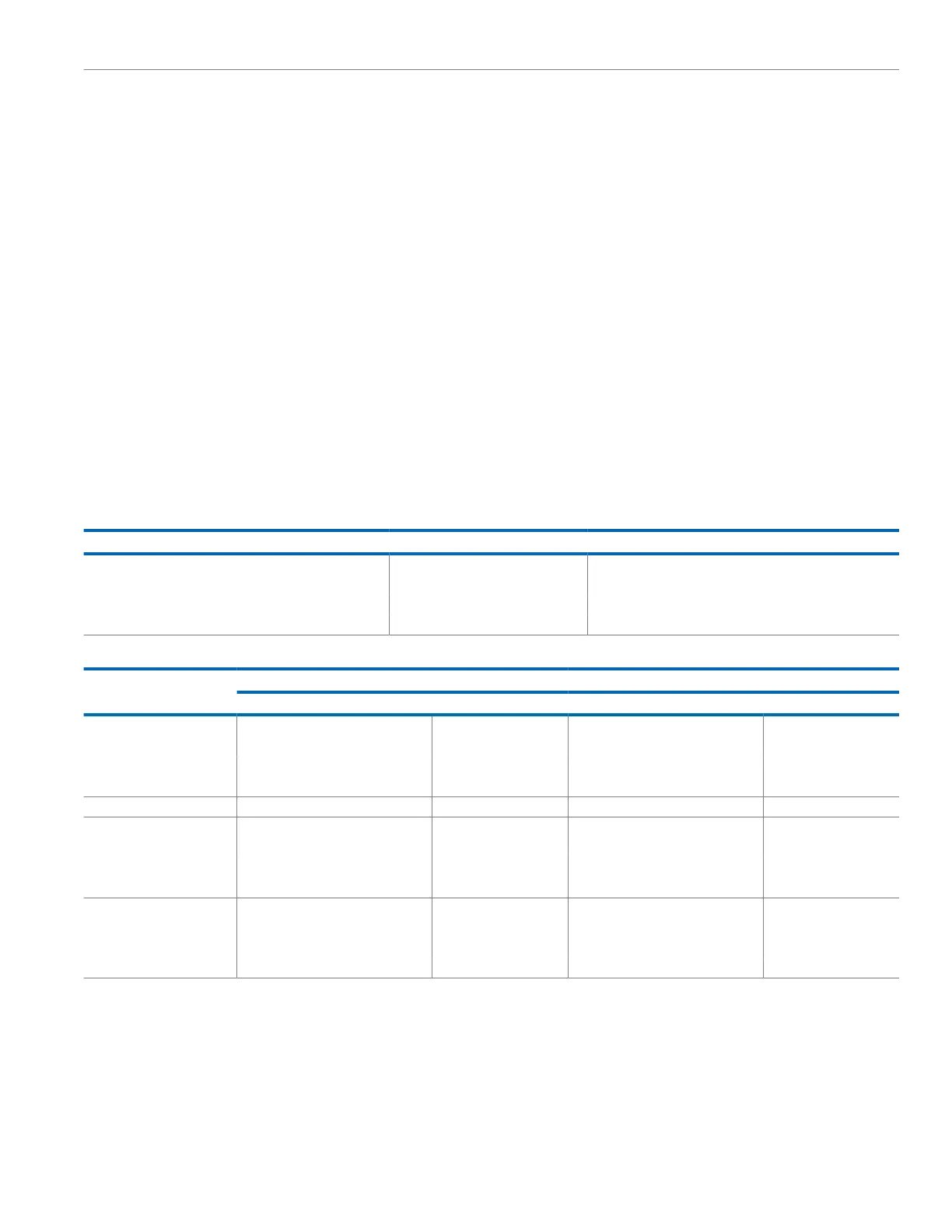

Table 189. Channel Control Data Structure

Offset Address Offset Register Name Description

0x00 SRC_END_PTR Source end pointer

0x04 DST_END_PTR Destination end pointer

0x08 CHNL_CFG Control data configuration

0x0C Reserved Reserved

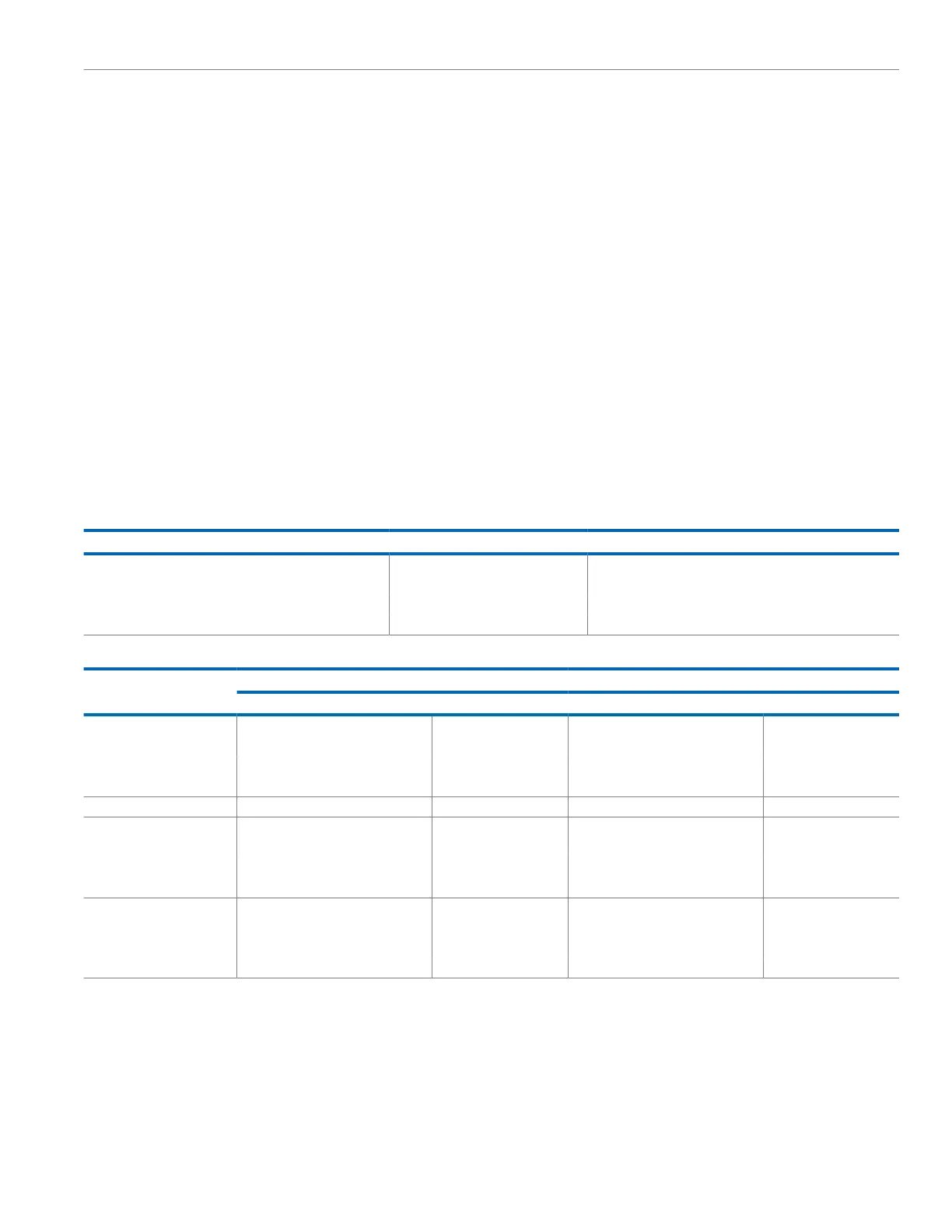

Table 190. Memory Map of Primary and Alternate DMA Structures

1

Channel Number

Primary Structures Alternate Structures

Register Description Offset Address Register Description Offset Address

Channel 23 Reserved, set to 0 0x17C Reserved, set to 0 0x1DC

Control 0x178 Control 0x1D8

Destination end pointer 0x174 Destination end pointer 0x1D4

Source end pointer 0x170 Source end pointer 0x1D0

… … … … …

Channel 1 Reserved, set to 0 0x01C Reserved, set to 0 0x11C

Control 0x018 Control 0x118

Destination end pointer 0x014 Destination end pointer 0x114

Source end pointer 0x010 Source end pointer 0x110

Channel 0 Reserved, set to 0 0x00C Reserved, set to 0 0x10C

Control 0x008 Control 0x108

Destination end pointer 0x004 Destination end pointer 0x104

Source end pointer 0x000 Source end pointer 0x100

1

The row with ellipses (…) indicates all channels between Channel 23 and Channel 1. These channels follow the same register naming contentions and offset address

pattern.

The user must define the DMA structures in their source code, as

shown in the Example Code: Define DMA Structures section. After

the structure has been defined, its start address must be assigned

to the DMA base address pointer register, PDBPTR. Each register

for each DMA channel is then at the offset address (as specified in

Table 190) plus the value in the PDBPTR register.

When the DMA controller receives a request for a channel, it reads

the corresponding data structure from the system memory into its

internal cache. Any update to the descriptor in the system memory

Loading...

Loading...