Reference Manual ADuCM356

REGISTER SUMMARY: CLOCK ARCHITECTURE

analog.com Rev. A | 15 of 312

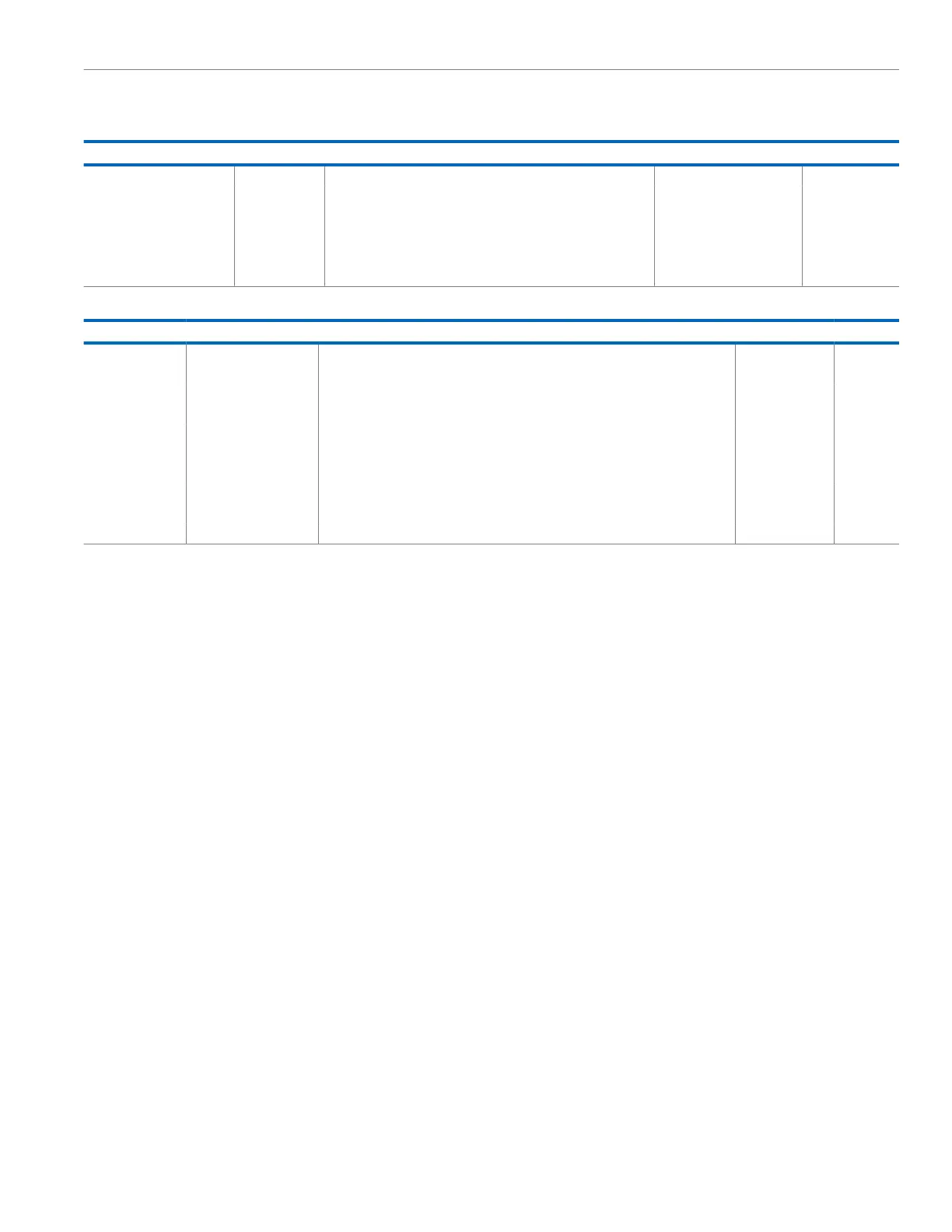

Table 3. Digital Die System Clock Register Summary (CLKG0_CLK Stack)

Address Name Description Reset Access

0x4004C10C KEY Key protection for CTL register 0x00000000 R/W

0x4004C110 CTL Oscillator control 0x00000302 R/W

0x4004C300 CTL0 Clock Control 0 0x00000078 R/W

0x4004C304 CTL1 Clock dividers 0x00100404 R/W

0x4004C314 CTL5 User clock gating control 0x0000001F R/W

0x4004C318 STAT0 Clocking status 0x00000000 R/W

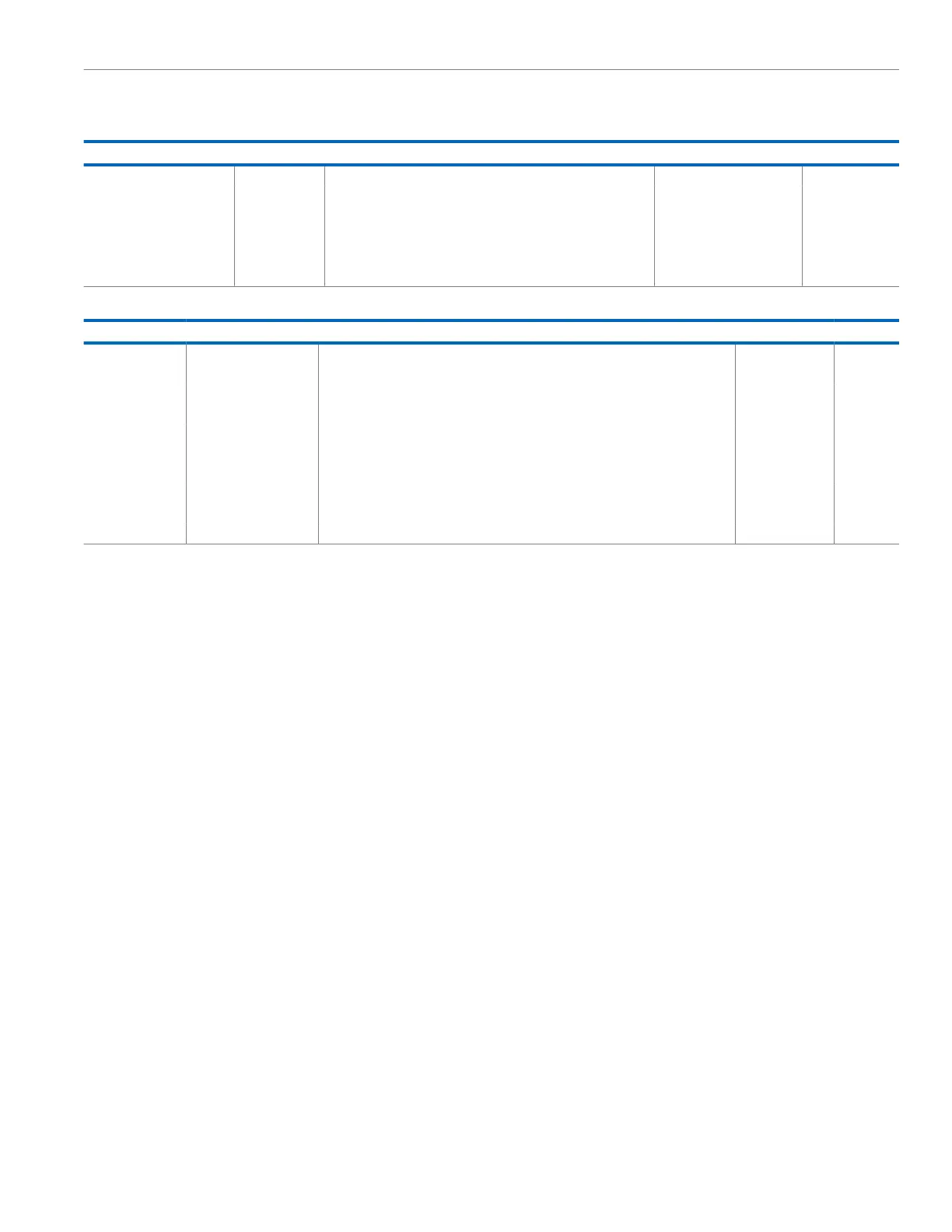

Table 4. Analog Die Clock Register Summary (AFECON Stack)

Address Name Description Reset Access

0x400C0408 CLKCON0 Clock divider configuration 0x0441 R/W

0x400C0410 CLKEN1 Clock gate enable 0x010A R/W

0x400C0414 CLKSEL Clock select 0x0000 R/W

0x400C041C GPIOCLKMUXSEL GPIO clock mux select to GPIO1 pin 0x0000 R/W

0x400C0420 CLKCON0KEY Key protection for CLKCON0 0x0000 R/W

0x400C0A70 CLKEN0 Clock control of low-power TIA chop, watchdog, and wake-up timers 0x0000 R/W

0x400C0A0C OSCKEY Key protection for OSCCON 0x0000 R/W

0x400C0A10 OSCCON Oscillator control 0x0303 R/W

0x400C20BC HPOSCCON High-power oscillator configuration 0x00000024 R/W

0x400C22F0 PMBW Power mode configuration register 0x00000000 R/W

Loading...

Loading...