Reference Manual ADuCM356

REGISTER DETAILS: ADC CIRCUIT

analog.com Rev. A | 71 of 312

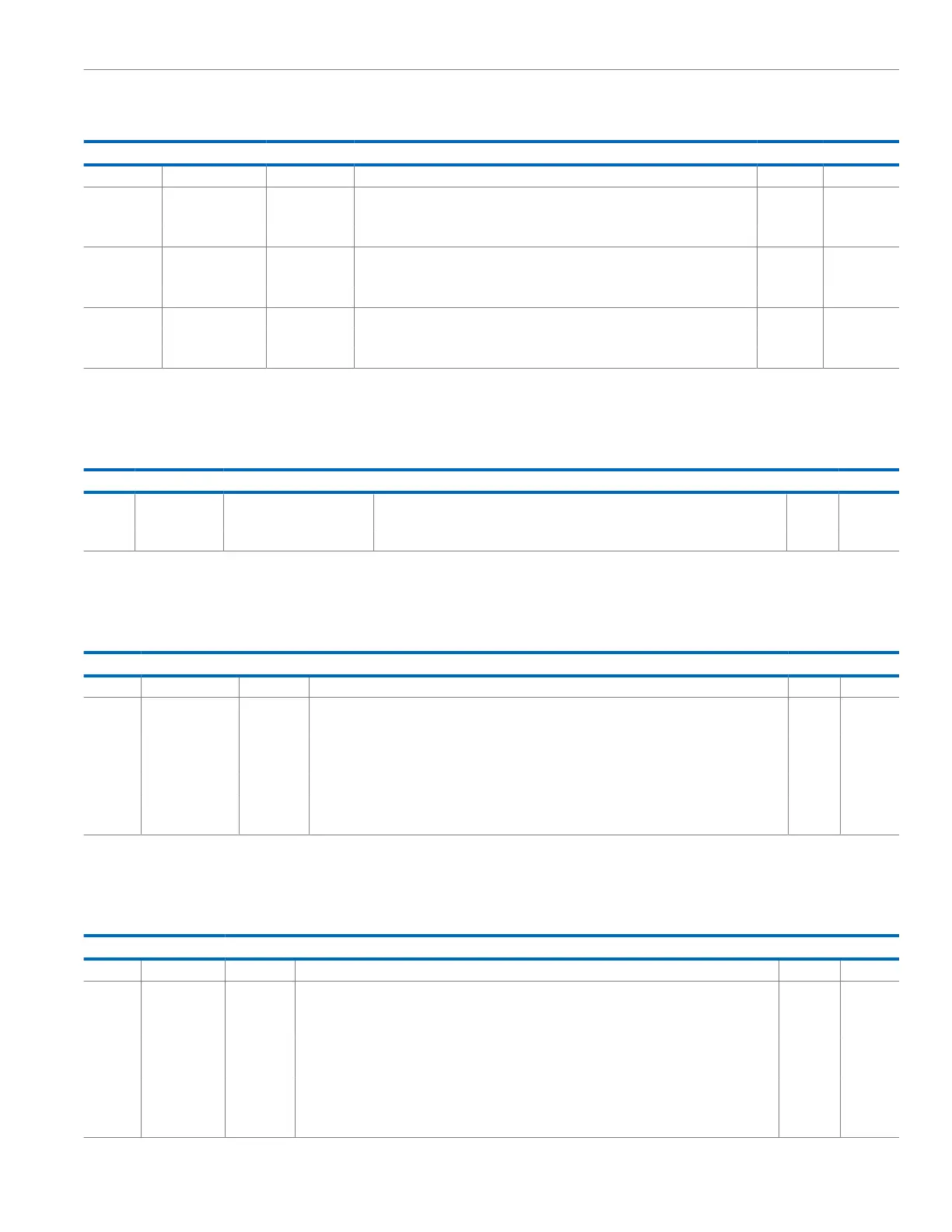

Table 76. Bit Descriptions for ADCBUFCON (Continued)

Bits Bit Name Settings Description Reset Access

1 Disable chop.

2 CHOPDIS Configure ADC Buffer Chop. 0x0 R/W

0 Enable chop.

1 Disable chop.

1 CHOPDIS Configure PGA Chop. 0x0 R/W

0 Enable chop.

1 Disable chop.

0 Configure Front-End Buffer Chop.

0 Enable chop.

1 Disable chop.

CALIBRATION LOCK REGISTER

Address: 0x400C2230, Reset: 0x00000000, Name: CALDATLOCK

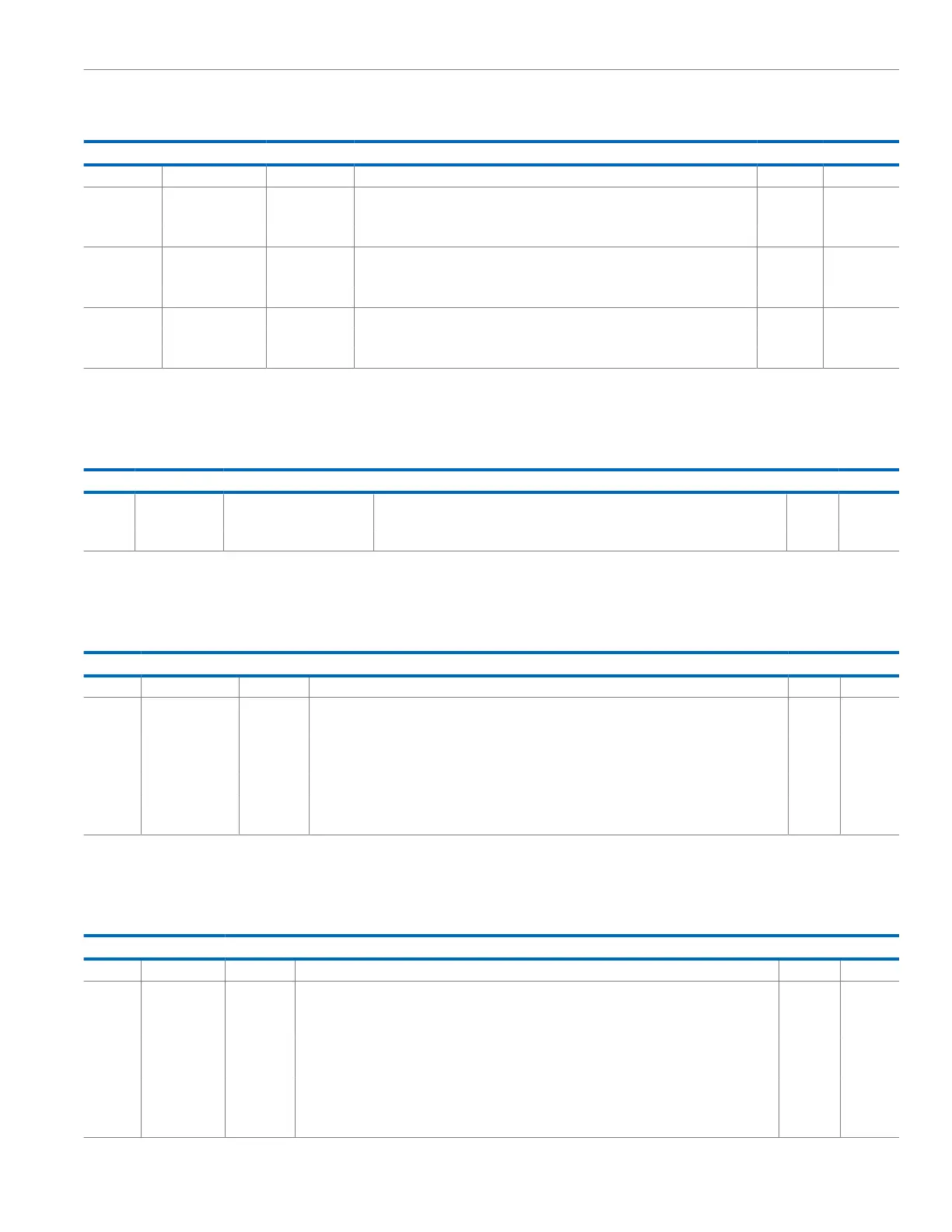

Table 77. Bit Descriptions for CALDATLOCK

Bits Bit Name Settings Description Reset Access

[31:0] KEY Password for Calibration Data Registers. Prevents overwriting of data after the

calibration phase.

0x0 R/W

0xDE87A5AF Calibration data registers read/write.

OFFSET CALIBRATION LOW-POWER TIA0 CHANNEL REGISTER

Address: 0x400C2288, Reset: 0x00000000, Name: ADCOFFSETLPTIA0

Table 78. Bit Descriptions for ADCOFFSETLPTIA0

Bits Bit Name Settings Description Reset Access

[31:15] Reserved Reserved. 0x0 R

[14:0] VALUE Offset Calibration for Low-Power TIA0. Represented as a twos complement number. The calibration

resolution is 0.25 LSBs of the ADCDAT LSB size.

0x0 R/W

0x3FFF 4095.75 (maximum positive offset calibration value).

0x0001 0.25 (minimum positive offset calibration value).

0x0000 0 (no offset adjustment).

0x7FFF −0.25 (minimum negative offset calibration value).

0x4000 −4096.0 (maximum negative offset calibration value).

GAIN CALIBRATION FOR LOW-POWER TIA0 CHANNEL REGISTER

Address: 0x400C228C, Reset: 0x00004000, Name: ADCGNLPTIA0

Table 79. Bit Descriptions for ADCGNLPTIA0

Bits Bit Name Settings Description Reset Access

[31:15] Reserved Reserved. 0x0 R

[14:0] VALUE Gain Error Calibration for Low-Power TIA0. ADC offset correction in TIA measurement mode,

represented as a twos complement number.

0x4000 R/W

0x7FFF 2 (maximum positive gain adjustment).

0x4001 1.000061 (minimum positive gain adjustment).

0x4000 1.0. ADC result multiplied by 1. No gain adjustment. Default value.

0x3FFF 0.999939 (minimum negative gain adjustment).

0x2000 0.5. ADC result multiplied by 0.5.

0x0001 0.000061 (maximum negative gain adjustment).

Loading...

Loading...