Reference Manual ADuCM356

REGISTER DETAILS: CRC

analog.com Rev. A | 309 of 312

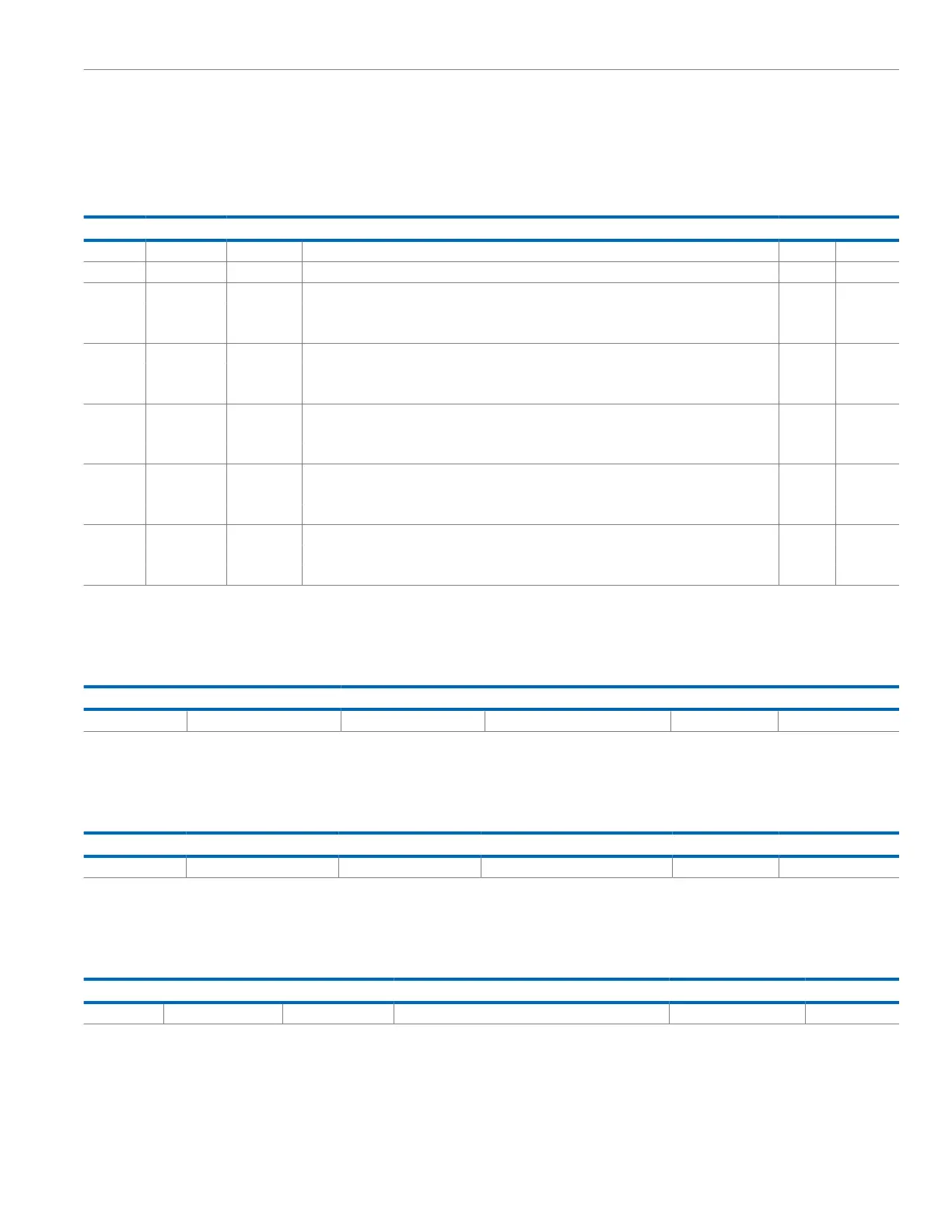

CRC CONTROL REGISTER

Address: 0x40040000, Reset: 0x10000000, Name: CTL

Table 405. Bit Descriptions for CTL

Bits Bit Name Settings Description Reset Access

[31:28] REVID Revision ID. 0x1 R

[27:5] Reserved Reserved. 0x0 R

4 W16SWP Word 16 Swap. This bit swaps 16-bit half words within a 32-bit word. 0x0 R/W

0 Word 16 swap disabled.

1 Word 16 swap enabled.

3 BYTMIRR Byte Mirroring. This bit swaps 8-bit bytes within each 16-bit half word. 0x0 R/W

0 Byte mirroring is disabled.

1 Byte Mirroring is enabled.

2 BITMIRR Bit Mirroring. This bit swaps bits within each byte. 0x0 R/W

0 Bit mirroring is disabled.

1 Bit mirroring is enabled.

1 LSBFIRST LSB First Calculation Order. 0x0 R/W

0 MSB first CRC calculation.

1 LSB first CRC calculation.

0 EN CRC Peripheral Enable. 0x0 R/W

0 CRC peripheral is disabled.

1 CRC peripheral is enabled.

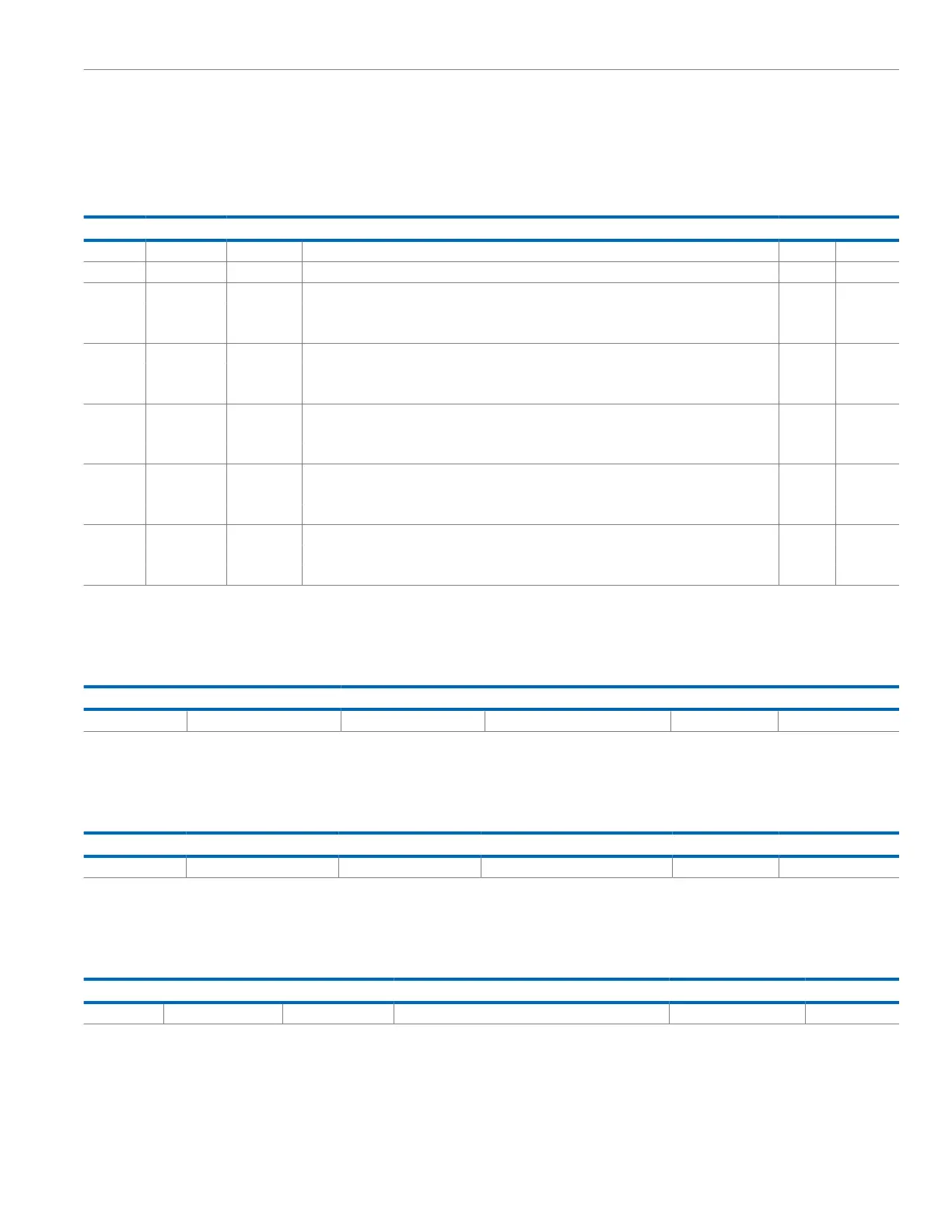

INPUT DATA WORD REGISTER

Address: 0x40040004, Reset: 0x00000000, Name: IPDATA

Table 406. Bit Descriptions for IPDATA

Bits Bit Name Settings Description Reset Access

[31:0] VALUE Data Input. 0x0 W

CRC RESULT REGISTER

Address: 0x40040008, Reset: 0x00000000, Name: RESULT

Table 407. Bit Descriptions for RESULT

Bits Bit Name Settings Description Reset Access

[31:0] VALUE CRC Reset. 0x0 R/W

PROGRAMMABLE CRC POLYNOMIAL REGISTER

Address: 0x4004000C, Reset: 0x04C11DB7, Name: POLY

Table 408. Bit Descriptions for POLY

Bits Bit Name Settings Description Reset Access

[31:0] VALUE CRC Reduction Polynomial. 0x4C11DB7 R/W

INPUT DATA BITS REGISTER

Address: 0x40040010 to 0x40040017 (Increments of 0x01), Reset: 0x00, Name: IPBITSN

Loading...

Loading...