Reference Manual ADuCM356

REGISTER DETAILS: DIGITAL INPUTS AND OUTPUTS

analog.com Rev. A | 217 of 312

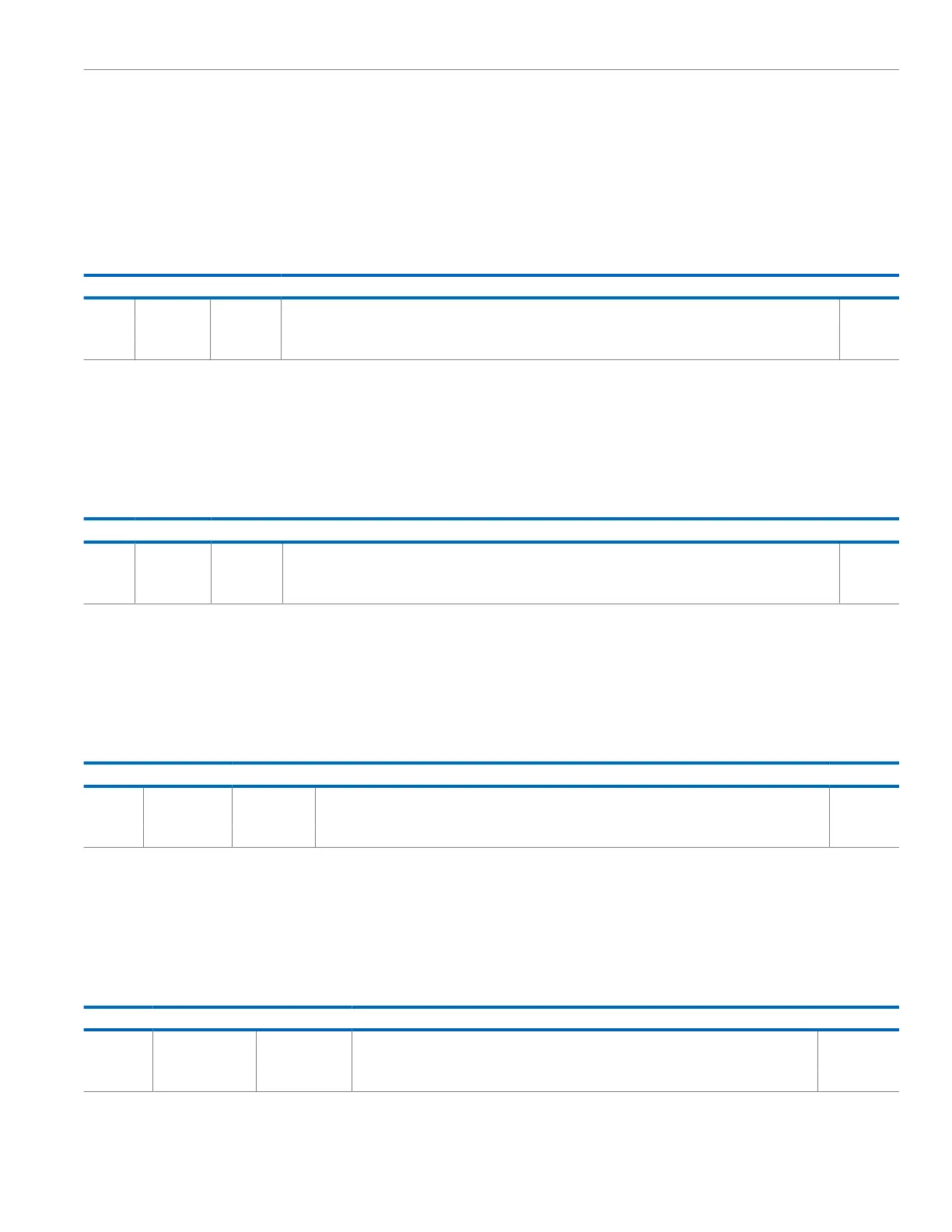

GPIO PORT DATA OUTPUT CLEAR REGISTERS

Address: 0x4002001C, Reset: 0x0000, Name: GP0CLR

Address: 0x4002005C, Reset: 0x0000, Name: GP1CLR

Address: 0x4002009C, Reset: 0x0000, Name: GP2CLR

Table 266. Bit Descriptions for GP0CLR, GP1CLR, GP2CLR

Bits Bit Name Settings Description Access

[15:0] CLR Data Out Clear. Set the output low. Do not use the bit band alias addresses for this register. W

0 Clearing this bit has no effect.

1 Each bit is set to drive the corresponding GPIO pin low.

GPIO PORT PIN TOGGLE REGISTERS

Address: 0x40020020, Reset: 0x0000, Name: GP0TGL

Address: 0x40020060, Reset: 0x0000, Name: GP1TGL

Address: 0x400200A0, Reset: 0x0000, Name: GP2TGL

Table 267. Bit Descriptions for GP0TGL, GP1TGL, GP2TGL

Bits Bit Name Settings Description Access

[15:0] TGL Toggle the Output of the Port Pin. Do not use the bit band alias addresses for this register. W

0 Clearing this bit has no effect.

1 Set by user code to invert the corresponding GPIO pin.

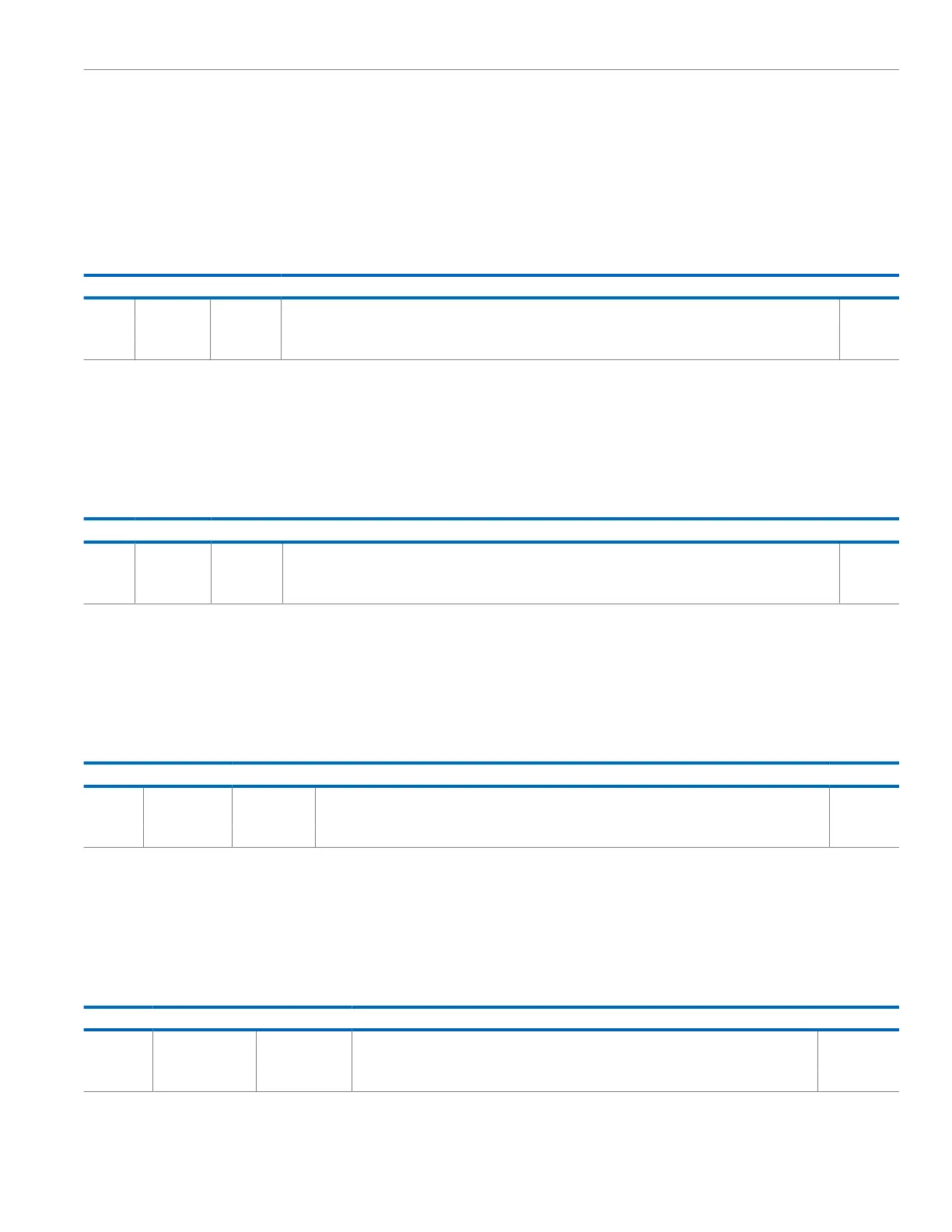

GPIO PORT INTERRUPT POLARITY REGISTERS

Address: 0x40020024, Reset: 0x0000, Name: GP0POL

Address: 0x40020064, Reset: 0x0000, Name: GP1POL

Address: 0x400200A4, Reset: 0x0000, Name: GP2POL

Table 268. Bit Descriptions for GP0POL, GP1POL, GP2POL

Bits Bit Name Settings Description Access

[15:0] POL GPIO Pin Interrupt Polarity Control. R/W

0 Clearing this bit for pin interrupts triggered on a high to low transition.

1 Set this bit for pin interrupts triggered on a low to high transition.

GPIO PORT INTERRUPT A ENABLE REGISTERS

Address: 0x40020028, Reset: 0x0000, Name: GP0IENA

Address: 0x40020068, Reset: 0x0000, Name: GP1IENA

Address: 0x400200A8, Reset: 0x0000, Name: GP2IENA

Table 269. Bit Descriptions for GP0IENA, GP1IENA, GP2IENA

Bits Bit Name Settings Description Access

[15:0] INTAEN GPIO Pin Interrupt A Enable Register. R/W

0 Clear this bit to disable the corresponding pin interrupt.

1 Set this bit to enable the corresponding pin interrupt.

Loading...

Loading...