Reference Manual ADuCM356

REGISTER DETAILS: POWER MANAGEMENT UNIT

analog.com Rev. A | 29 of 312

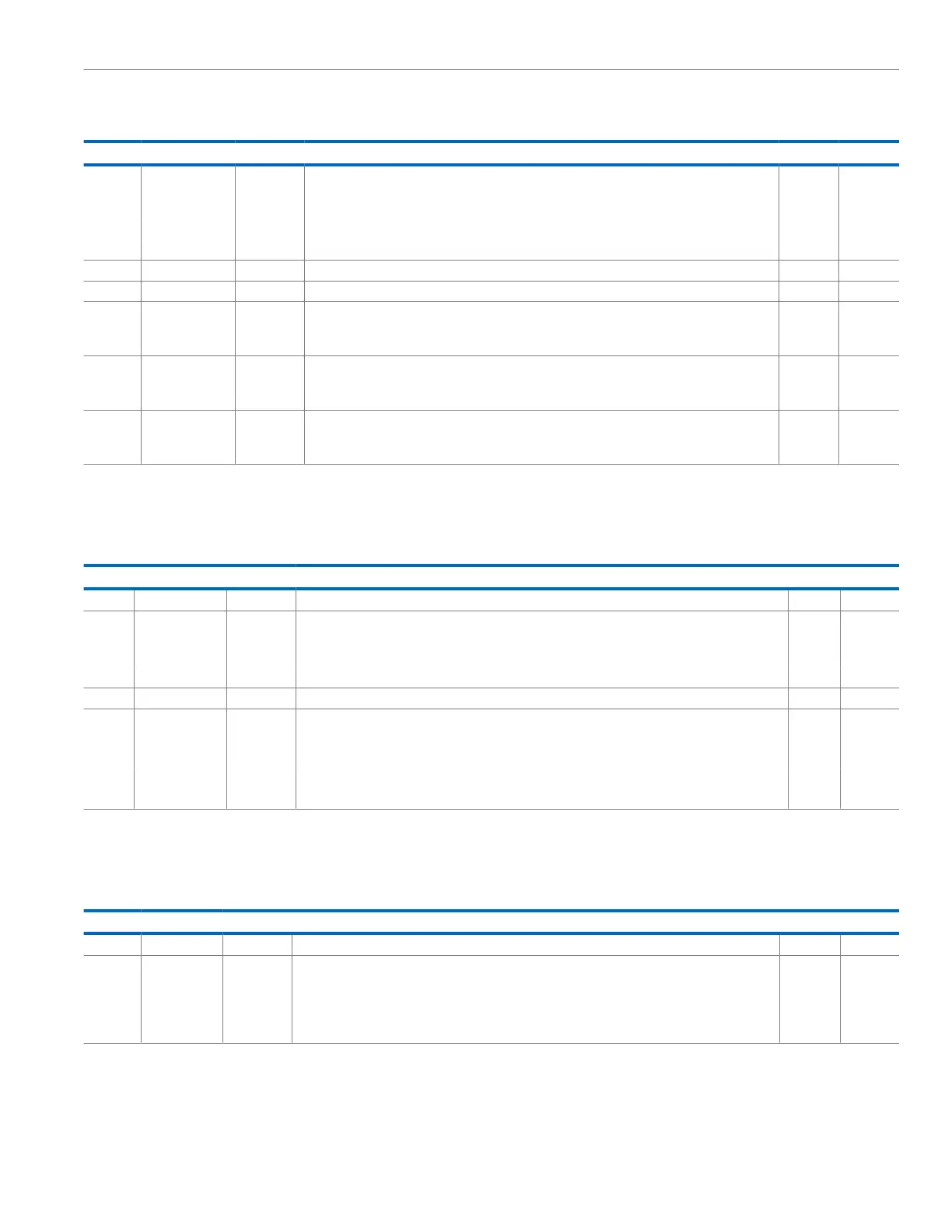

Table 24. Bit Descriptions for PSM_STAT (Continued)

Bits Bit Name Settings Description Reset Access

8 RANGE1 AVDD_DD Range 1 (>2.75 V). This is a write one to clear status bit indicating the relevant

AVDD_DD range. Generates the AVDD_DD range interrupt if IEN, Bit 10 is set. The status bit sets

again even after 1 is written to the flag to clear it if AVDD_DD falls in the specified range.

0x1 R/W1C

1 AVDD_DD in the specified range.

0 AVDD_DD not in the specified range.

7 WICENACK Wake-Up Interrupt Controller (WIC) Enable Acknowledge from Cortex. 0x0 R

[6:3] Reserved Reserved. 0x0 R

2 VREGOVR Status Bit for Alarm Indicating Overvoltage for DVDD_REG. Bit set if DVDD_REG (LDO regulator

output) > 1.32 V. Generates an interrupt if IEN, Bit 2 is set. This is write one to clear this bit. The

status bit sets again even after 1 is written to the flag to clear it if DVDD_REG is > 1.32 V.

0x0 R/W1C

1 VREGUNDR Status Bit for Alarm Indicating DVDD_REG is Less Than 1 V. Generates an interrupt if IEN Bit 1 is

set. This bit sets if DVDD_REG < 1 V. This is a write one to clear bit. The status bit sets again even

after 1 is written to the flag to clear it if DVDD_REG is < 1 V.

0x0 R/W1C

0 VBATUNDR Status Bit Indicating an Alarm that AVDD_DD is Less than 1.8 V. Generates an interrupt if IEN Bit 0

is set. This bit sets if AVDD_DD < 1.83 V. This is a write one to clear bit. The status bit sets again

even after 1 is written to the flag to clear it if AVDD_DD is < 1.83 V.

0x0 R/W1C

POWER MODE REGISTER

Address: 0x4004C008, Reset: 0x00000000, Name: PWRMOD

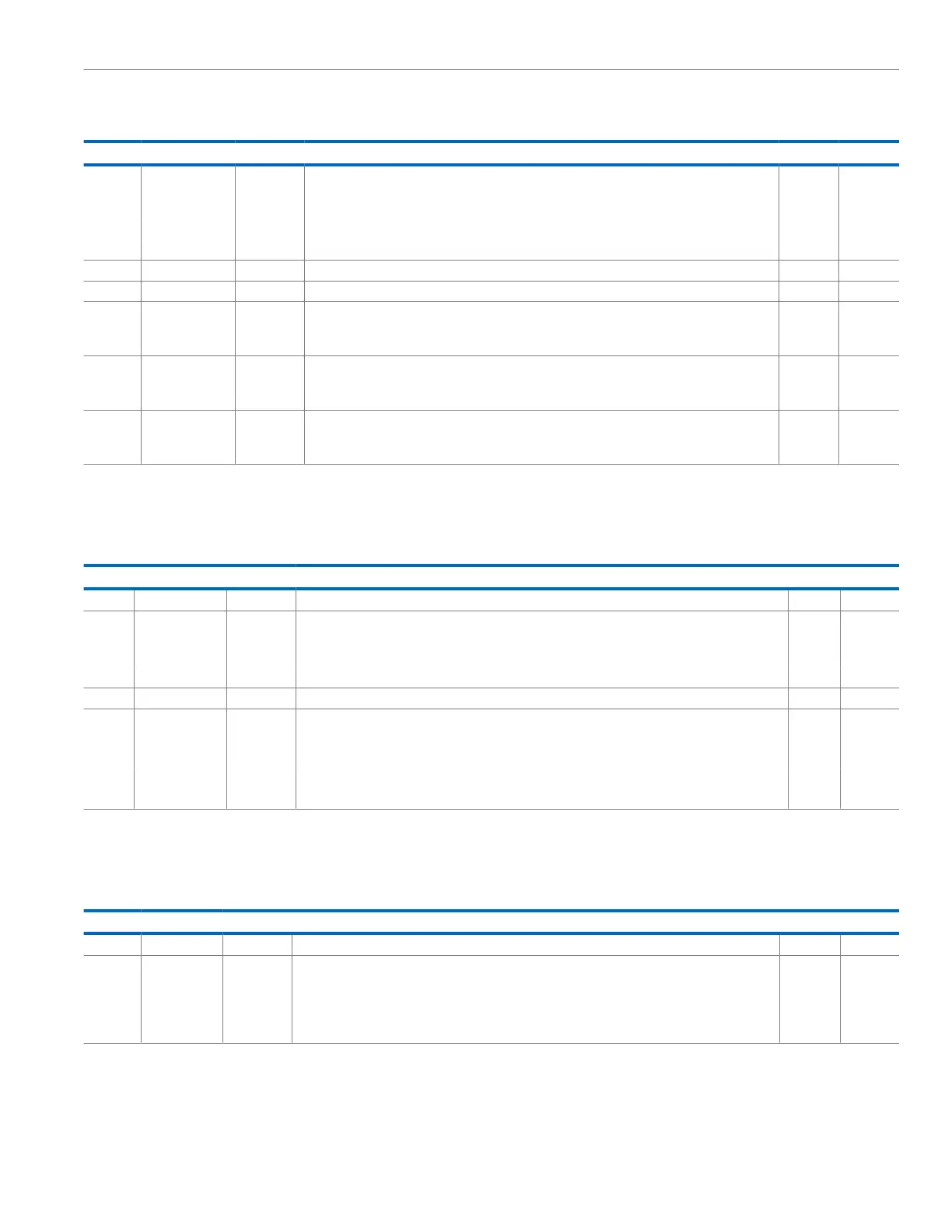

Table 25. Bit Descriptions for PWRMOD

Bits Bit Name Settings Description Reset Access

[31:4] Reserved Reserved. 0x0 R

3 MONVBATN Monitor AVDD_DD During Hibernate Mode. Monitors AVDD_DD by default. DVDD_REG (1.2 V LDO

regulator). Monitoring cannot be disabled.

0x0 R/W

0 AVDD_DD monitor enabled in PMU block. Default.

1 AVDD_DD monitor disabled in PMU block.

2 Reserved Reserved. 0x0 R/W

[1:0] MODE Power Mode Bits. 0x0 R/W

00 Flexi mode.

01 Reserved.

10 Hibernate mode.

11 Reserved.

KEY PROTECTION FOR PWRMOD AND SRAMRET REGISTER

Address: 0x4004C00C, Reset: 0x00000000, Name: PWRKEY

Table 26. Bit Descriptions for PWRKEY

Bits Bit Name Settings Description Reset Access

[31:16] Reserved Reserved. 0x0 R

[15:0] VALUE Power Control Key Register. The PMG0 PWRMOD and PMG0 SRAMRET registers are key protected.

One write to the key is necessary to change the value in the PMG0 PWRMOD and PMG0 SRAMRET

registers. Write 0x4859 to PMG0 PWRKEY before writing to PMG0 PWRMOD or PMG0 SRAMRET

register. A write to any other register on the Arm peripheral bus before writing to PMG0 PWRMOD or

PMG0 SRAMRET returns the protection to the lock state.

0x0000 W

CONTROL FOR RETENTION SRAM DURING HIBERNATE MODE REGISTER

Address: 0x4004C014, Reset: 0x00000000, Name: SRAMRET

Loading...

Loading...