Reference Manual ADuCM356

REGISTER DETAILS: LOW POWER TIA/POTENTIOSTAT AND DAC CIRCUITS

analog.com Rev. A | 94 of 312

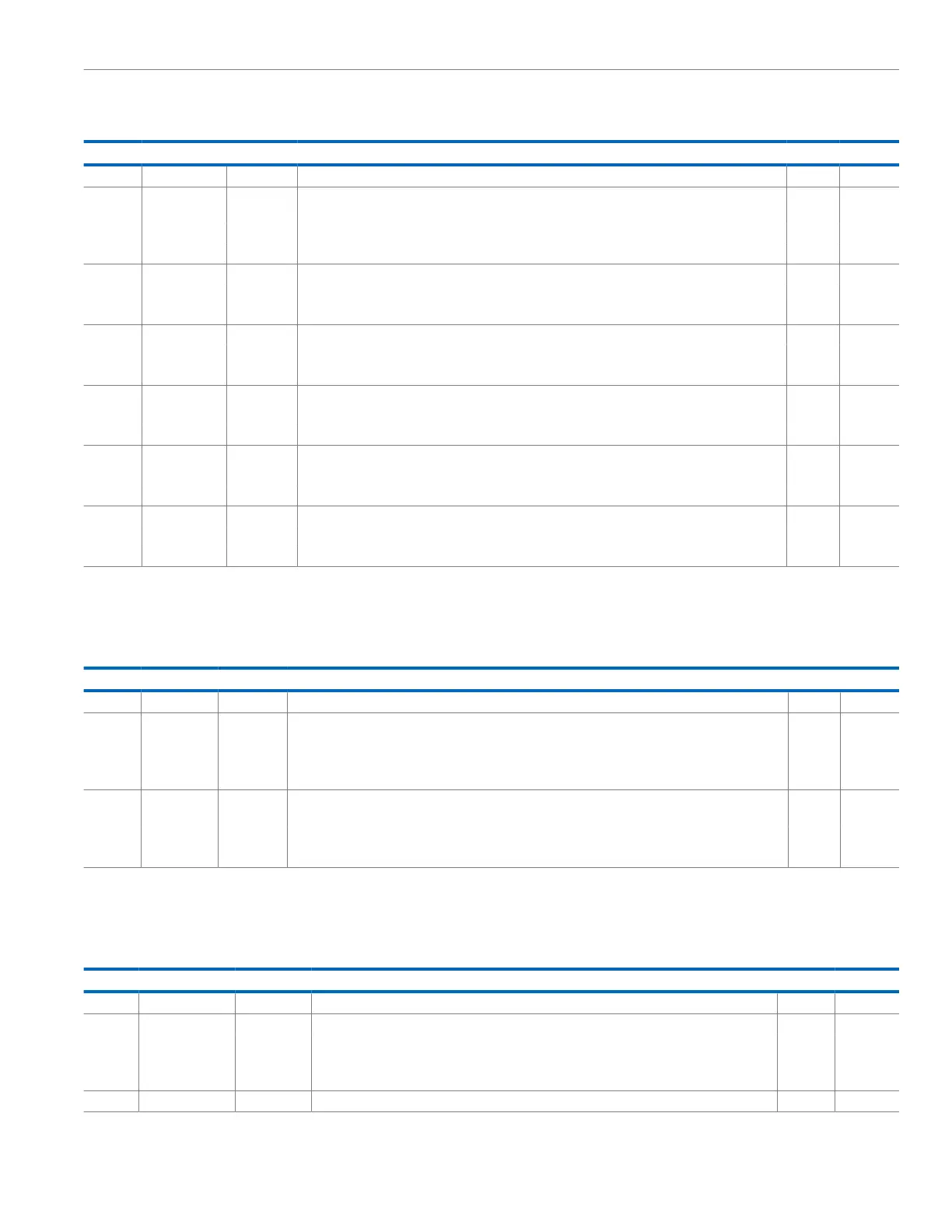

Table 112. Bit Descriptions for LPTIASW1 (Continued)

Bits Bit Name Settings Description Reset Access

1 Close switch.

5 SW5 SW5 Switch Control Active High. Close to connect external capacitor or R

TIA

resistor between the

RC1_0 and RC1_1 pins.

0x0 R/W

0 Open switch.

1 Close switch.

4 SW4 SW4 Switch Control Active High. 0x0 R/W

0 Open switch.

1 Close switch.

3 SW3 SW3 Switch Control Active High. 0x0 R/W

0 Open switch.

1 Close switch.

2 SW2 SW2 Switch Control Active High. 0x0 R/W

0 Open switch.

1 Close switch.

1 SW1 SW1 Switch Control Active High. 0x0 R/W

0 Open switch.

1 Close switch.

0 SW0 SW0 Switch Control Active High. 0x0 R/W

0 Open switch.

1 Close switch.

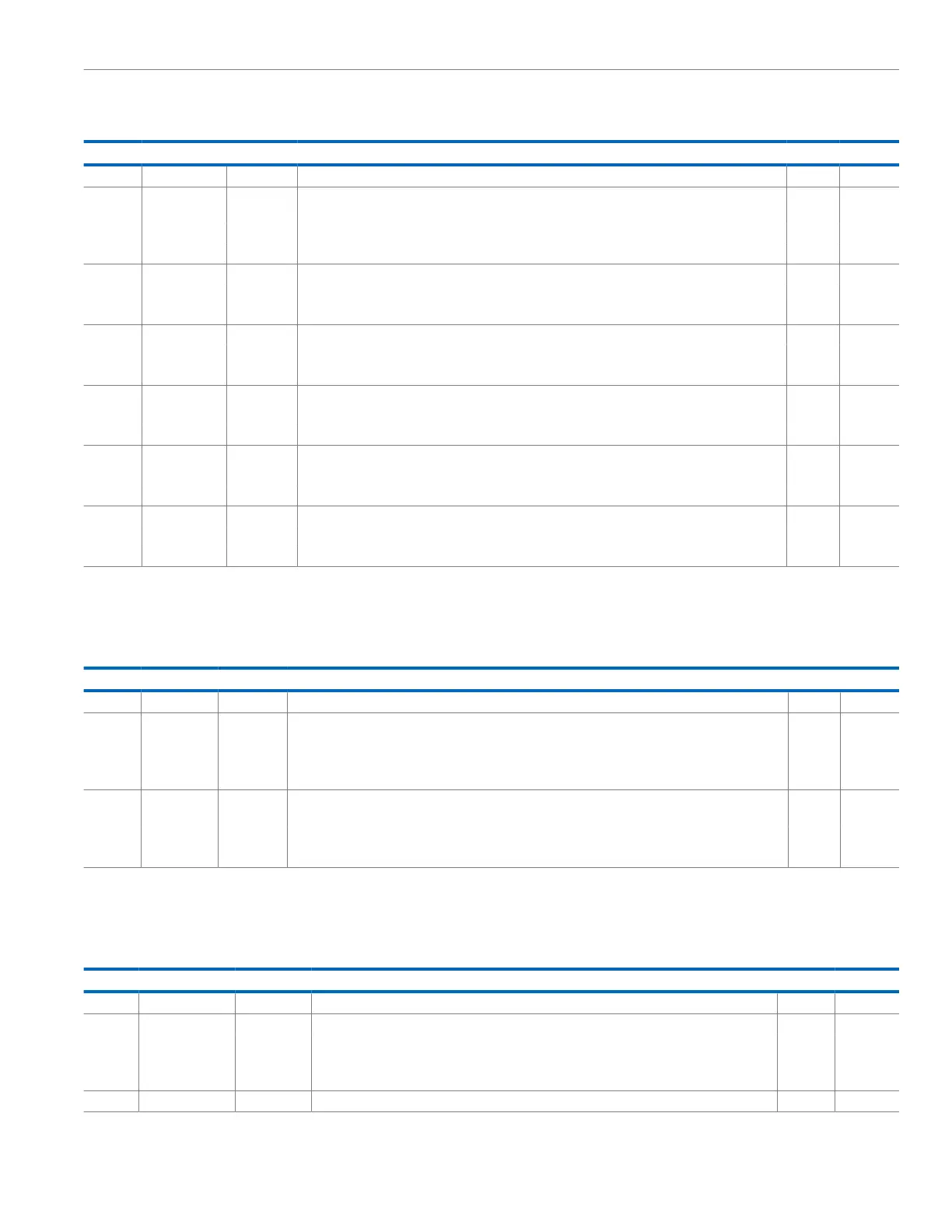

LPDAC0 DATA OUT REGISTER

Address: 0x400C2120, Reset: 0x00000000, Name: LPDACDAT0

Table 113. Bit Descriptions for LPDACDAT0

Bits Bit Name Settings Description Reset Access

[31:18] Reserved Reserved. 0x0 R

[17:12] DACIN6 6-Bit Value, 1 LSB = 34.375 mV. A low-power DAC0 6-bit output data register value between 0 and 0x3F

is expected to set 6-bit output voltage.

0x0 R/W

0 0.2 V.

111111 2.366 V.

[11:0] DACIN12 12-Bit Value, 1 LSB = 537 μV. A low-power DAC0 12-bit output data register value between 0 and 0xFFF

is expected to set 12-bit output voltage.

0x0 R/W

0 0.2 V.

0xFFF 2.4 V.

LPDAC0 SWITCH CONTROL REGISTER

Address: 0x400C2124, Reset: 0x00000000, Name: LPDACSW0

Table 114. Bit Descriptions for LPDACSW0

Bits Bit Name Settings Description Reset Access

[31:6] Reserved Reserved. 0x0 R

5 LPMODEDIS Switch Control. Controls switches connected to the output of low-power DAC0. 0x0 R/W

0 Switches connected to output of low-power DAC configured via LPDACCON0, Bit 5. Default.

1 Overrides LPDACCON0, Bit 5. Switches connected to the low-power DAC0 output are controlled

via LPDACSW0, Bits[4:0].

4 SW4 LPDAC0 SW4 Control. 0x0 R/W

Loading...

Loading...