Reference Manual ADuCM356

REGISTER DETAILS: POWER MANAGEMENT UNIT

analog.com Rev. A | 30 of 312

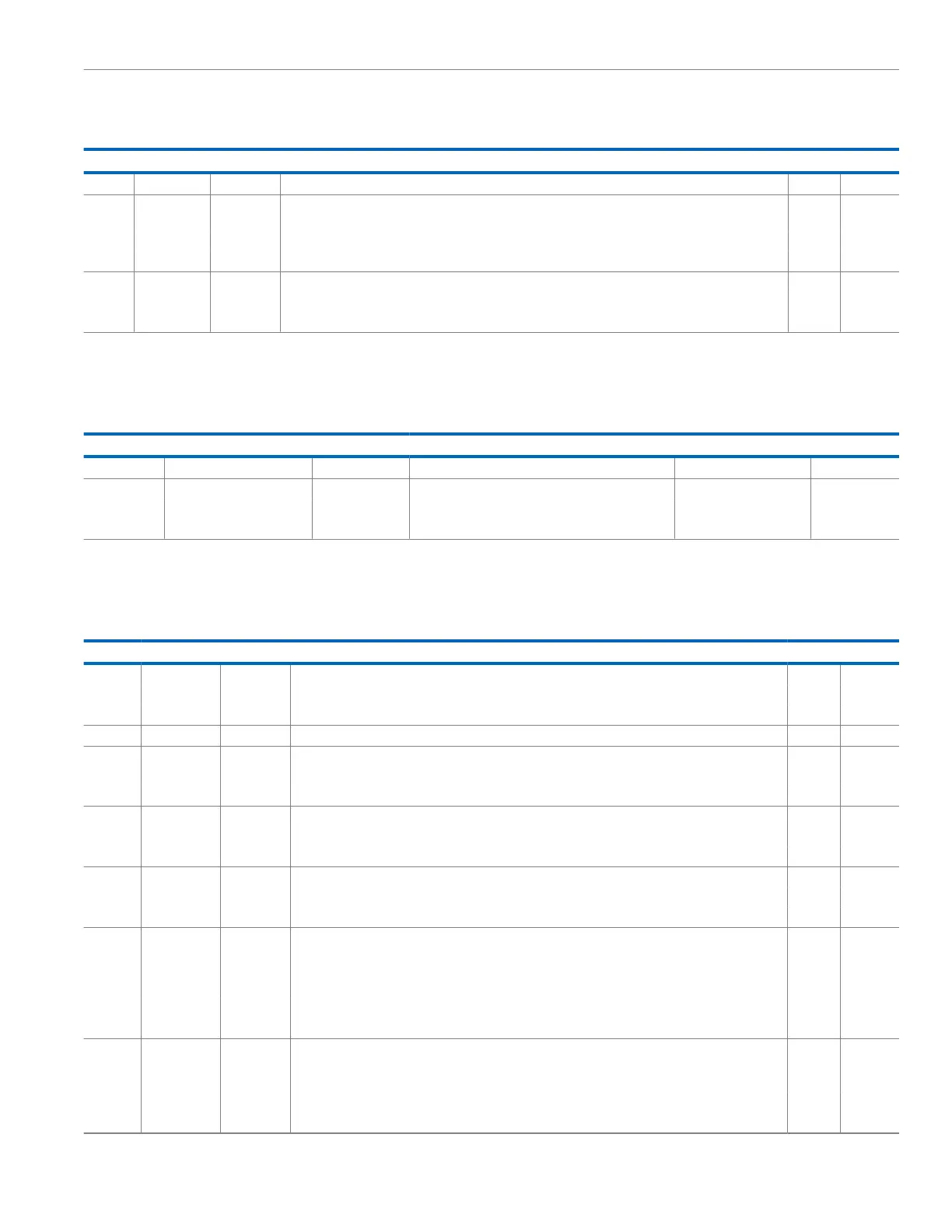

Table 27. Bit Descriptions for SRAMRET

Bits Bit Name Settings Description Reset Access

[31:2] Reserved Reserved. 0x0 R

1 BNK2EN Enable Retention Bank 2 (16 kB). Bank address is 0x10000000 to 0x10003FFF if SRAM_CTL, Bit 31 = 1.

Bank address is 0x20004000 to 0x20007FFF if SRAM_CTL, Bit 31 = 0.

0x0 R/W

0 Disable retention of SRAM Bank 2.

1 Enable retention of SRAM Bank 2 during hibernate mode. This option consumes more power.

0 BNK1EN Enable Retention Bank 1 (8 kB). Bank address is 0x20002000 to 0x20003FFF. 0x0 R/W

0 Disable retention of SRAM Bank 1.

1 Enable retention of SRAM Bank 1 during hibernate mode. This option consumes more power.

HIGH-POWER BUCK CONTROL REGISTER

Address: 0x4004C044, Reset: 0x00000000, Name: CTL1

Table 28. Bit Descriptions for CTL1

Bits Bit Name Settings Description Reset Access

[31:1] Reserved Reserved. 0x00000000 R/W

0 HPBUCKEN Enable High-Power Buck. 0x0 R/W

0 Buck regulator is disabled.

1 Buck regulator is enabled.

CONTROL FOR SRAM PARITY AND INSTRUCTION SRAM REGISTER

Address: 0x4004C260, Reset: 0x80000000, Name: SRAM_CTL

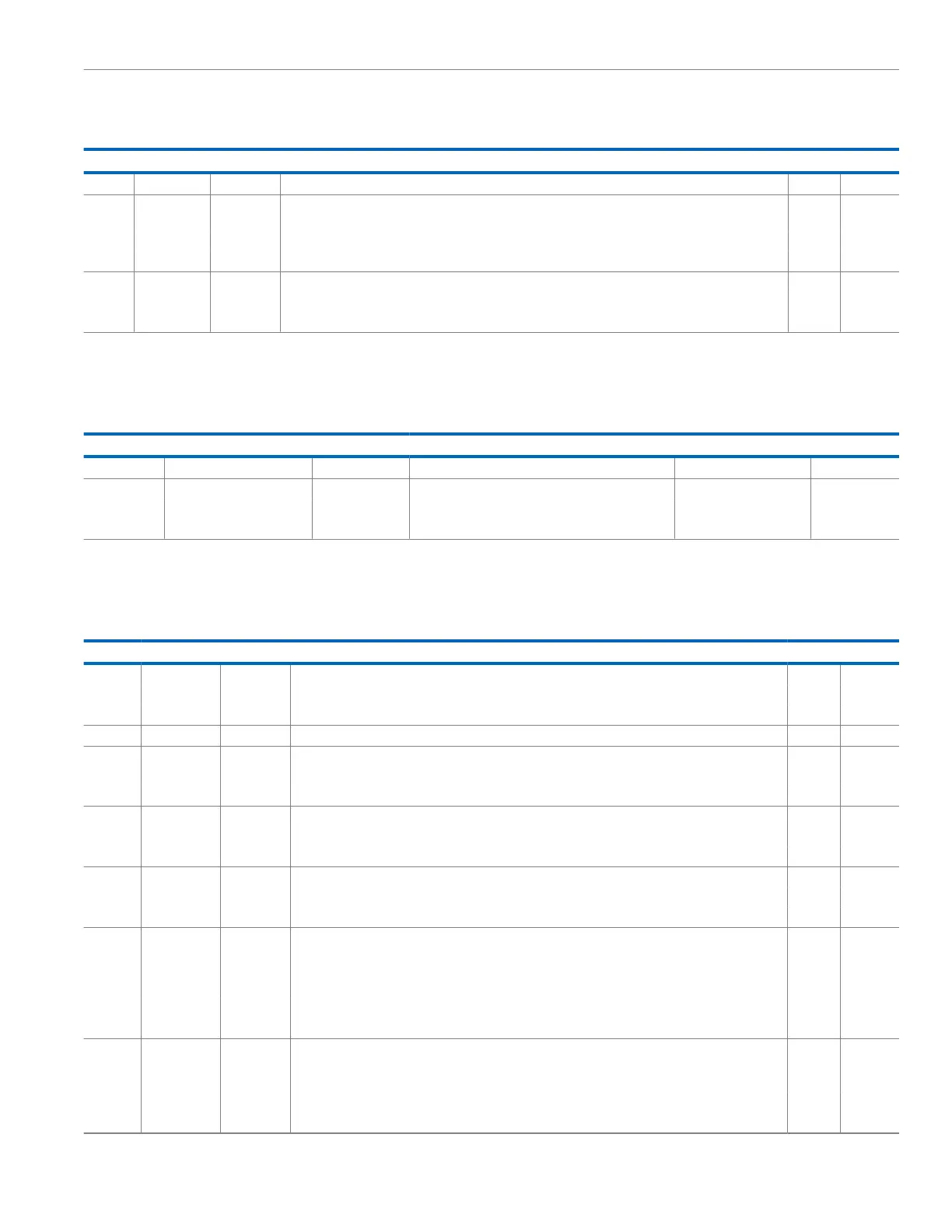

Table 29. Bit Descriptions for SRAM_CTL

Bits Bit Name Settings Description Reset Access

31 INSTREN Enables Instruction SRAM. 0x1 R/W

1 CPU instructions use SRAM address range of 0x10000000 to 0x10003FFF.

0 SRAM used for data.

[30:22] Reserved Reserved. 0x000 R

21 PENBNK5 Enable Parity Check for SRAM Bank 5. 0x0 R/W

0 Disable parity check of this bank of SRAM.

1 Enable parity check of this bank of SRAM.

20 PENBNK4 Enable Parity Check for SRAM Bank 4. 0x0 R/W

0 Disable parity check of this bank of SRAM.

1 Enable parity check of this bank of SRAM.

19 PENBNK3 Enable Parity Check for SRAM Bank 3. 0x0 R/W

0 Disable parity check of this bank of SRAM.

1 Enable parity check of this bank of SRAM.

18 PENBNK2 Enable Parity Check for SRAM Bank 2. SRAM Address 0x10000000 to Address 0x10003FFF if

SRAM_CTL, Bit 31 = 1. Address range is 0x20004000 to 0x20007FFF if SRAM_CTL, Bit 31 = 0. Parity

is checked when data is read and when a byte or half word data is written to this SRAM area. If a parity

error is detected, a bus error is generated and the execution vectors to the bus fault interrupt.

0x0 R/W

0 Disable parity check of this bank of SRAM.

1 Enable parity check of this bank of SRAM.

17 PENBNK1 Enable Parity Check for SRAM Bank 1. SRAM Address 0x20002000 to Address 0x20003FFF. Parity is

checked when data is read and when a byte or half word data is written to this SRAM area. If a parity

error is detected, a bus error is generated and the execution vectors to the bus fault interrupt.

0x0 R/W

0 Disable parity check of this bank of SRAM.

1 Enable parity check of this bank of SRAM.

Loading...

Loading...