Reference Manual ADuCM356

REGISTER SUMMARY: I

2

C

analog.com Rev. A | 226 of 312

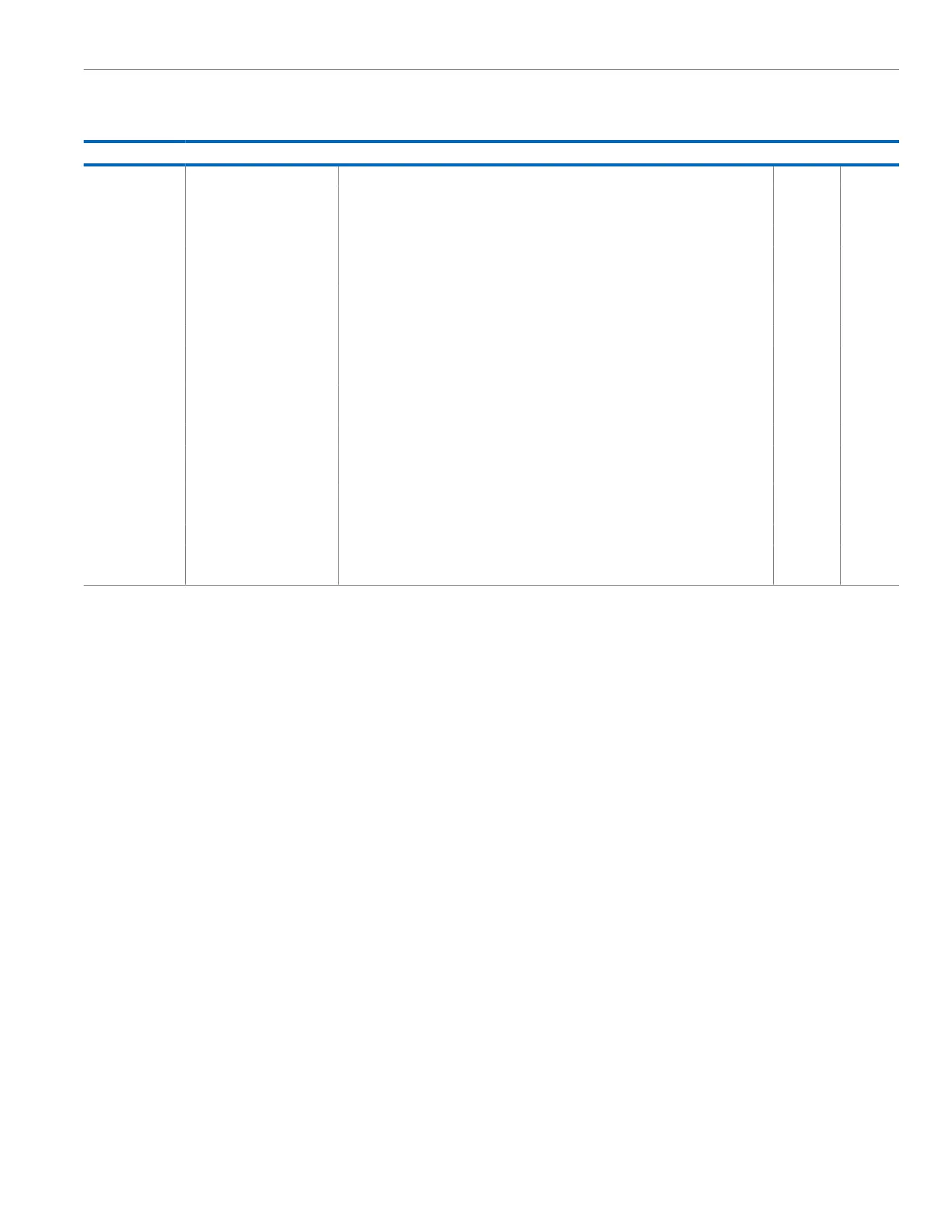

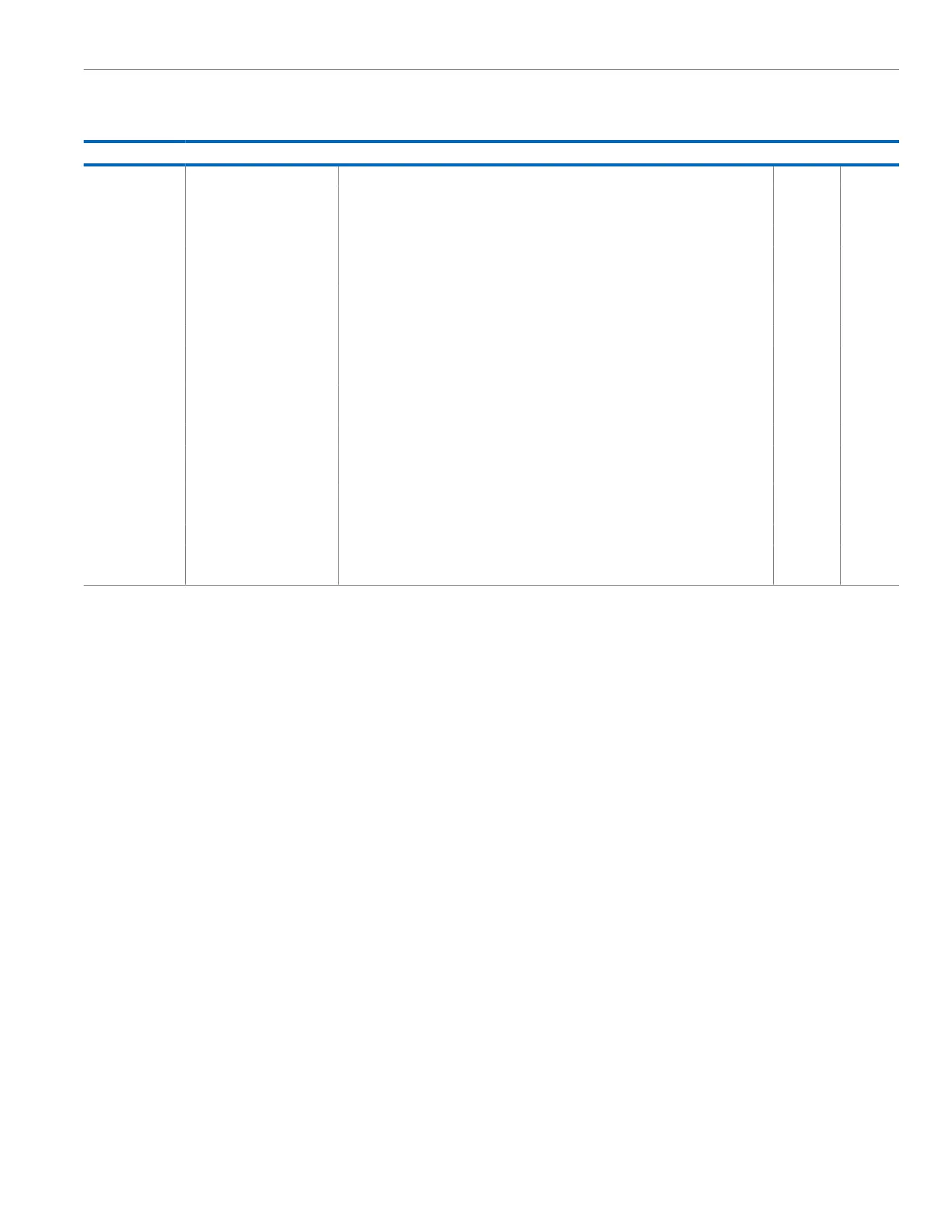

Table 282. I

2

C Register Summary

Address Name Description Reset Access

0x40003000 MCTL Initiator control 0x0000 R/W

0x40003004 MSTAT Initiator status 0x6000 R

0x40003008 MRX Initiator receive data 0x0000 R

0x4000300C MTX Initiator transmit data 0x0000 R/W

0x40003010 MRXCNT Initiator receive data count 0x0000 R/W

0x40003014 MCRXCNT Initiator current receive data count 0x0000 R

0x40003018 ADR1 First initiator address byte 0x0000 R/W

0x4000301C ADR2 Second initiator address byte 0x0000 R/W

0x40003024 DIV Serial clock period divisor 0x1F1F R/W

0x40003028 SCTL Target control 0x0000 R/W

0x4000302C SSTAT Target I

2

C status, error, and IRQ 0x0001 R

0x40003030 SRX Target receive 0x0000 R

0x40003034 STX Target transmit 0x0000 R/W

0x40003038 ALT Hardware general call ID 0x0000 R/W

0x4000303C ID0 First target address device ID 0x0000 R/W

0x40003040 ID1 Second target address device ID 0x0000 R/W

0x40003044 ID2 Third target address device ID 0x0000 R/W

0x40003048 ID3 Fourth target address device ID 0x0000 R/W

0x4000304C FSTAT Initiator and target FIFO status 0x0000 R/W

0x40003050 SHCTL Initiator and target shared control 0x0000 W

0x40003058 ASTRETCH_SCL Automatic stretch control for initiator and target mode 0x0000 R/W

Loading...

Loading...