Reference Manual ADuCM356

REGISTER DETAILS: DMA

analog.com Rev. A | 178 of 312

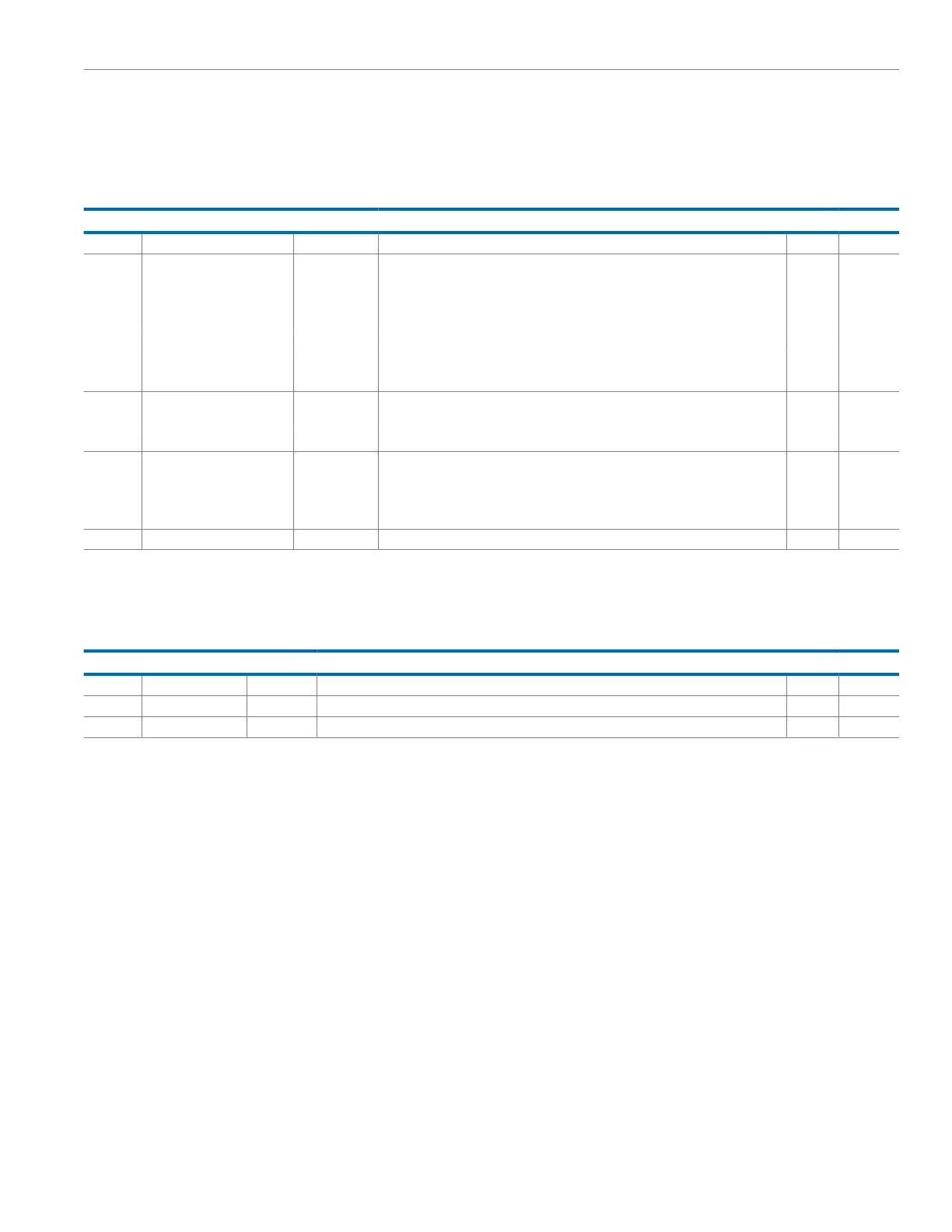

FIFO CONFIGURATION REGISTER

Address: 0x400C2008, Reset: 0x00001010, Name: FIFOCON

Table 219. Bit Descriptions for FIFOCON

Bits Bit Name Settings Description Reset Access

[31:16] Reserved Reserved. 0x0 R

[15:13] DATAFIFOSRCSEL Selects the Source for the Data FIFO. 0x0 R/W

000, 001, 110,

111

ADC data. ADC data is output of sinc3 filter.

010 DFT data, 18-bit real part and 18-bit imaginary part.

011 Sinc2 output.

100 Statistic variance output.

101 Statistics mean result.

12 DATAFIFODMAREQEN Enable Data FIFO DMA Channel. 0x1 R/W

0 Disable DMA requests for data FIFO.

1 Enable DMA requests for data FIFO.

11 DATAFIFOEN Data FIFO Enable. 0x0 R/W

0 FIFO is reset. No data transfers may take place. Sets the read and write pointers to

the default values (empty FIFO). Status indicates if FIFO is empty.

1 Normal operation. FIFO is not reset.

[10:0] Reserved Reserved. 0x10 R

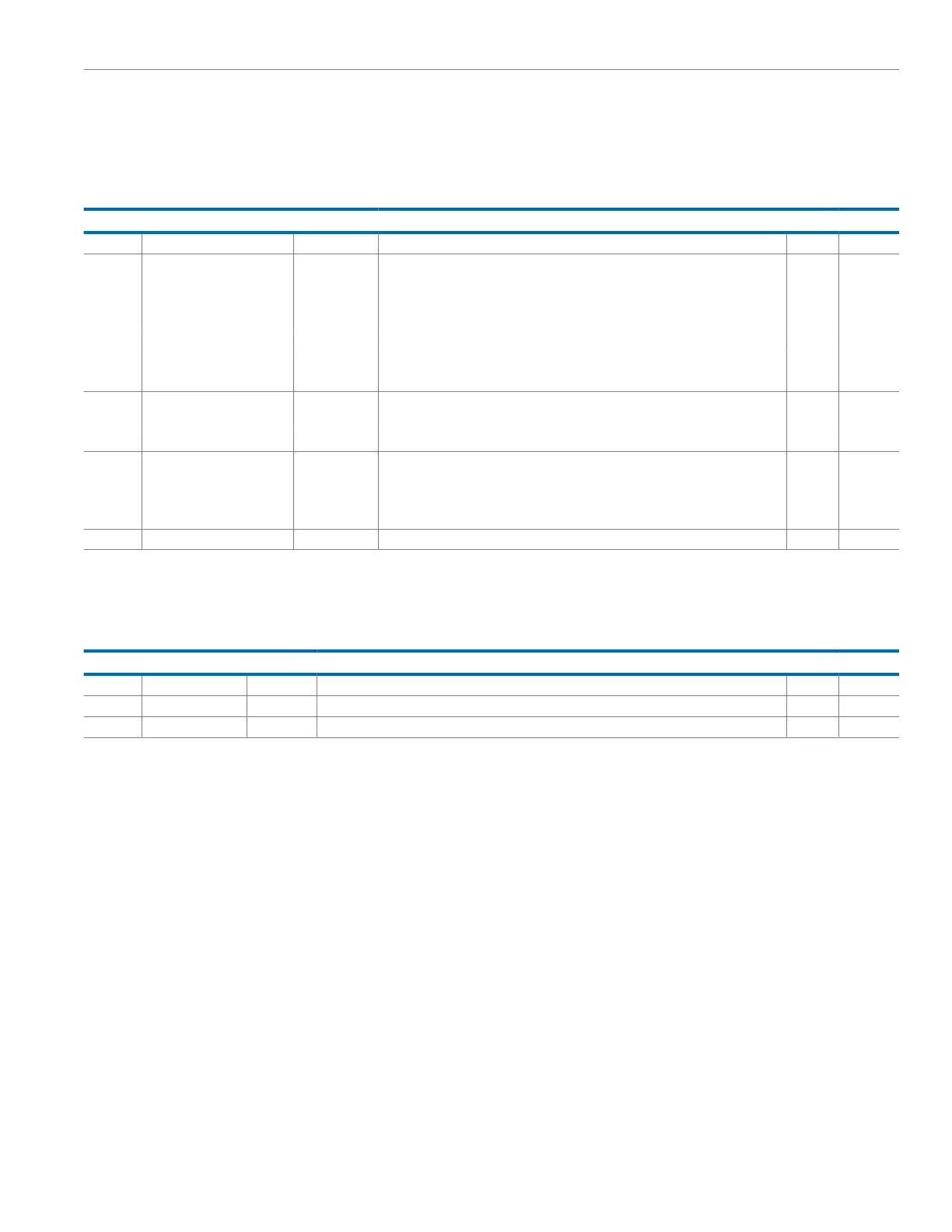

DATA FIFO READ REGISTER

Address: 0x400C206C, Reset: 0x00000000, Name: DATAFIFORD

Table 220. Bit Descriptions for DATAFIFORD

Bits Bit Name Settings Description Reset Access

[31:25] ECC ECC of Lower 25 Bits. 0x0 R

[24:18] Reserved Reserved. 0x0 R

[17:0] DATAFIFOOUT Data FIFO Read. If data FIFO is empty, a read of this register returns 0x00000000. 0x0 R

Loading...

Loading...