Reference Manual ADuCM356

REGISTER DETAILS: I

2

C

analog.com Rev. A | 234 of 312

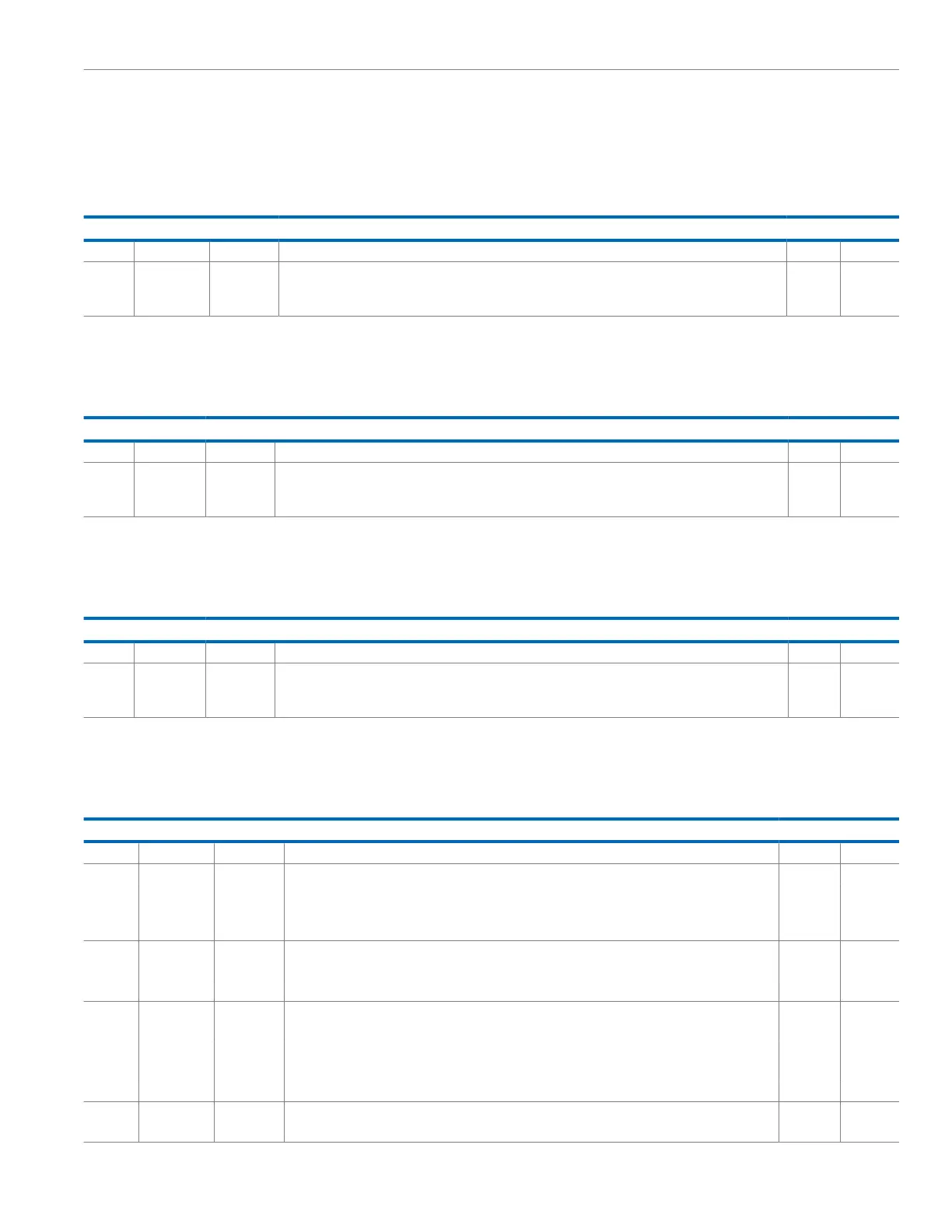

SECOND TARGET ADDRESS DEVICE ID REGISTER

Address: 0x40003040, Reset: 0x0000, Name: ID1

Table 298. Bit Descriptions for ID1

Bits Bit Name Settings Description Reset Access

[15:8] Reserved Reserved. 0x0 R

[7:0] ID1 Target Device ID 1. ID1, Bits[7:1] are programmed with the device ID. ID1, Bit 0 is don't care. See SCTL,

Bit 1 to see how this register is programmed with a 10-bit address. Take care to avoid I

2

C reserved target

addresses with values less than 0x10 and greater than 0xF6.

0x0 R/W

THIRD TARGET ADDRESS DEVICE ID REGISTER

Address: 0x40003044, Reset: 0x0000, Name: ID2

Table 299. Bit Descriptions for ID2

Bits Bit Name Settings Description Reset Access

[15:8] Reserved Reserved. 0x0 R

[7:0] ID2 Target Device ID 2. ID2, Bits[7:1] are programmed with the device ID. ID2, Bit 0 is don't care. See SCTL,

Bit 1 to see how this register is programmed with a 10-bit address. Take care to avoid I

2

C reserved target

addresses with values less than 0x10 and greater than 0xF6.

0x0 R/W

FOURTH TARGET ADDRESS DEVICE ID REGISTER

Address: 0x40003048, Reset: 0x0000, Name: ID3

Table 300. Bit Descriptions for ID3

Bits Bit Name Settings Description Reset Access

[15:8] Reserved Reserved. 0x0 R

[7:0] ID3 Target Device ID 3. ID3, Bits[7:1] are programmed with the device ID. ID3, Bit 0 is don't care. See SCTL,

Bit 1 to see how this register is programmed with a 10-bit address. Take care to avoid I

2

C reserved target

addresses with values less than 0x10 and greater than 0xF6.

0x0 R/W

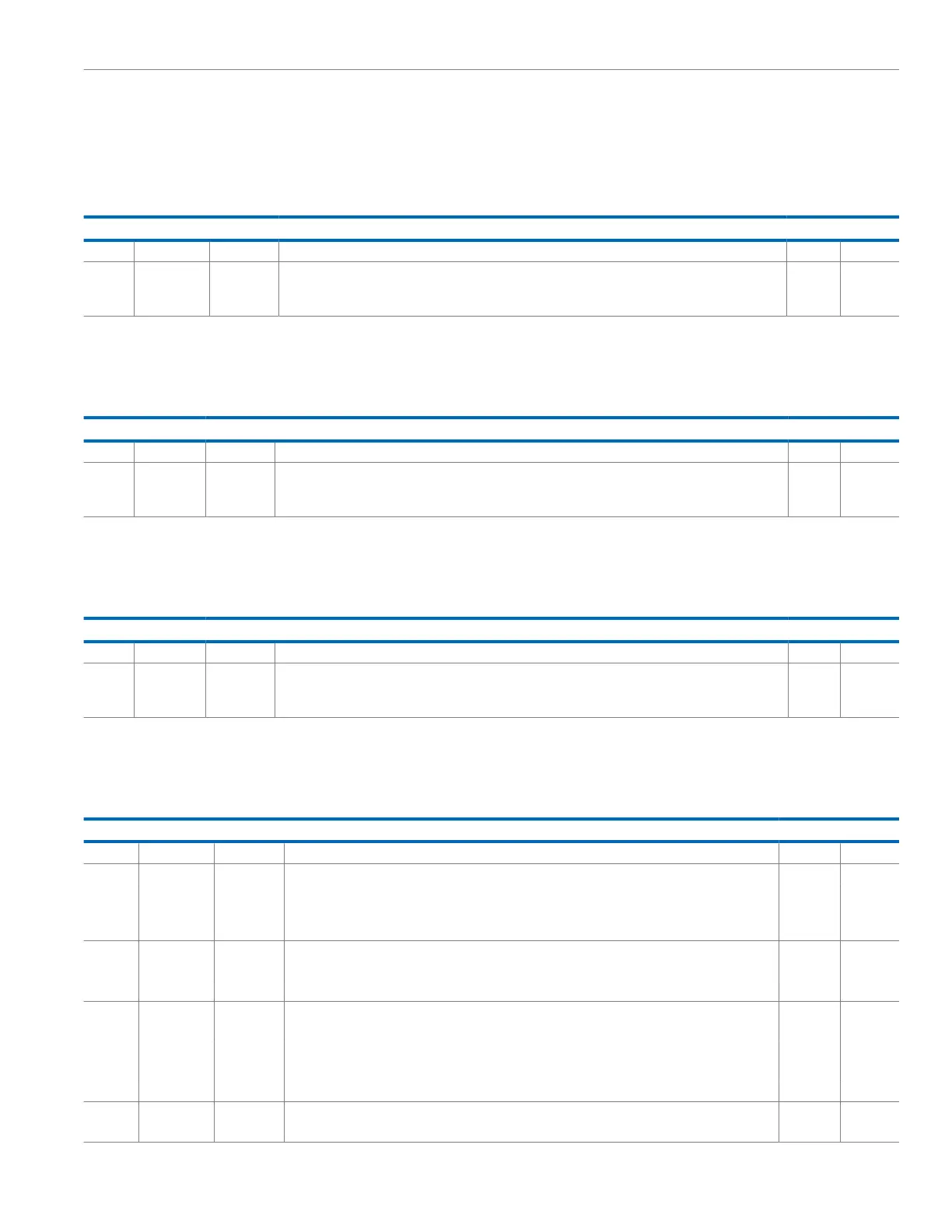

INITIATOR AND TARGET FIFO STATUS REGISTER

Address: 0x4000304C, Reset: 0x0000, Name: FSTAT

Table 301. Bit Descriptions for FSTAT

Bits Bit Name Settings Description Reset Access

[15:10] Reserved Reserved. 0x0 R/W

9 MFLUSH Flush the Initiator Transmit FIFO. 0x0 W

0 No effect.

1 Flush the initiator transmit FIFO. The initiator transmit FIFO must be flushed if arbitration is lost or a

target responds with a no acknowledge.

8 SFLUSH Flush the Target Transmit FIFO. 0x0 W

0 No effect.

1 Flush the target transmit FIFO.

[7:6] MRXF Initiator Receive FIFO Status. The status is a count of the number of bytes in a FIFO. 0x0 R

00 FIFO empty.

01 1 byte in the FIFO.

10 2 bytes in the FIFO.

11 Reserved.

[5:4] MTXF Initiator Transmit FIFO Status. The status is a count of the number of bytes in a FIFO. 0x0 R

00 FIFO empty.

Loading...

Loading...