Reference Manual ADuCM356

REGISTER DETAILS: SPI0/SPI1

analog.com Rev. A | 245 of 312

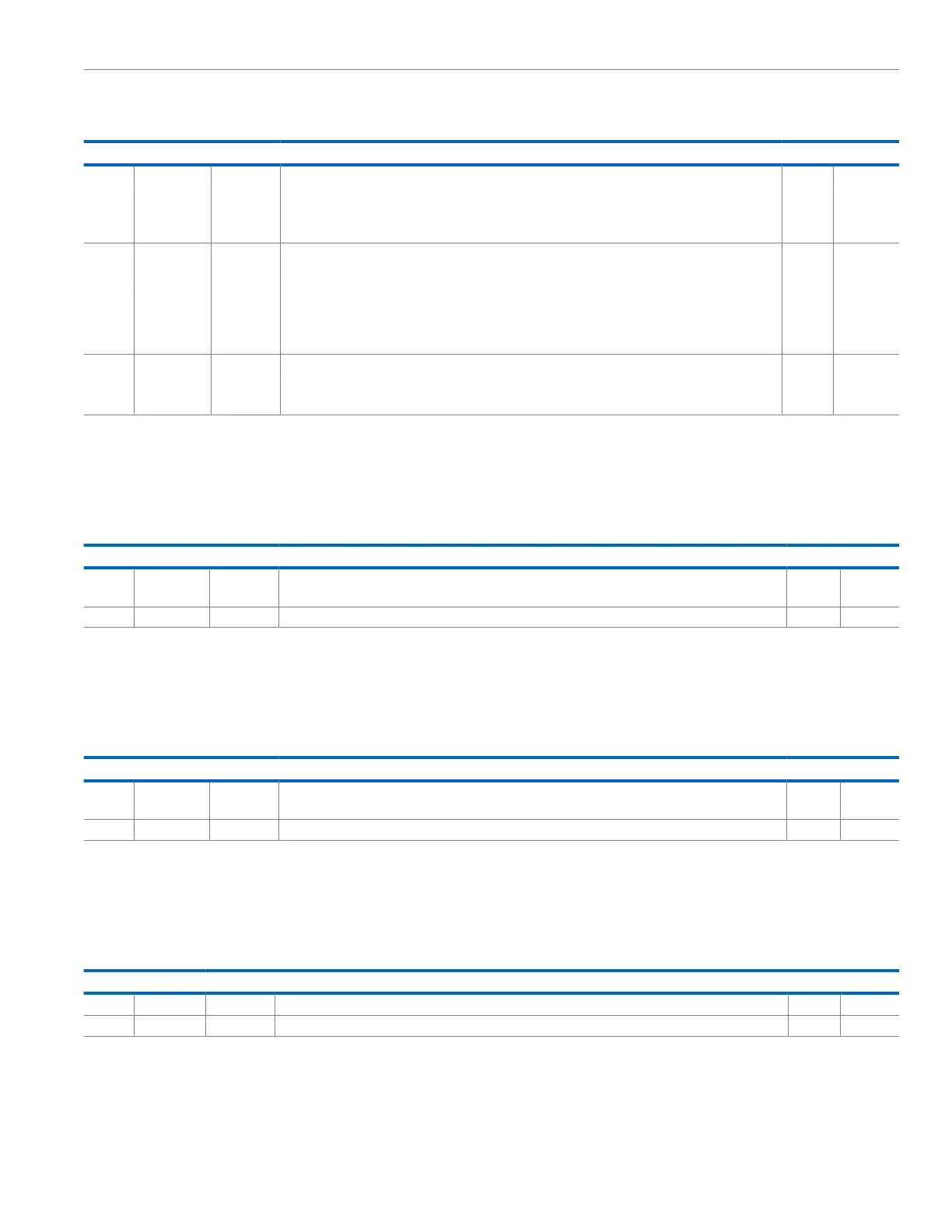

Table 306. Bit Descriptions for SPI0_STAT, SPI1_STAT (Continued)

Bits Bit Name Settings Description Reset Access

2 TXEMPTY SPI Transmit FIFO Empty Interrupt. 0x0 R/W1C

0 Cleared to 0 when 1 is written to this bit or when SPIx_CTL, Bit 0 is cleared to 0.

1 Set when the transmit FIFO is empty. This bit generates an interrupt if SPIx_IEN, Bit 14 is set to 1 except

when SPIx_CTL, Bit 13 is set.

1 XFRDONE SPI Transfer Completion. This bit indicates the status of SPI transfer completion in initiator mode. 0x0 R/W1C

0 Cleared to 0 when 1 is written to this bit.

1 Set when the transfer of SPIx_CNT, Bits[13:0] number of bytes has finished. In target mode or if

SPIx_CNT, Bits[13:0] = 0, this bit is invalid. If SPIx_IENx, Bit 13 is set, this bit generates an interrupt. It

uses the state of the initiator state machine to determine the completion of a SPI transfer. Therefore, a

chip select override does not affect this bit.

0 IRQ SPI Interrupt Status. 0x0 R

0 Cleared to 0 when all SPI interrupt sources are cleared.

1 Set when an SPI based interrupt occurs.

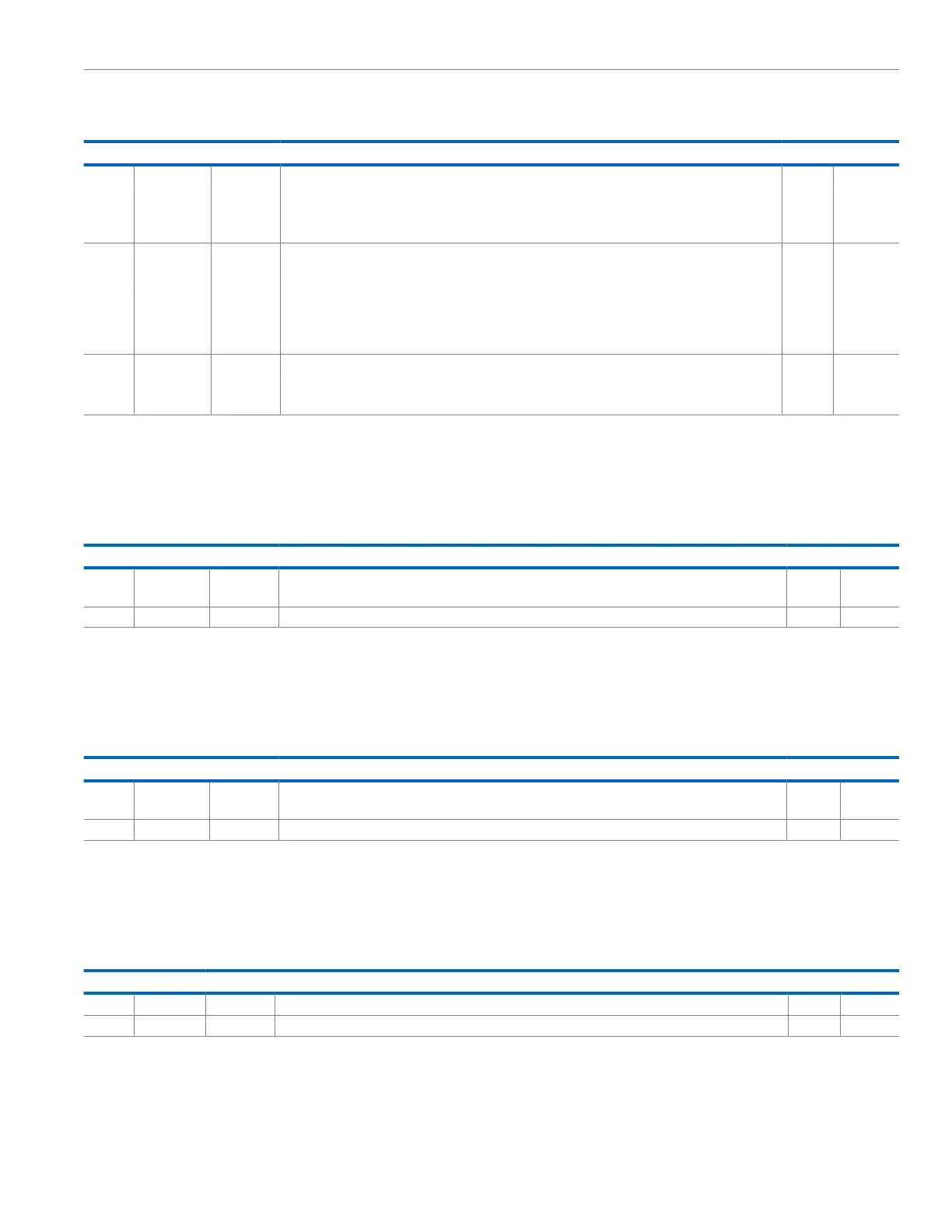

RECEIVE REGISTERS

Address: 0x40004004, Reset: 0x0000, Name: SPI0_RX

Address: 0x40024004, Reset: 0x0000, Name: SPI1_RX

Table 307. Bit Descriptions for SPI0_RX, SPI1_RX

Bits Bit Name Settings Description Reset Access

[15:8] BYTE2 8-Bit Receive Buffer. These 8 bits are used only in DMA mode, where all FIFO accesses occur as half word

accesses. They return 0 if DMA is disabled.

0x0 R

[7:0] BYTE1 8-Bit Receive Buffer. 0x0 R

TRANSMIT REGISTERS

Address: 0x40004008, Reset: 0x0000, Name: SPI0_TX

Address: 0x40024008, Reset: 0x0000, Name: SPI1_TX

Table 308. Bit Descriptions for SPI0_TX, SPI1_TX

Bits Bit Name Settings Description Reset Access

[15:8] BYTE2 8-Bit Transmit Buffer. These 8 bits are used only in DMA mode, where all FIFO accesses occur as half

word accesses. They return 0 if DMA is disabled.

0x0 W

[7:0] BYTE1 8-Bit Transmit Buffer. 0x0 W

BAUD RATE SELECTION REGISTERS

Address: 0x4000400C, Reset: 0x0000, Name: SPI0_DIV

Address: 0x4002400C, Reset: 0x0000, Name: SPI1_DIV

Table 309. Bit Descriptions for SPI0_DIV, SPI1_DIV

Bits Bit Name Settings Description Reset Access

[15:6] Reserved Reserved. 0x0 R

[5:0] VALUE SPI Clock Divider. The clock divider value is the factor used to divide UCLK to generate the serial clock. 0x0 R/W

CONFIGURATION REGISTERS

Address: 0x40004010, Reset: 0x0000, Name: SPI0_CTL

Address: 0x40024010, Reset: 0x0000, Name: SPI1_CTL

Loading...

Loading...