Reference Manual ADuCM356

REGISTER DETAILS: ADC CIRCUIT

analog.com Rev. A | 66 of 312

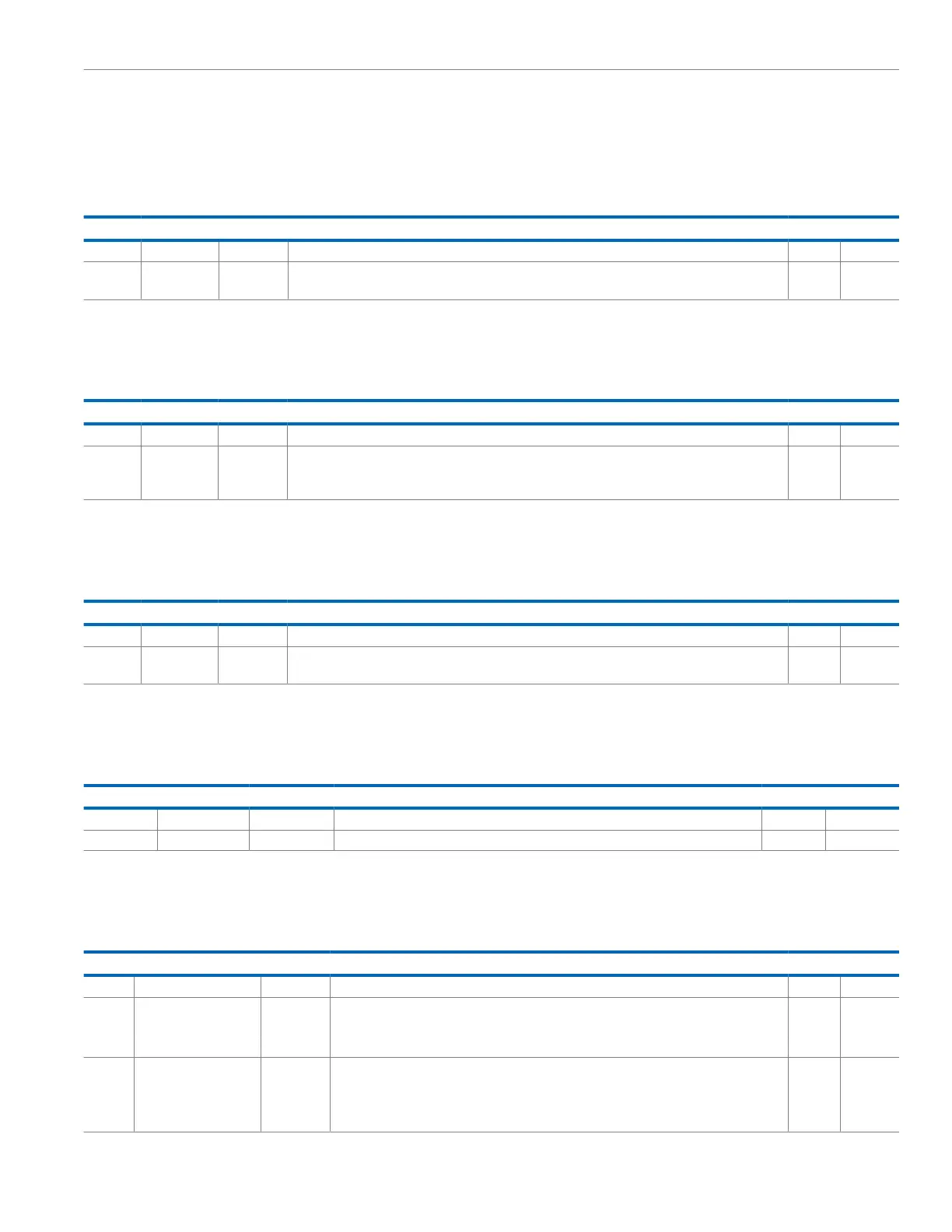

DFT RESULT, REAL PART REGISTER

Address: 0x400C2078, Reset: 0x00000000, Name: DFTREAL

Table 66. Bit Descriptions for DFTREAL

Bits Bit Name Settings Description Reset Access

[31:18] Reserved Reserved. 0x0 R

[17:0] DATA DFT Real. DFT hardware accelerator returns a complex number. This register returns the 18-bit real part

of the complex number from the DFT result. The DFT result is represented in twos complement.

0x0 R/W

DFT RESULT, IMAGINARY PART REGISTER

Address: 0x400C207C, Reset: 0x00000000, Name: DFTIMAG

Table 67. Bit Descriptions for DFTIMAG

Bits Bit Name Settings Description Reset Access

[31:18] Reserved Reserved. 0x0 R

[17:0] DATA DFT Imaginary. DFT hardware accelerator returns a complex number. This register returns the 18-bit

imaginary part of the complex number from the DFT result. DFT result is represented in twos

complement.

0x0 R/W

SINC2 AND SUPPLY REJECTION FILTER RESULT REGISTER

Address: 0x400C2080, Reset: 0x00000000, Name: SINC2DAT

Table 68. Bit Descriptions for SINC2DAT

Bits Bit Name Settings Description Reset Access

[31:16] Reserved Reserved. 0x0 R

[15:0] RESULT Sinc2 and Low-Pass Filter Result. Sinc2 and power supply rejection filter, ADC output result. Data output

from 50 Hz or 60 Hz rejection filter. When new data is available, ADCINTSTA, Bit 2 is set to 1.

0x0 R/W

TEMPERATURE SENSOR 0 RESULT REGISTER

Address: 0x400C2084, Reset: 0x00000000, Name: TEMPSENSDAT0

Table 69. Bit Descriptions for TEMPSENSDAT0

Bits Bit Name Settings Description Reset Access

[31:16] Reserved Reserved. 0x0 R

[15:0] DATA Temperature Sensor. ADC temperature sensor Channel 0 result. 0x0 R/W

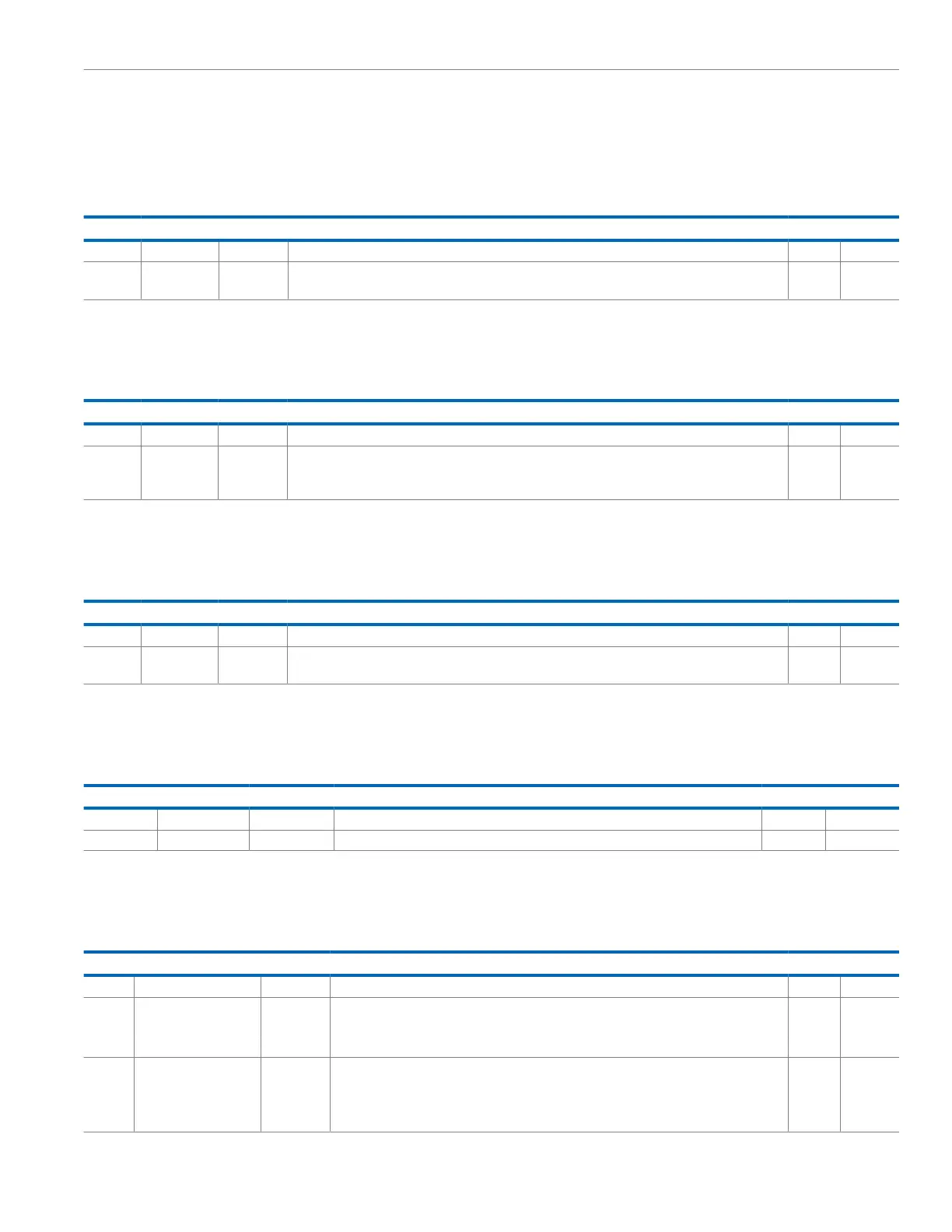

ANALOG CAPTURE INTERRUPT ENABLE REGISTER

Address: 0x400C2088, Reset: 0x00000000, Name: ADCINTIEN

Table 70. Bit Descriptions for ADCINTIEN

Bits Bit Name Settings Description Reset Access

[31:8] Reserved Reserved. 0x0 R

7 MEANIEN Mean Interrupt. Mean result ready interrupt enable. 0x0 R/W

0 Interrupt disabled.

1 Interrupt enabled.

6 ADCDELTAFAILIEN ADC Delta Value Check Fail Interrupt Enable. When set, this bit generates an interrupt if the

difference between two consecutive ADC samples is greater than the value in the ADC delta

range.

0x0 R/W

0 Interrupt disabled.

Loading...

Loading...