Reference Manual ADuCM356

REGISTER DETAILS: POWER MANAGEMENT UNIT

analog.com Rev. A | 28 of 312

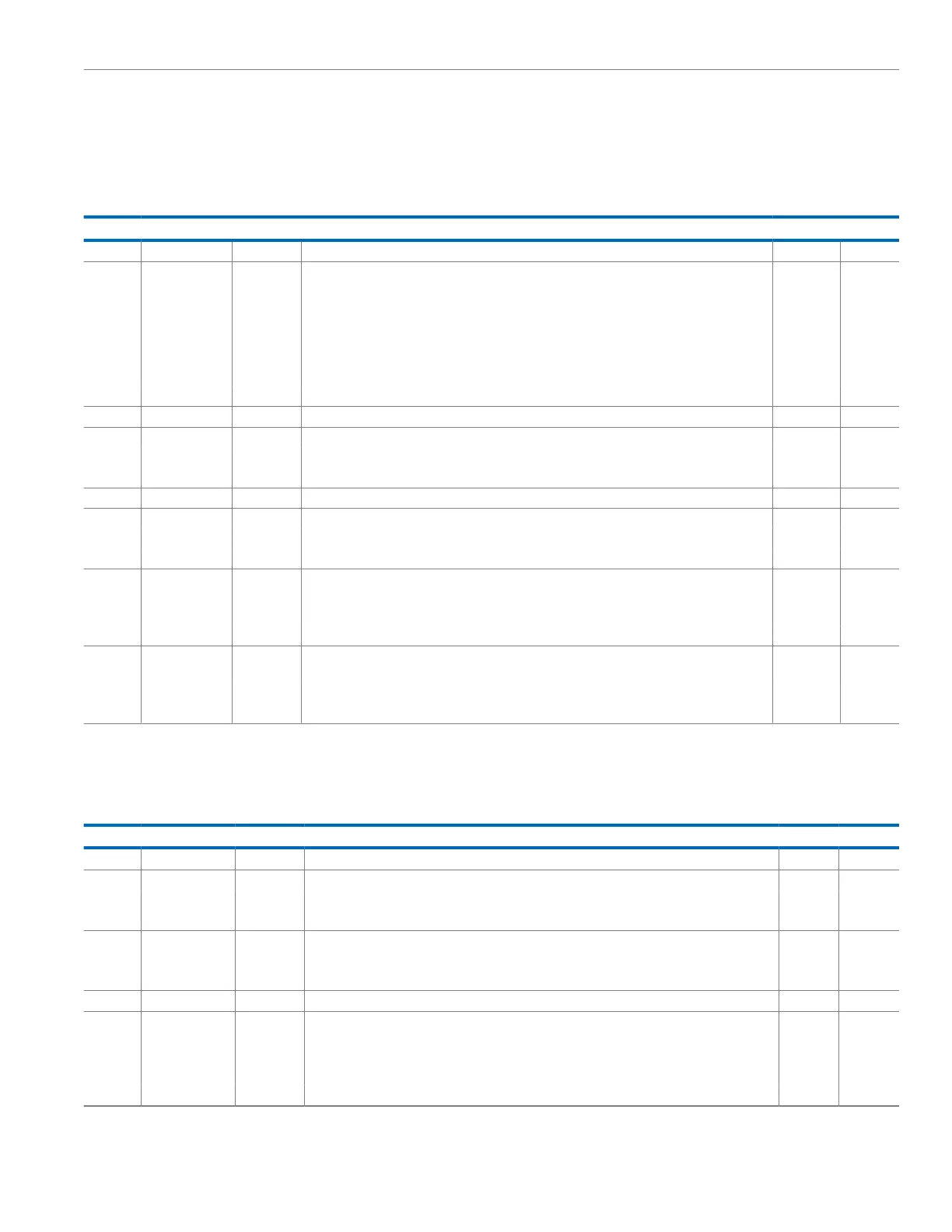

POWER SUPPLY MONITOR INTERRUPT ENABLE REGISTER

Address: 0x4004C000, Reset: 0x00000000, Name: IEN

Table 23. Bit Descriptions for IEN

Bits Bit Name Settings Description Reset Access

[31:11] Reserved Reserved. 0x00000 R

10 IENBAT Interrupt Enable for AVDD_DD Range. Set this bit if an interrupt must be generated for the

RANGEBAT bit. Configure RANGEBAT for the interrupt to be generated and then set IENBAT. An

interrupt is generated if the DVDD_AD pin falls in the RANGEBAT bit. For example, if the battery

is within the required range and the user wishes to monitor the battery, the user must configure the

RANGE2 bit in the PSM_STAT register. Clear all PSM_STAT flags and then enable this interrupt.

Otherwise, the RANGE1 bit of the PSM_STAT register of battery keeps issuing the interrupt.

0x0 R/W

0 Disable IENBAT as an interrupt source.

1 Enable IENBAT as an interrupt source.

9 Reserved Reserved. 0x0 R

8 RANGEBAT Battery Monitor Range. Configure the appropriate RANGEBAT bit setting to generate the interrupt. 0x0 R/W

0 Configure to generate interrupt if AVDD_DD > 2.75 V.

1 Configure to generate interrupt if AVDD_DD is between 2.75 V and 1.6 V.

[7:3] Reserved Reserved. 0x00 R

2 VREGOVR Enable Interrupt When DVDD_REG is Greater Than 1.32 V (Overvoltage). 0x0 R/W

0 Disable VREGOVR as an interrupt source.

1 Enable VREGOVR as an interrupt source.

1 VREGUNDR Enable Interrupt when DVDD_REG is Less Than 1 V (Undervoltage). If enabled, the interrupt

connects to nonmaskable interrupt (NMI).

0x0 R/W

0 Disable VREGUNDR as an interrupt source.

1 Enable VREGUNDR as an interrupt source.

0 VBAT Enable Interrupt for AVDD_DD. If enabled, the interrupt connects to NMI and generates an interrupt

if AVDD_DD < 1.83 V.

0x0 R/W

0 Disable AVDD_DD as an interrupt source.

1 Enable AVDD_DD as an interrupt source.

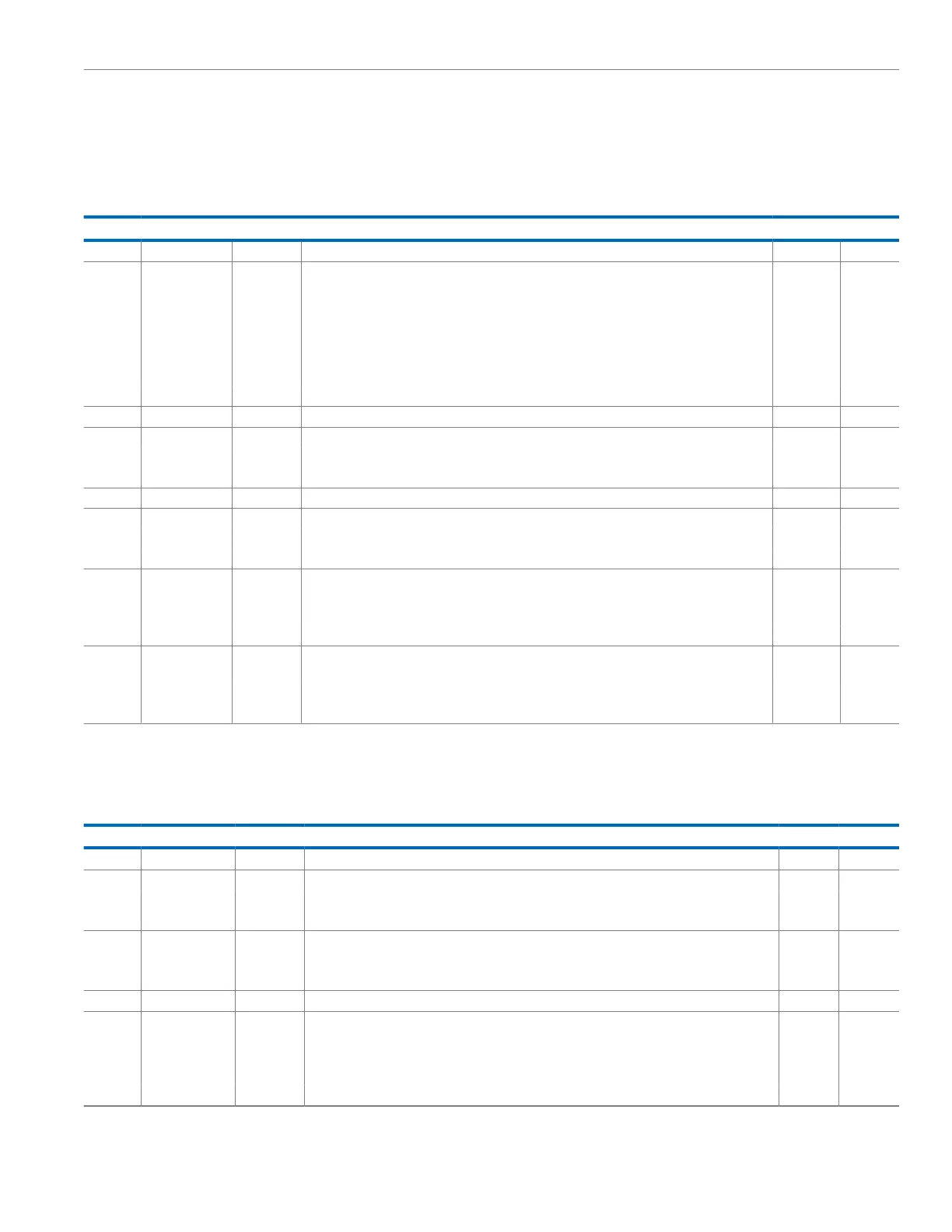

POWER SUPPLY MONITOR STATUS REGISTER

Address: 0x4004C004, Reset: 0x2100, Name: PSM_STAT

Table 24. Bit Descriptions for PSM_STAT

Bits Bit Name Settings Description Reset Access

[31:15] Reserved Reserved. 0x0000 R

14 RORANGE2 AVDD_DD Range 2 (2.75 V and 2.3 V) Read Only Status Bit. 0x0 R

1 AVDD_DD in the range specified.

0 AVDD_DD not in the range specified.

13 RORANGE1 Battery Voltage Range 1 (>2.75 V) Read Only Status Bit. 0x1 R

1 AVDD_DD in the range specified.

0 AVDD_DD not in the range specified.

[12:10] Reserved Reserved. 0x0 R

9 RANGE2 AVDD_DD Range 2 (2.75 V and 2.3 V). This is a write one to clear the status bit that indicates the

relevant DVDD_AD range. Generates the AVDD_DD range interrupt if IEN, Bit 10 is set. The status

bit sets again even after 1 is written to the flag to clear it if AVDD_DD falls in the range specified.

0x0 R/W1C

1 AVDD_DD in the range specified.

0 AVDD_DD not in the range specified.

Loading...

Loading...