Reference Manual ADuCM356

SYSTEM EXCEPTIONS AND PERIPHERAL INTERRUPTS

analog.com Rev. A | 43 of 312

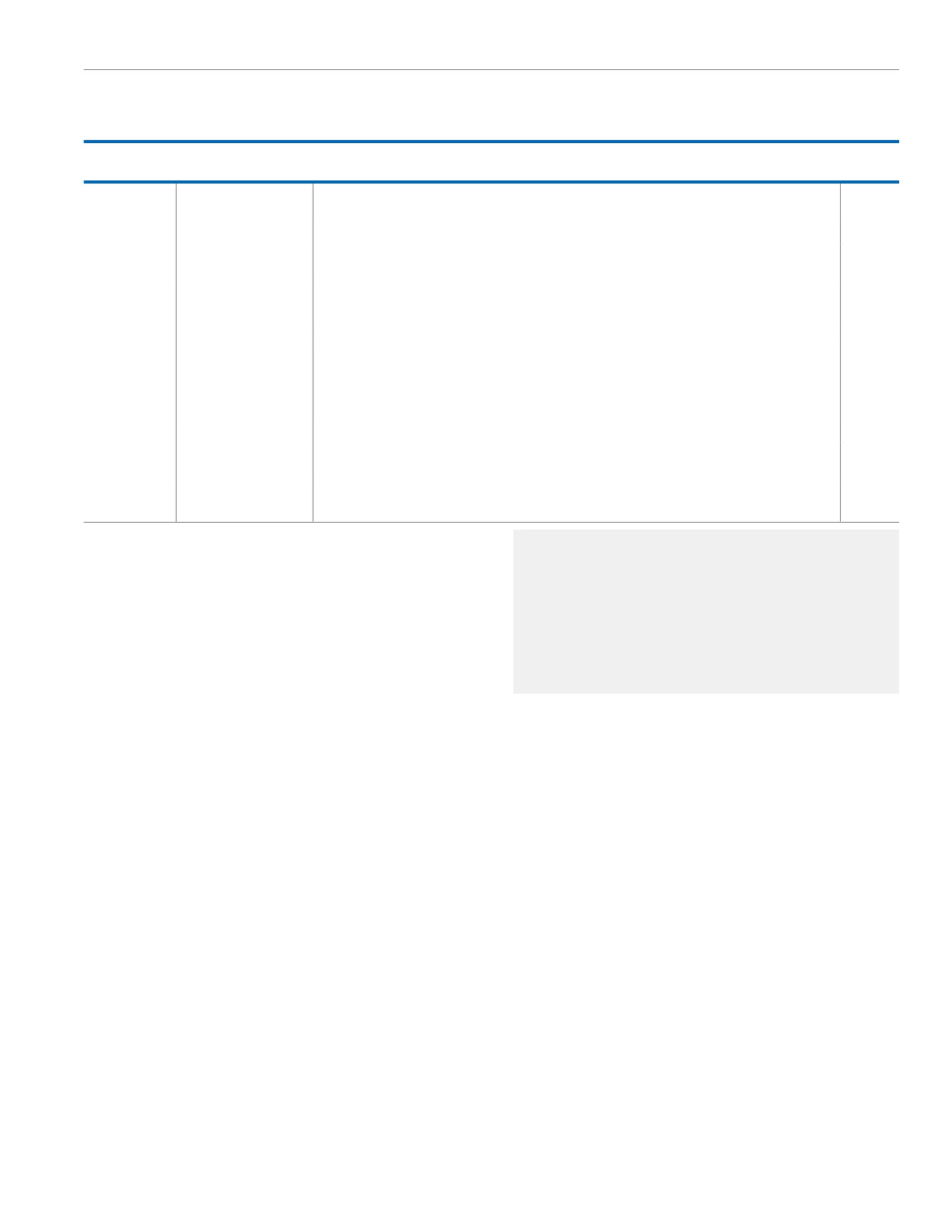

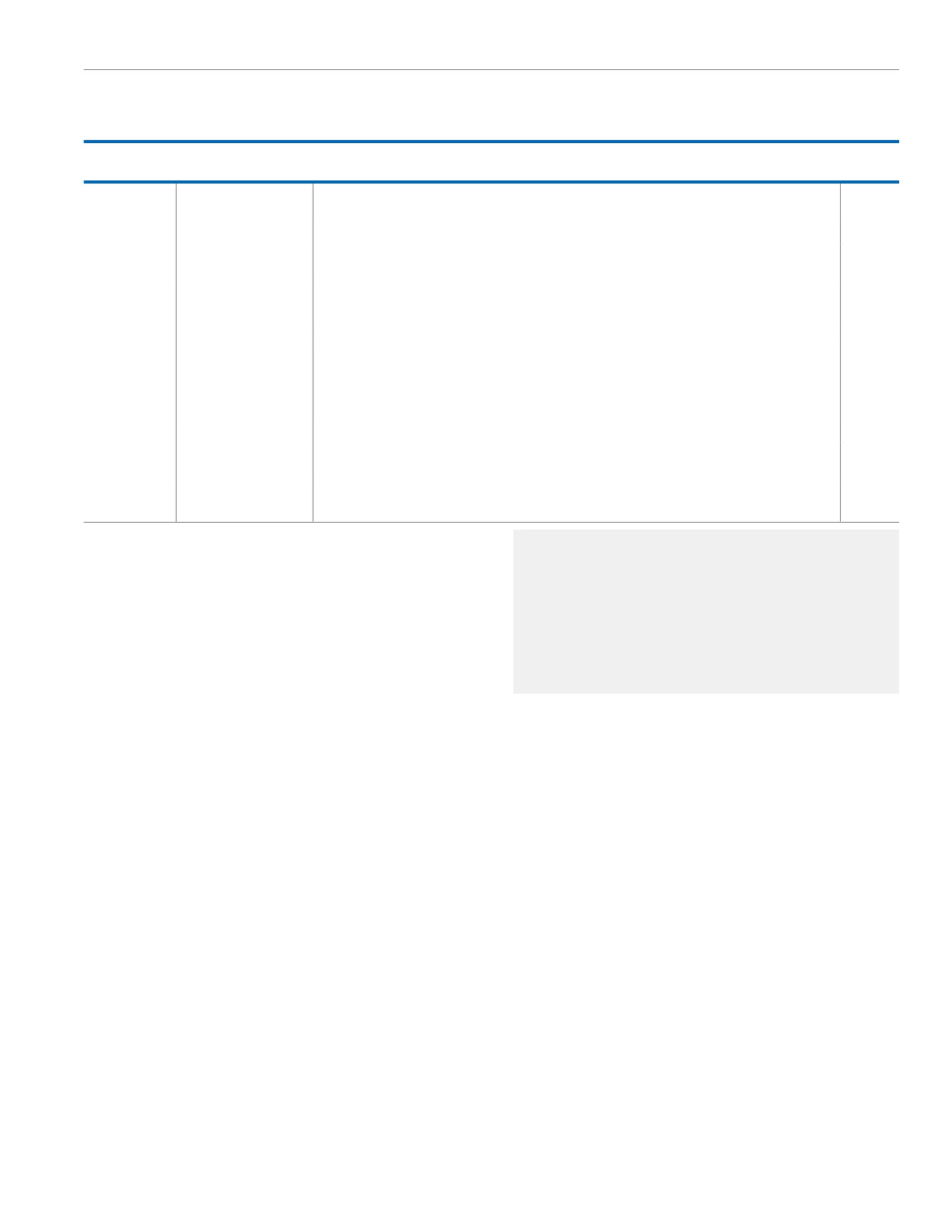

Table 43. NVIC Registers (Continued)

Address

Analog Devices

Header File Name Description Access

0xE000E438 IPR14 IRQ56 to IRQ59 priority. R/W

0xE000E43C IPR15 IRQ60 to IRQ63 priority. R/W

0xE000ED00 CPUID CPU ID base. R

0xE000ED04 ICSR Interrupt control and status. R/W

0xE000ED08 VTOR Vector table offset. R/W

0xE000ED0C AIRCR Application interrupt and reset control. R/W

0xE000ED10 SCR System control. R/W

0xE000ED14 CCR Configuration control. R/W

0xE000ED18 SHPR1 System Handler 1. R/W

0xE000ED1C SHPR2 System Handler 2. R/W

0xE000ED20 SHPR3 System Handler 3. R/W

0xE000ED24 SHCRS System handler control and state. R/W

0xE000ED28 CFSR Configurable fault status. R/W

0xE000ED2C HFSR Hard fault status. R/W

0xE000ED34 MMAR Memory manage fault address. R/W

0xE000ED38 BFAR Bus fault address. R/W

0xE000EF00 STIR Software trigger interrupt. W

EXTERNAL INTERRUPT CONFIGURATION

Two external interrupts are implemented, separate from those de-

scribed in the Digital Inputs and Outputs section. One of these

external interrupts is the P1.0/SYS_WAKE pin. The other is the

interrupt source from the analog die that connects to External

Interrupt 3 line of the digital die, which can be connected to the

UART input pin (P0.11/UART_SIN). These two external interrupts

can be separately configured to detect any combination of the

following type of events:

► Edge: rising edge, falling edge, or both rising and falling edges.

An interrupt signal (pulse) is sent to the NVIC upon detecting a

transition from low to high, high to low, or on either high to low or

low to high.

► Level: high or low. An interrupt signal is generated and remains

asserted in the NVIC until the conditions generating the interrupt

deassert. The level must be maintained for a minimum of one

core clock cycle to be detected.

The external interrupt detection unit block is in the always on

section and allows the external interrupt to wake up the device

when in hibernate mode.

Ensure that the associated GPxIE register bits are enabled for the

required external interrupt input. The GPxIE registers enable the

input path circuit for the external interrupt.

For example, for External Interrupt 1 (SYS_WAKE), the following

code disables the P1.0/SYS_WAKE output pin and enables the

input path. The appended code also enables the External Interrupt

1 NVIC interrupt source.

pADI_GPIO1->OEN &= 0xFFFE; //Disable

P1.0 output.

pADI_GPIO1->IEN |= 0x0001; //Enable in►

put path for P1.0 input.

pADI_XINT0->CFG0 |=0x80; //External

IRQ1 enabled.

NVIC_EnableIRQ(XINT_EVT1_IRQn); //Enable Ex►

ternal Interrupt 1 source.

Loading...

Loading...