Reference Manual ADuCM356

REGISTER DETAILS: CLOCK ARCHITECTURE

analog.com Rev. A | 17 of 312

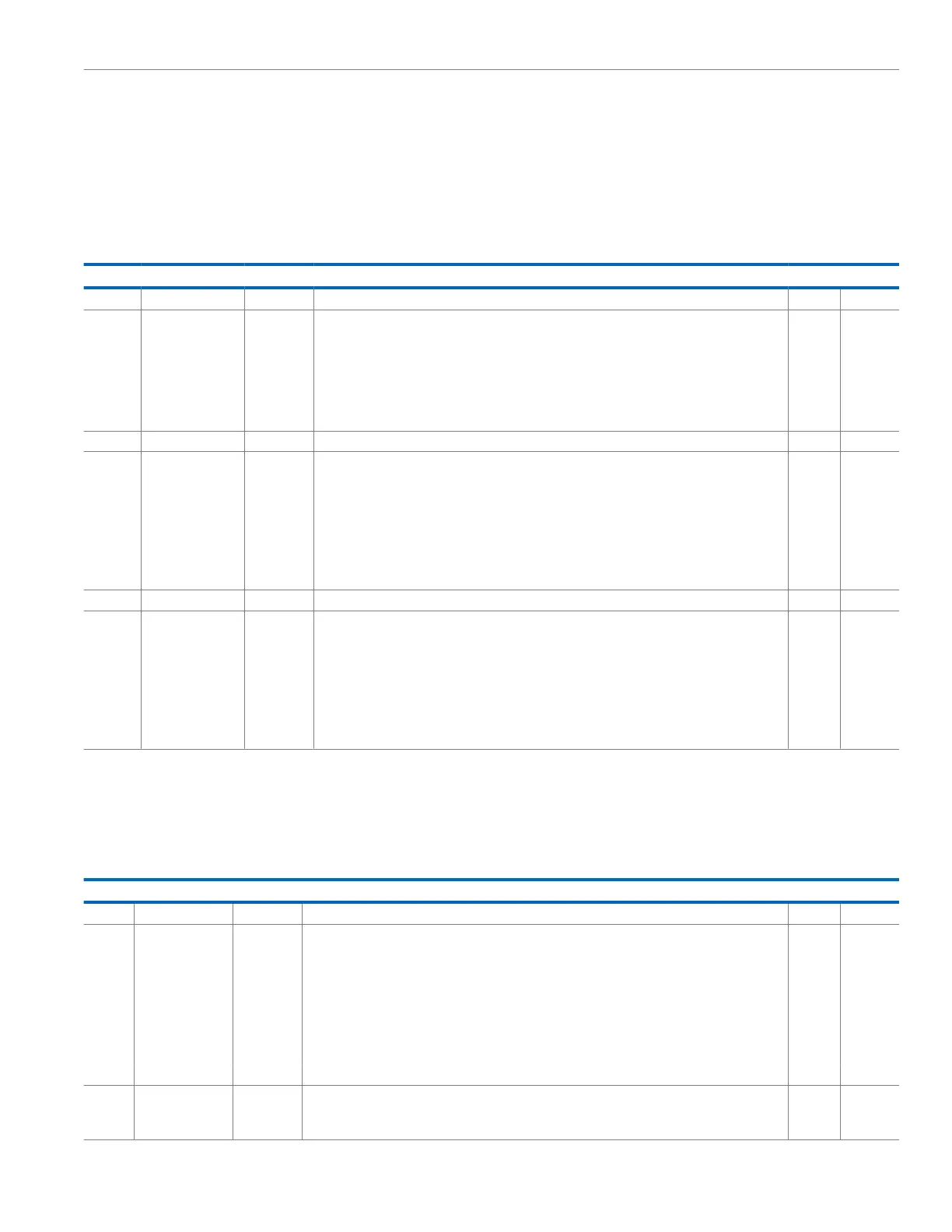

CLOCK DIVIDERS REGISTER

Address: 0x4004C304, Reset: 0x00100404, Name: CTL1

The clock dividers register is used to set the divide rates for the HCLK, PCLK, and ACLK dividers. This register can be written to at any time. All

unused bits are read only, returning a value of 0. Writing to unused bits has no effect.

Table 8. Bit Descriptions for CTL1

Bits Bit Name Settings Description Reset Access

[31:24] Reserved Reserved. 0x0 R

[23:16] ACLKDIVCNT ACLK Clock Divider. This bit determines the ACLK rate based on the equation ACLK = root

clock/ACLKDIVCNT. For example, if the root clock is 26 MHz and ACLKDIVCNT = 0x1, ACLK

operates at 26 MHz. The value of ACLKDIVCNT takes effect after a write access to this register and

typically takes one ACLK cycle. This register can be read at any time and can be written to at any

time. The value range is from 1 to 32. Values larger than 32 are saturated to 32. Value 0 and Value

1 have the same results as divided by 1. The default value of this register is configured such that

ACLK = 1.625 MHz.

0x10 R/W

[15:14] Reserved Reserved. 0x0 R

[13:8] PCLKDIVCNT PCLK Clock Divider. Determines the PCLK rate based on the equation PCLK = root clock/

PCLKDIVCNT. For example, if the root clock is 26 MHz and PCLKDIVCNT = 0x2, PCLK operates

at 13 MHz. The value of PCLKDIVCNT takes effect after a write access to this register and typically

takes 2 to 4 PCLK cycles. This register can be read at any time and can be written to at any time.

The value range is from 1 to 32. Values larger than 32 are saturated to 32. Value 0 and Value 1

have the same results as divided by 1. The default value of this register is configured such that

PCLK frequency = 6.5 MHz. It is recommended to only use the 0x1, 0x2, or 0x4 value and matching

PCLKDIVCNT with HCLKDIVCNT.

0x4 R/W

[7:6] Reserved Reserved. 0x0 R

[5:0] HCLKDIVCNT HCLK Divide Count. Determines the HCLK rate based on the equation: HCLK = root clock/

HCLKDIVCNT. For example, if the root clock is 26 MHz and HCLKDIVCNT = 0x1, HCLK operates

at 26 MHz. The value of HCLKDIVCNT takes effect after a write access to this register and typically

takes 2 to 4 PCLK cycles (not HCLK cycles). This register can be read at any time and can be

written to at any time. The value range is from 1 to 32. Values larger than 32 are saturated to 32.

Value 0 and Value 1 have the same results as divided by 1. The default value of this register is

configured such that HCLK = 6.5 MHz. It is recommended to only use the values 0x1, 0x2, or 0x4

and match HCLKDIVCNT with PCLKDIVCNT.

0x4 R/W

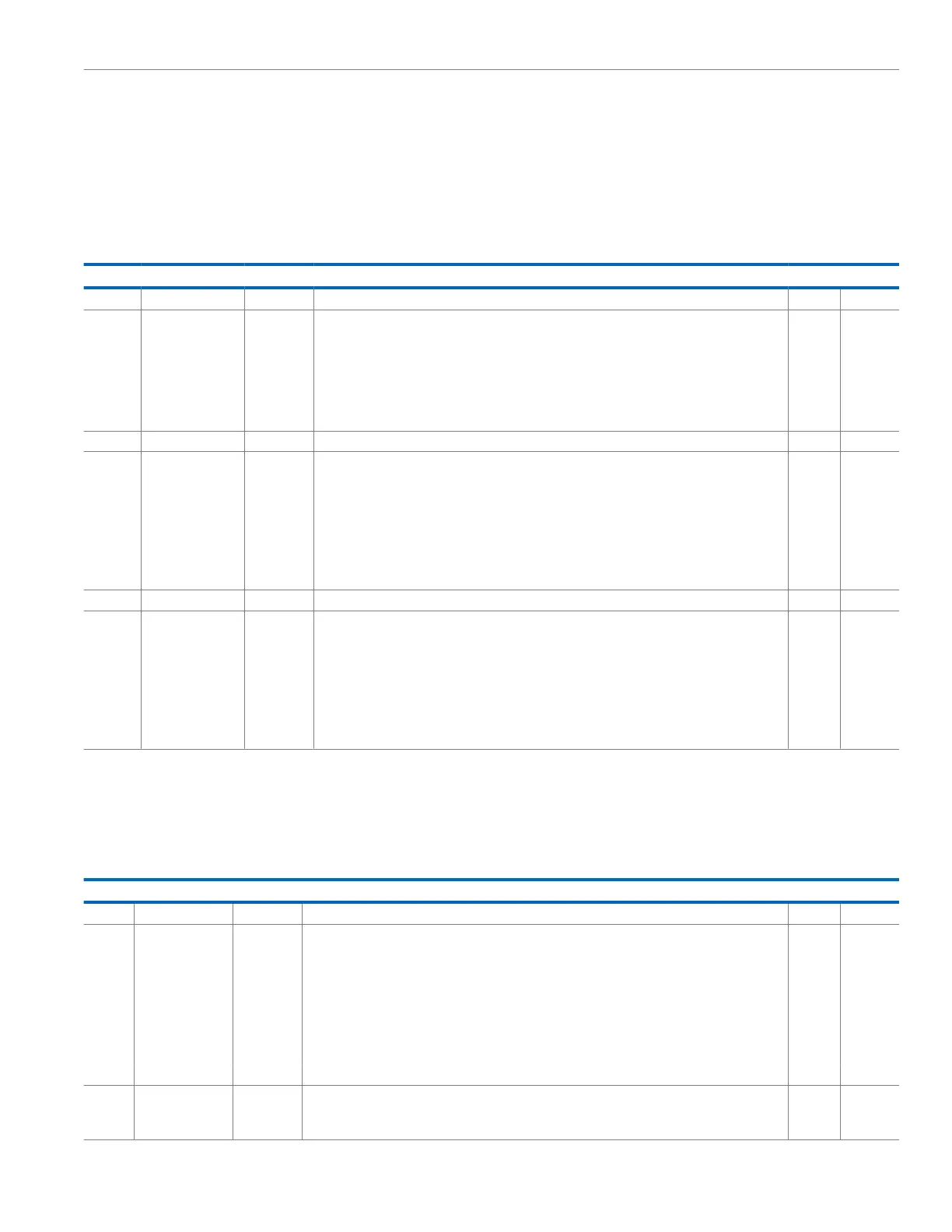

USER CLOCK GATING CONTROL REGISTER

Address: 0x4004C314, Reset: 0x0000001F, Name: CTL5

User clock gating control is used to control the clock gating to peripherals.

Table 9. Bit Descriptions for CTL5

Bits Bit Name Settings Description Reset Access

[31:6] Reserved Reserved. 0x0 R

5 PERCLKOFF Peripheral Clocks Off. This bit is used to disable all clocks connected to all peripherals. After setting

this bit, any read or write to any of the peripheral registers automatically resets PERCLKOFF to 0, and

that read or write transaction is honored. After setting PERCLKOFF = 1, if the user reads the CTL5

register, PERCLKOFF is automatically cleared and PERCLKOFF reads as 0. The user must ensure

that DMA transactions are done and no more transactions are expected from the DMA. Ensure that

the PERCLKOFF bit write is the last write and no writes or reads to any of peripheral registers are

performed after setting this bit. Otherwise, the PERCLKOFF bit clears.

0x0 R/W

0 Clocks to all peripherals are active.

1 Clocks to all peripherals are gated off.

4 GPIOCLKOFF GPIO Clock Control. This bit disables the GPIO clock and controls the gate on the ACLK out from

ACLK divider. This ACLK control is available in active mode and Flexi

™

mode. In hibernate mode, the

ACLK is always off and this bit has no effect. This bit does not automatically clear. Explicitly enable or

0x1 R/W

Loading...

Loading...