Reference Manual ADuCM356

REGISTER DETAILS: FLASH CACHE CONTROLLER (FLCC)

analog.com Rev. A | 199 of 312

ECC STATUS (ADDRESS) REGISTER

Address: 0x40018048, Reset: 0x00000000, Name: ECC_ADDR

This register is updated when ECC error or correction events occur. ECC error and correction events can generate interrupts if the appropriate

bits of the IEN register are selected, which generates a bus fault. This register records the address of the first ECC error or correction event

to generate an interrupt since reset or the last time the ECC status bits were cleared. If the status bits are cleared in the same cycle as a new

ECC event (selected to generate an IRQ), a new address is recorded and the status bits remain set.

Errors have priority over corrections. Two or more corrupt bits results in an error. A correction results in proper data being returned after a single

bit is corrected. If an error and a correction occur in the same cycle, this register reports the error address. When two of the same priority ECC

events occur (both errors or both corrections), the ICode bus has priority over DCode. As such, if both ICode and DCode buses generate the

same type of ECC event in the same cycle, the ICode address is stored in this register.

The register cannot be cleared except by reset. It always holds the address of the most recently reported ECC correction or error.

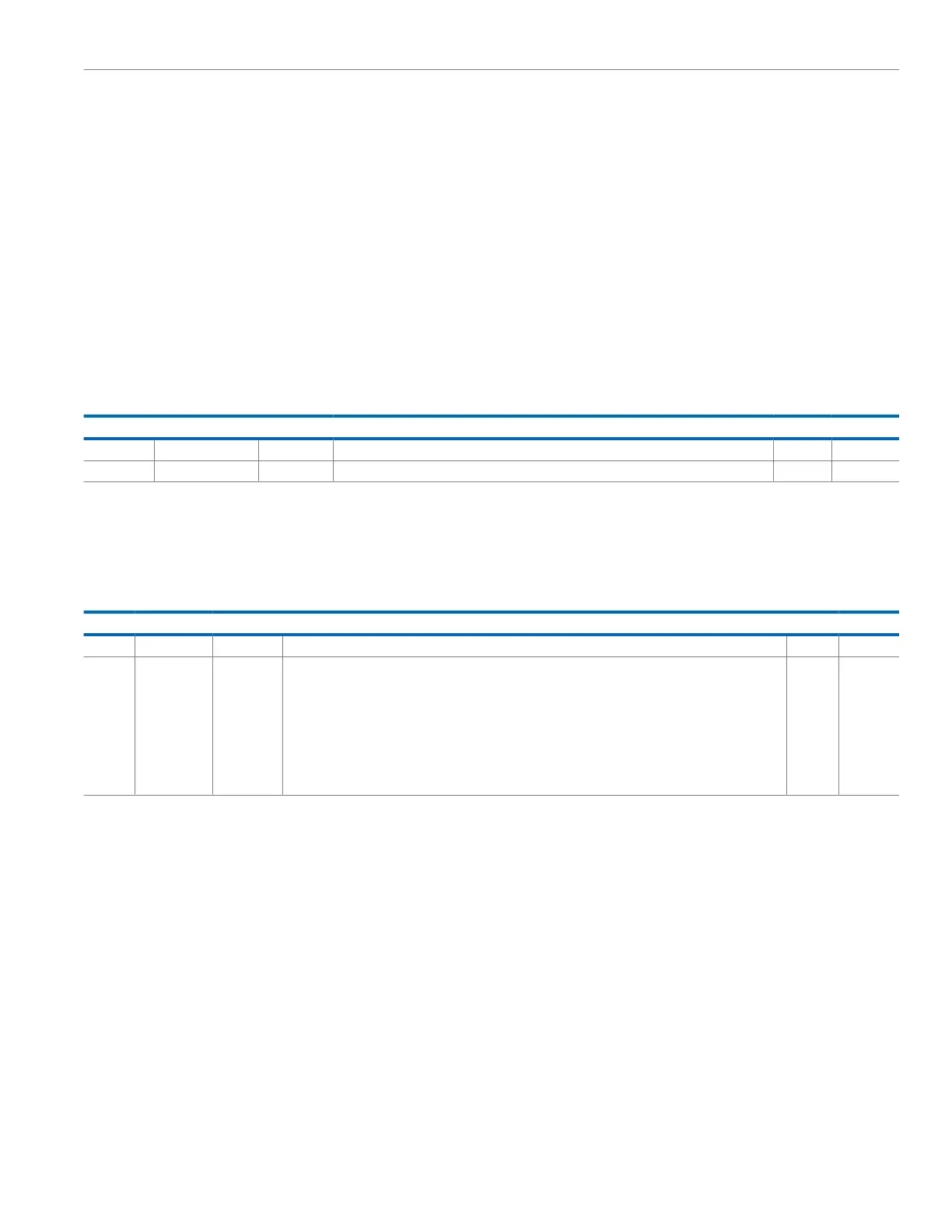

Table 240. Bit Descriptions for ECC_ADDR

Bits Bit Name Settings Description Reset Access

[31:19] Reserved Reserved. 0x0 R

[18:0] VALUE Address for Which ECC Error Is Detected. 0x0 R

ANALOG DEVICES FLASH SECURITY REGISTER

Address: 0x40018050, Reset: 0x00000000, Name: ADI_POR_SEC

This register resets only after a POR or an external reset.

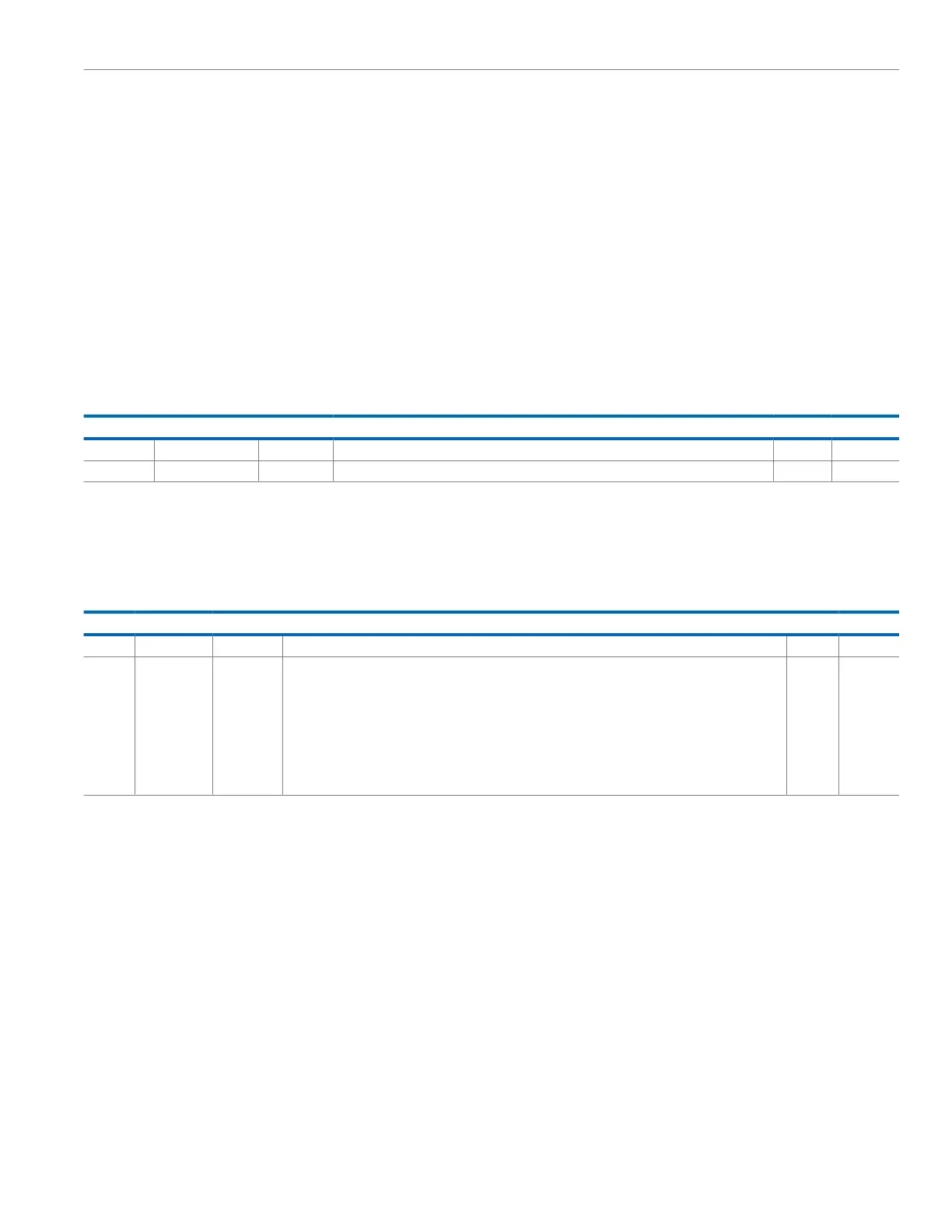

Table 241. Bit Descriptions for ADI_POR_SEC

Bits Bit Name Settings Description Reset Access

[31:1] Reserved Reserved. 0x0 R

0 SECURE Prevents Read or Write to User Space. Set this bit to prevent a read or write access to user space. This

bit is sticky when set and requires a user key. When set, this bit cannot be cleared without resetting the

device using a POR or external reset. This bit plays a direct role in user space security enforcement.

When set, this bit prevents access to user space. DCode reads return bus faults with the data bus =

0. ICode reads return bus faults with the data bus = 0. APB writes are denied, and the flash content is

unchanged. When set, the user can still perform mass erase and page erase operations. However, the

WRPROT register still applies and only unprotected pages can be erased. Mass erase is not allowed if

any pages are protected. See the Security Features section for more information.

0x0 R/W1S

Loading...

Loading...