Reference Manual ADuCM356

REGISTER SUMMARY: ADC CIRCUIT

analog.com Rev. A | 61 of 312

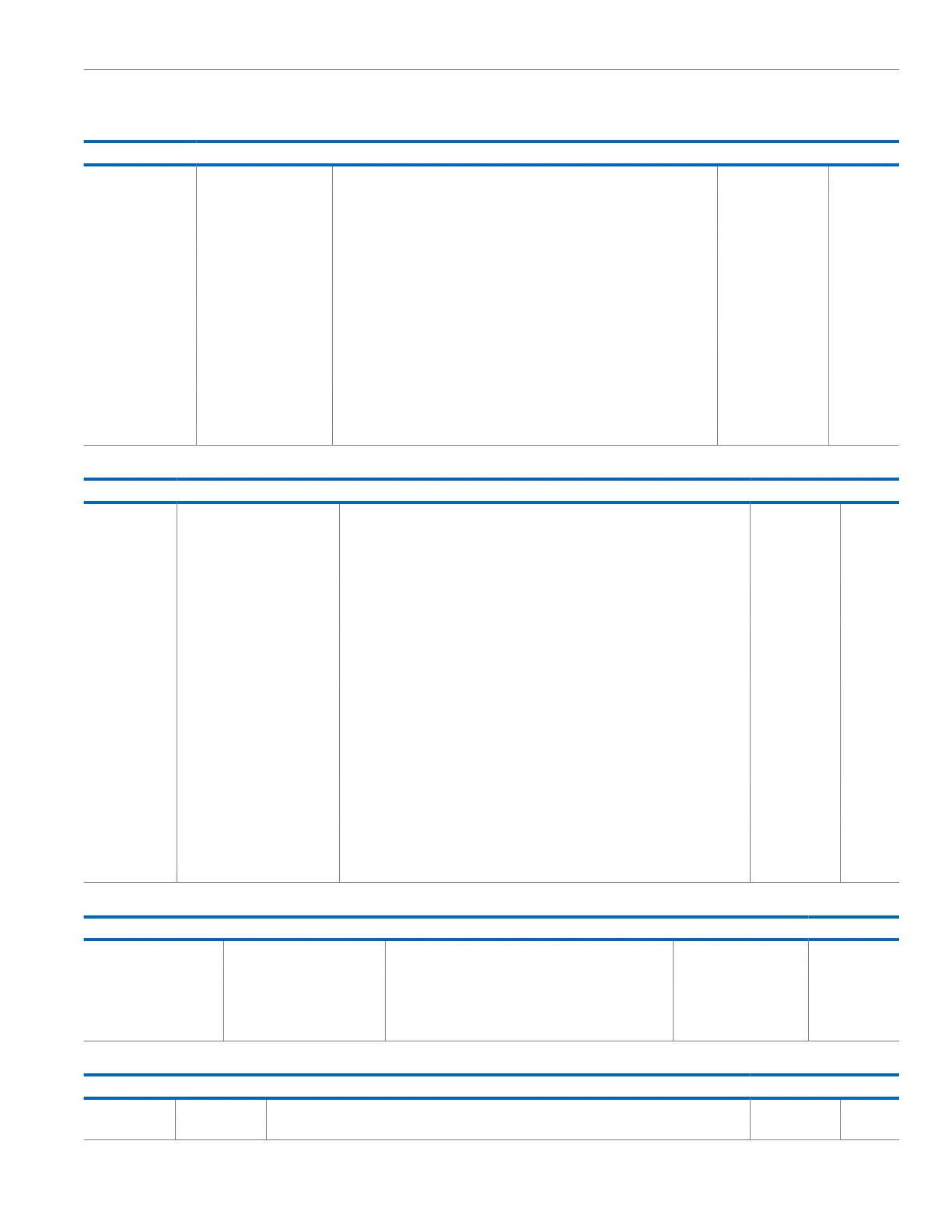

Table 58. ADC Control Register Summary

Address Name Description Reset Access

0x400C21A8 ADCCON ADC configuration register 0x00000000 R/W

0x400C2044 ADCFILTERCON ADC output filters configuration 0x00000301 R/W

0x400C2074 ADCDAT Raw result 0x00000000 R/W

0x400C2078 DFTREAL DFT result, real part 0x00000000 R/W

0x400C207C DFTIMAG DFT result, imaginary part 0x00000000 R/W

0x400C2080 SINC2DAT Sinc2 and supply rejection filter result 0x00000000 R/W

0x400C2084 TEMPSENSDAT0 Temperature Sensor 0 result 0x00000000 R/W

0x400C2088 ADCINTIEN Analog capture interrupt enable 0x00000000 R/W

0x400C2098 ADCINTSTA Analog capture interrupt 0x00000000 R/W

0x400C20D0 DFTCON AFE DSP configuration 0x00000090 R/W

0x400C2174 TEMPCON0 Temperature Sensor 0 configuration 0x00000000 R/W

0x400C2180 BUFSENCON High-power and low-power buffer control 0x00000037 R/W

0x400C21F0 REPEATADCCNV Number of repeat ADC conversions 0x00000160 R/W

0x400C238C ADCBUFCON Buffer configuration 0x005F3D00 R/W

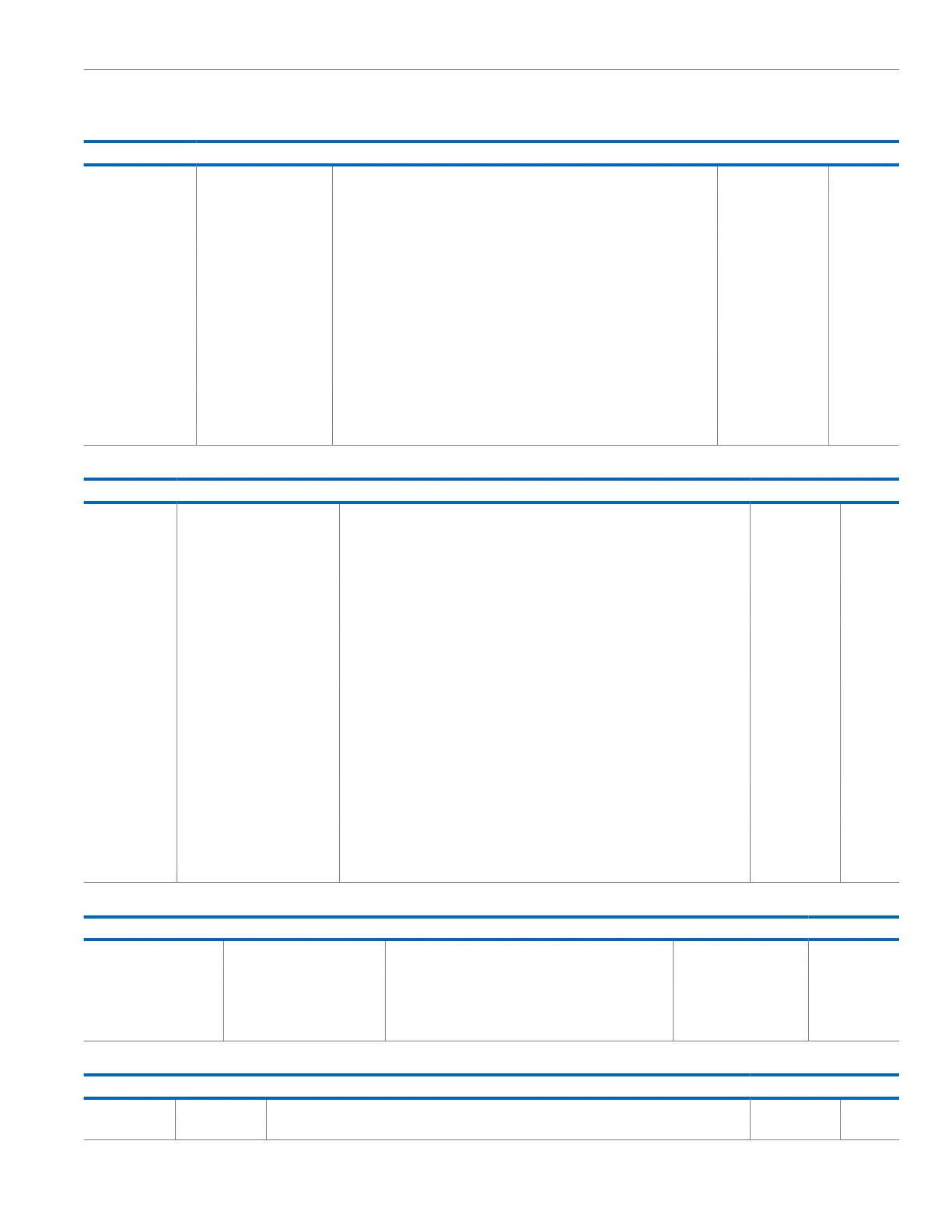

Table 59. ADC Calibration Register Summary

Address Name Description Reset Access

0x400C2230 CALDATLOCK Calibration lock 0x00000000 R/W

0x400C2288 ADCOFFSETLPTIA0 Offset calibration low-power TIA0 channel 0x00000000 R/W

0x400C228C ADCGNLPTIA0 Gain calibration for low-power TIA0 channel 0x00004000 R/W

0x400C22C0 ADCOFFSETLPTIA1 Offset calibration low-power TIA1 channel 0x00000000 R/W

0x400C22C4 ADCGNLPTIA1 Gain calibration for low-power TIA1 channel 0x00004000 R/W

0x400C2234 ADCOFFSETHSTIA Offset calibration high-speed TIA channel 0x00000000 R/W

0x400C2284 ADCGNHSTIA Gain calibration for high-speed TIA channel 0x00004000 R/W

0x400C2244 ADCOFFSETGN1 Offset calibration voltage channel (PGA gain = 1) 0x00000000 R/W

0x400C2240 ADCGAINGN1 Gain calibration voltage input channel (PGA gain = 1) 0x00004000 R/W

0x400C22CC ADCOFFSETGN1P5 Offset calibration voltage input channel (PGA gain = 1.5) 0x00000000 R/W

0x400C2270 ADCGAINGN1P5 Gain calibration voltage input channel (PGA gain = 1.5) 0x00004000 R/W

0x400C22C8 ADCOFFSETGN2 Offset calibration voltage input channel (PGA gain = 2) 0x00000000 R/W

0x400C2274 ADCGAINGN2 Gain calibration voltage input channel (PGA gain = 2) 0x00004000 R/W

0x400C22D4 ADCOFFSETGN4 Offset calibration voltage input channel (PGA gain = 4) 0x00000000 R/W

0x400C2278 ADCGAINGN4 Gain calibration voltage input channel (PGA gain = 4) 0x00004000 R/W

0x400C22D0 ADCOFFSETGN9 Offset calibration voltage input channel (PGA gain = 9) 0x00000000 R/W

0x400C2298 ADCGAINGN9 Gain calibration voltage input channel (PGA gain = 9) 0x00004000 R/W

0x400C223C ADCOFFSETTEMPSENS0 Offset calibration temperature sensor Channel 0 0x00000000 R/W

0x400C2238 ADCGAINTEMPSENS0 Gain calibration temperature sensor Channel 0 0x00004000 R/W

Table 60. ADC Digital Postprocessing Register Summary (Optional)

Address Name Description Reset Access

0x400C20A8 ADCMIN Minimum value check 0x00000000 R/W

0x400C20AC ADCMINSM Minimum slow moving value 0x00000000 R/W

0x400C20B0 ADCMAX Maximum value check 0x00000000 R/W

0x400C20B4 ADCMAXSMEN Maximum slow moving 0x00000000 R/W

0x400C20B8 ADCDELTA Delta check 0x00000000 R/W

Table 61. ADC Statistics Register Summary (Optional)

Address Name Description Reset Access

0x400C21C4 STATSCON Statistics module configuration 0x00000000 R/W

0x400C21C8 STATSMEAN Mean output 0x00000000 R

Loading...

Loading...