Reference Manual ADuCM356

REGISTER DETAILS: DMA

analog.com Rev. A | 173 of 312

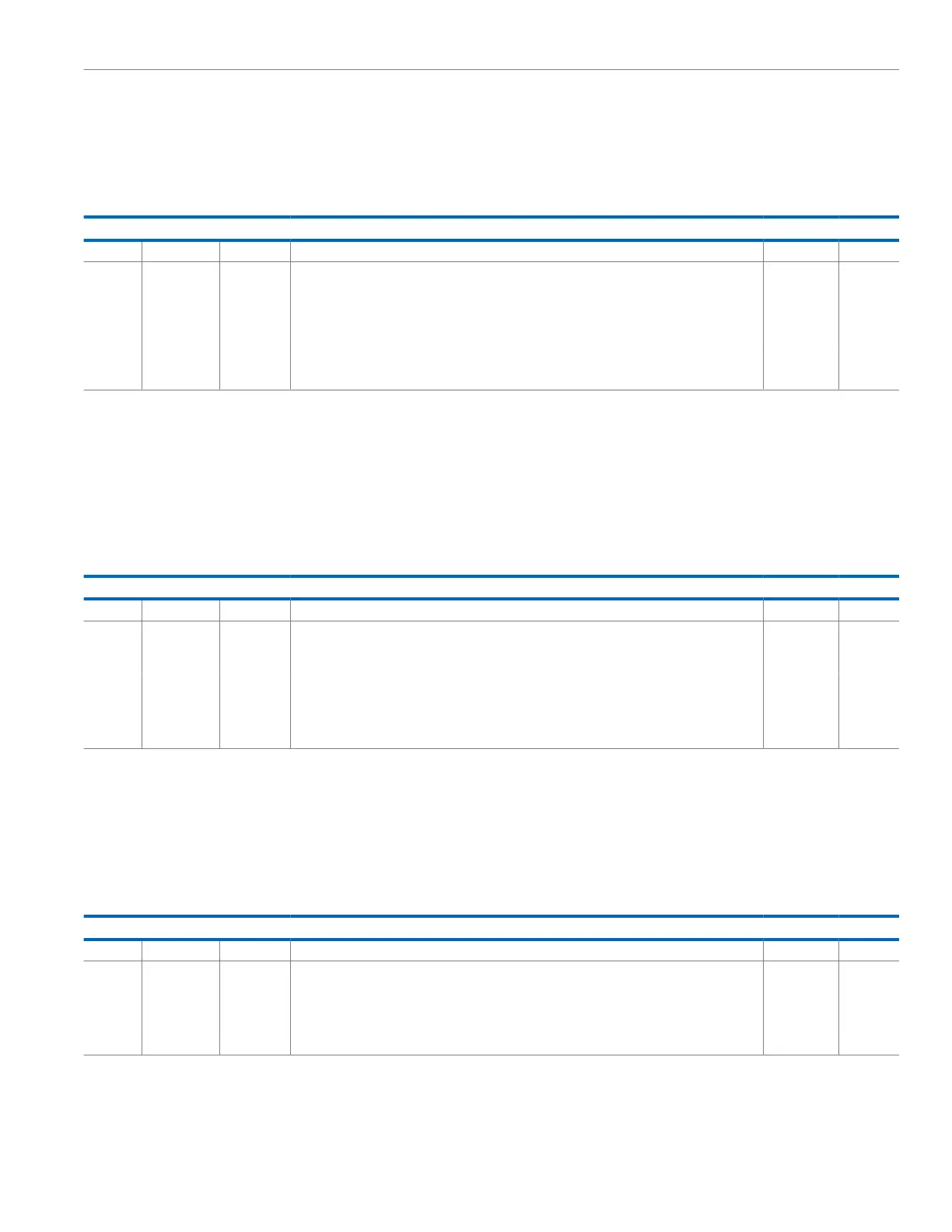

CHANNEL ENABLE CLEAR REGISTER

Address: 0x4001002C, Reset: 0x00000000, Name: EN_CLR

Table 205. Bit Descriptions for EN_CLR

Bits Bit Name Settings Description Reset Access

[31:24] Reserved Reserved. 0x00 R

[23:0] CHAN Disable DMA Channels. This register allows the disabling of DMA channels. This register is write

only. Each bit of the register represents the corresponding channel number in the DMA controller.

The controller disables a channel automatically by setting the appropriate bit when it completes the

DMA cycle. Set the appropriate bit to disable the corresponding channel. Bit 0 corresponds to DMA

Channel 0. Bit M – 1 corresponds to DMA Channel M – 1.

0x000000 W

0 No effect. Use the EN_SET register to enable the channel.

1 Disables Channel C.

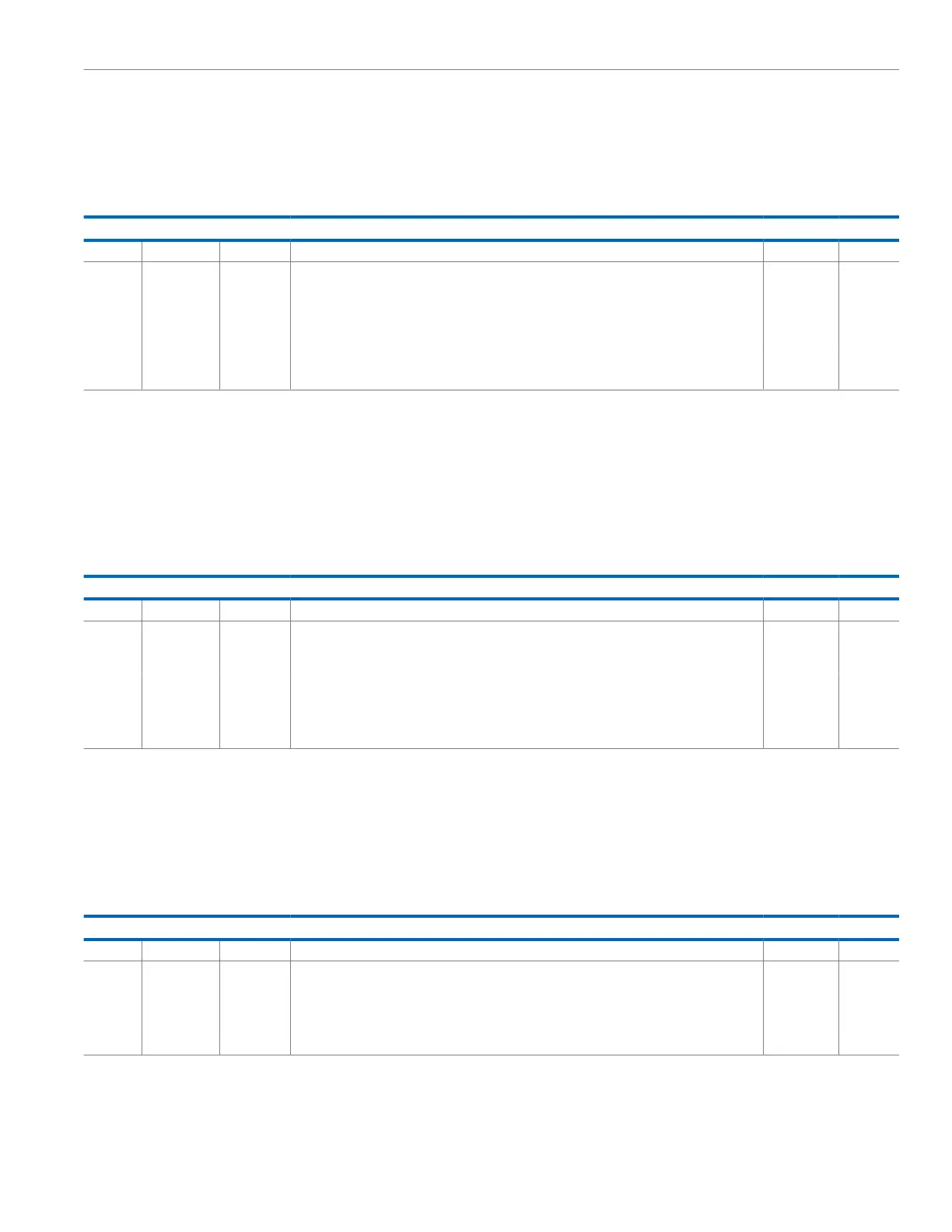

CHANNEL PRIMARY ALTERNATE SET REGISTER

Address: 0x40010030, Reset: 0x00000000, Name: ALT_SET

The ALT_SET register enables the user to configure the appropriate DMA channel to use the alternate control data structure. Reading the

register returns the status of which data structure is in use for the corresponding DMA channel. Each bit of the register represents the

corresponding channel number in the DMA controller. The DMA controller sets and clears these bits automatically as necessary for ping pong,

memory scatter gather, and peripheral scatter gather transfers.

Table 206. Bit Descriptions for ALT_SET

Bits Bit Name Settings Description Reset Access

[31:24] Reserved Reserved. 0x00 R

[23:0] CHAN Control Structure Status and Select Alternate Structure. Returns the channel control data structure

status or selects the alternate data structure for the corresponding DMA channel. Bit 0 corresponds

to DMA Channel 0. Bit M – 1 corresponds to DMA Channel M – 1.

0x000000 R/W

0 When read as 0, DMA Channel C uses the primary data structure. When written as 0, no effect.

Use the ALT_CLR register to set Channel C to 0.

1 When read as 1, DMA Channel C uses the alternate data structure. When written as 1, the

alternate data structure for Channel C is selected.

CHANNEL PRIMARY ALTERNATE CLEAR REGISTER

Address: 0x40010034, Reset: 0x00000000, Name: ALT_CLR

The ALT_CLR write only register enables the user to configure the appropriate DMA channel to use the primary control data structure. Each bit

of the register represents the corresponding channel number in the DMA controller. The DMA controller sets and clears these bits automatically

as necessary for ping pong, memory scatter gather, and peripheral scatter gather transfers.

Table 207. Bit Descriptions for ALT_CLR

Bits Bit Name Settings Description Reset Access

[31:24] Reserved Reserved. 0x00 R

[23:0] CHAN Select Primary Data Structure. Set the appropriate bit to select the primary data structure for the

corresponding DMA channel. Bit 0 corresponds to DMA Channel 0. Bit M – 1 corresponds to DMA

Channel M – 1.

0x000000 W

0 No effect. Use the ALT_SET register to select the alternate data structure.

1 Selects the primary data structure for Channel C.

CHANNEL PRIORITY SET REGISTER

Address: 0x40010038, Reset: 0x00000000, Name: PRI_SET

Loading...

Loading...