Reference Manual ADuCM356

REGISTER DETAILS: CLOCK ARCHITECTURE

analog.com Rev. A | 22 of 312

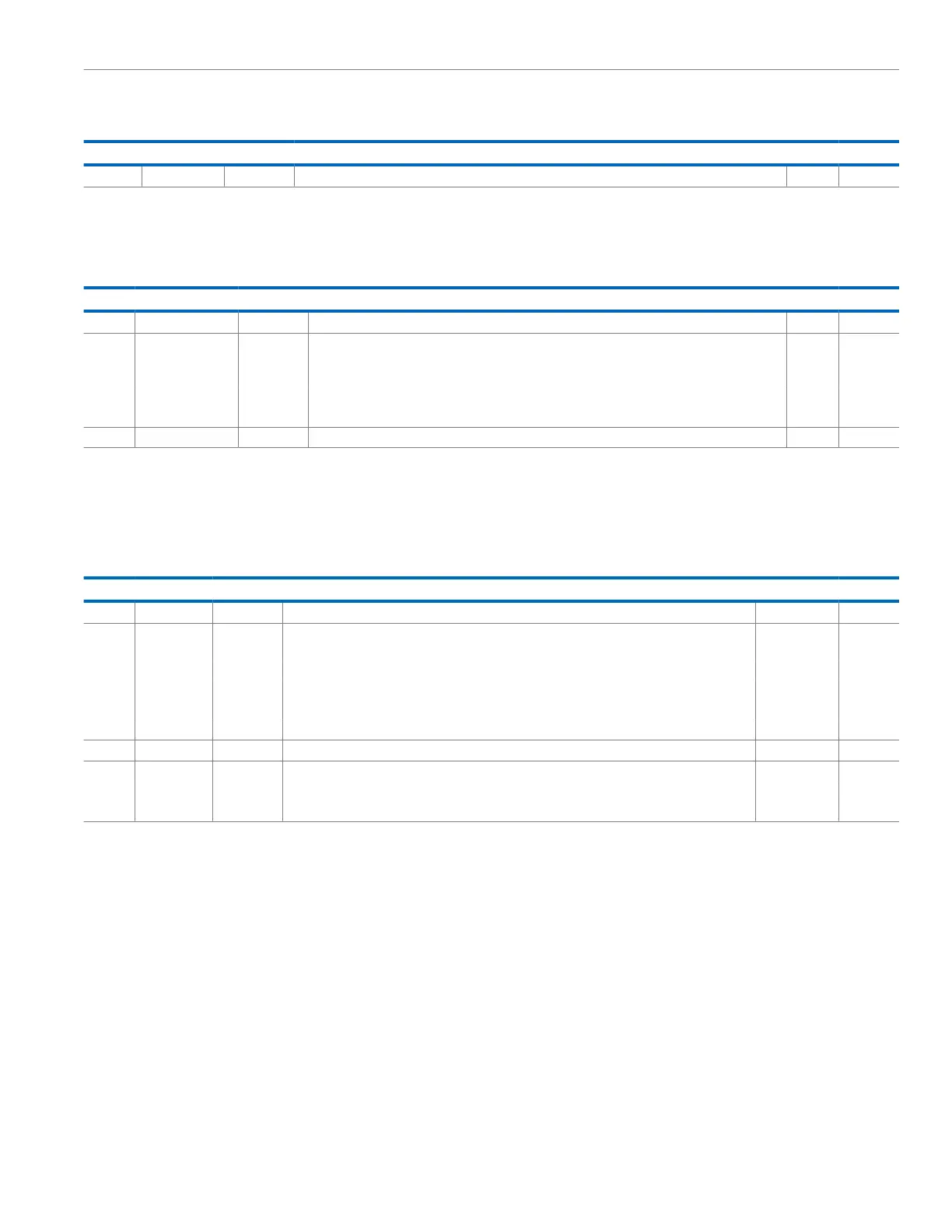

Table 18. Bit Descriptions for OSCCON (Continued)

Bits Bit Name Settings Description Reset Access

1 The low frequency oscillator is enabled.

HIGH-POWER OSCILLATOR CONFIGURATION REGISTER

Address: 0x400C20BC, Reset: 0x00000024, Name: HPOSCCON

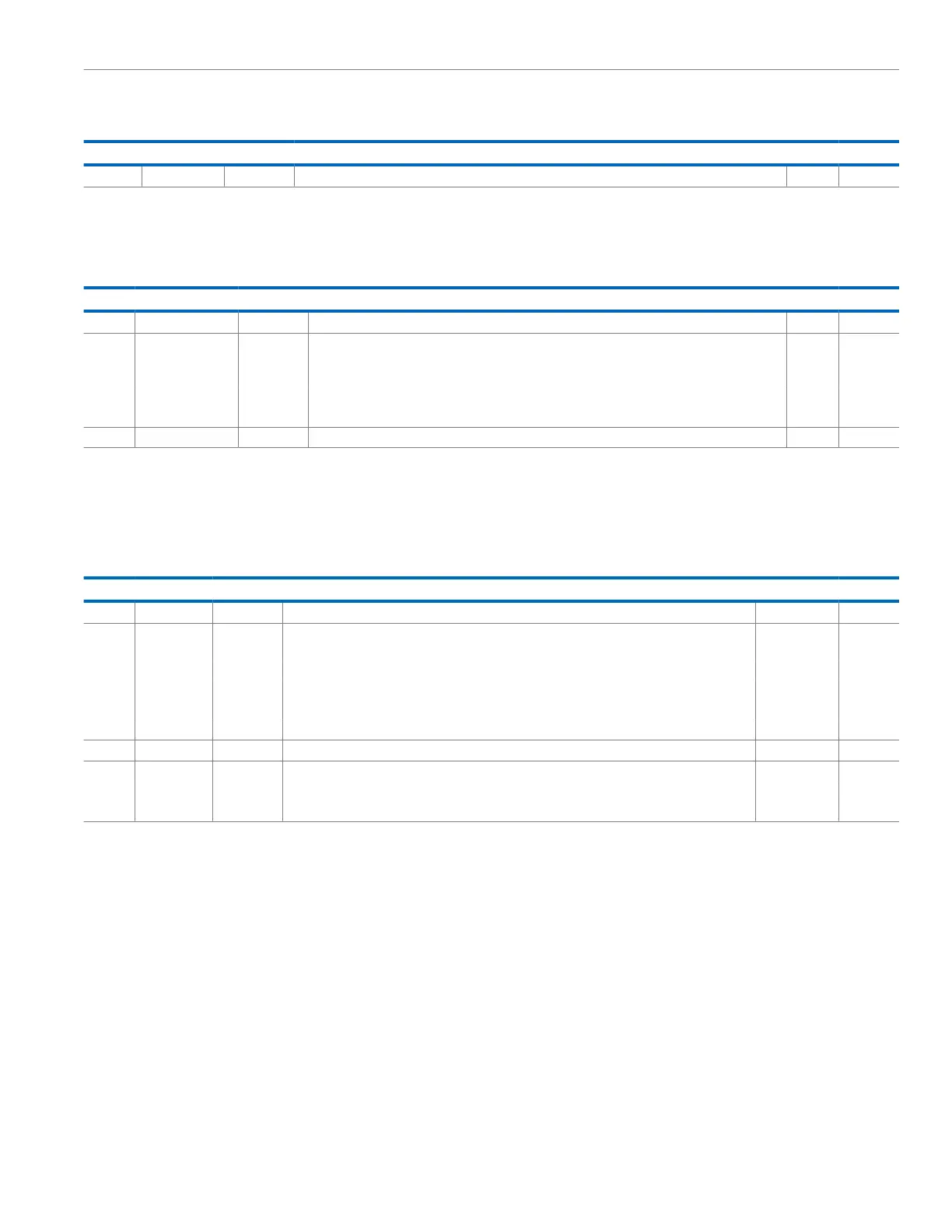

Table 19. Bit Descriptions for HPOSCCON

Bits Bit Name Settings Description Reset Access

[31:3] Reserved Reserved. 0x0 R

2 CLK32MHZEN 16 MHz or 32 MHz Output Selector Signal. Select an output of 32 MHz or 16 MHz. The ADC can

run at 32 MHz, but the system clock cannot run at 32 MHz. Divide the system clock by 2 first before

switching the oscillator to 32 MHz. Refer to CLKCON0, Bits[5:0].

0x1 R/W

0 Select 32 MHz output.

1 Select 16 MHz output.

[1:0] Reserved Reserved. 0x0 R

POWER MODE CONFIGURATION REGISTER

Address: 0x400C22F0, Reset: 0x00000000, Name: PMBW

This register configures the high and low-power system mode for the high-speed DAC and ADC circuits.

Table 20. Bit Descriptions for PMBW

Bits Bit Name Settings Description Reset Access

[31:4] Reserved Reserved. 0x0000000 R

[3:2] SYSBW Configure System Bandwidth. Configures the bandwidth of the high-speed DAC reconstruction filter

and the ADC antialias filter.

0x0 R/W

00 Reserved.

01 50 kHz, −3 dB bandwidth.

10 100 kHz, −3 dB bandwidth.

11 250 kHz, −3 dB bandwidth.

1 Reserved Reserved. 0x0 R

0 SYSHP Set High-Speed DAC and ADC in High-Power Mode. 0x0 R/W

0 Low-power mode. Clear this bit for impedance measurements <80 kHz.

1 High-power mode. Set this bit for impedance measurements >80 kHz.

Loading...

Loading...