Reference Manual ADuCM356

REGISTER DETAILS: DMA

analog.com Rev. A | 171 of 312

STATUS REGISTER

Address: 0x40010000, Reset: 0x00180000, Name: STAT

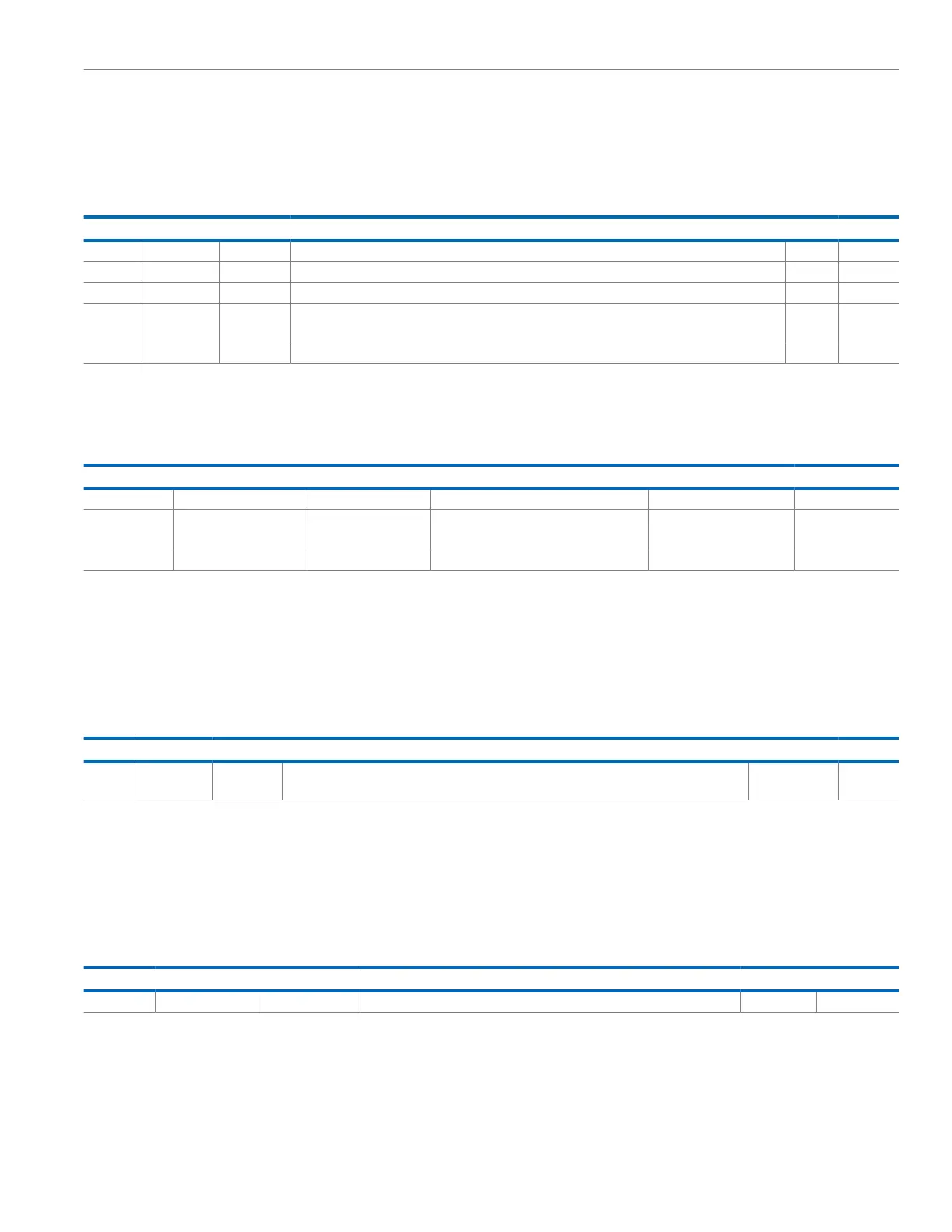

Table 197. Bit Descriptions for STAT

Bits Bit Name Settings Description Reset Access

[31:21] Reserved Reserved. 0x000 R

[20:16] CHANM1 Number of Available DMA Channels Minus 1. With 24 channels available, the register reads back 0x17. 0x18 R

[15:1] Reserved Reserved. 0x000 R

0 MEN Enable Status Of The Controller. 0x0 R

0 Controller is disabled.

1 Controller is enabled.

CONFIGURATION REGISTER

Address: 0x40010004, Reset: 0x00000000, Name: CFG

Table 198. Bit Descriptions for CFG

Bits Bit Name Settings Description Reset Access

[31:1] Reserved Reserved. 0x0000000 R

0 MEN Controller Enable. 0x0 W

0 Disable controller.

1 Enable controller.

CHANNEL PRIMARY CONTROL DATA BASE POINTER REGISTER

Address: 0x40010008, Reset: 0x00000000, Name: PDBPTR

The PDBPTR register must be programmed to point to the channel primary control data base pointer in the system memory. The amount of

system memory that must be assigned to the DMA controller depends on the number of DMA channels used and whether the alternate channel

control data structure is used. This register cannot be read when the DMA controller is in the reset state.

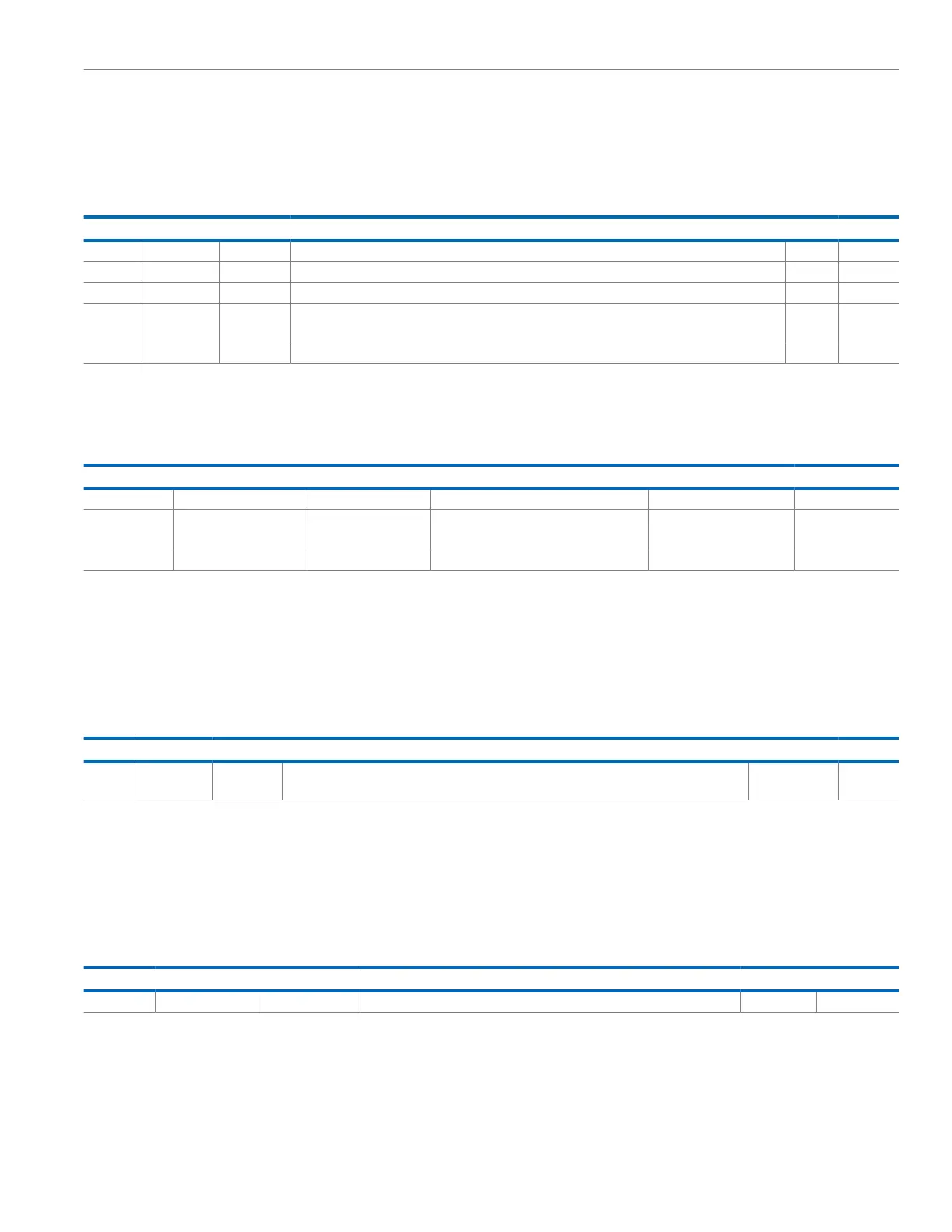

Table 199. Bit Descriptions for PDBPTR

Bits Bit Name Settings Description Reset Access

[31:0] ADDR Pointer to the Base Address of the Primary Data Structure. 5 + log

2

M LSBs are reserved and

must be written as 0, where M is number of channels.

0x00000000 R/W

CHANNEL ALTERNATE CONTROL DATA BASE POINTER REGISTER

Address: 0x4001000C, Reset: 0x00000200, Name: ADBPTR

The ADBPTR read only register returns the base address of the alternate channel control data structure. This register removes the necessity for

application software to calculate the base address of the alternate data structure. This register cannot be read when the DMA controller is in the

reset state.

Table 200. Bit Descriptions for ADBPTR

Bits Bit Name Settings Description Reset Access

[31:0] ADDR Base Address of the Alternate Data Structure. 0x200 R

CHANNEL SOFTWARE REQUEST REGISTER

Address: 0x40010014, Reset: 0x00000000, Name: SWREQ

The SWREQ register enables the generation of a software DMA request. Each bit of the register represents the corresponding channel number

in the DMA controller. M is the number of DMA channels.

Loading...

Loading...