Reference Manual ADuCM356

REGISTER DETAILS: I

2

C

analog.com Rev. A | 230 of 312

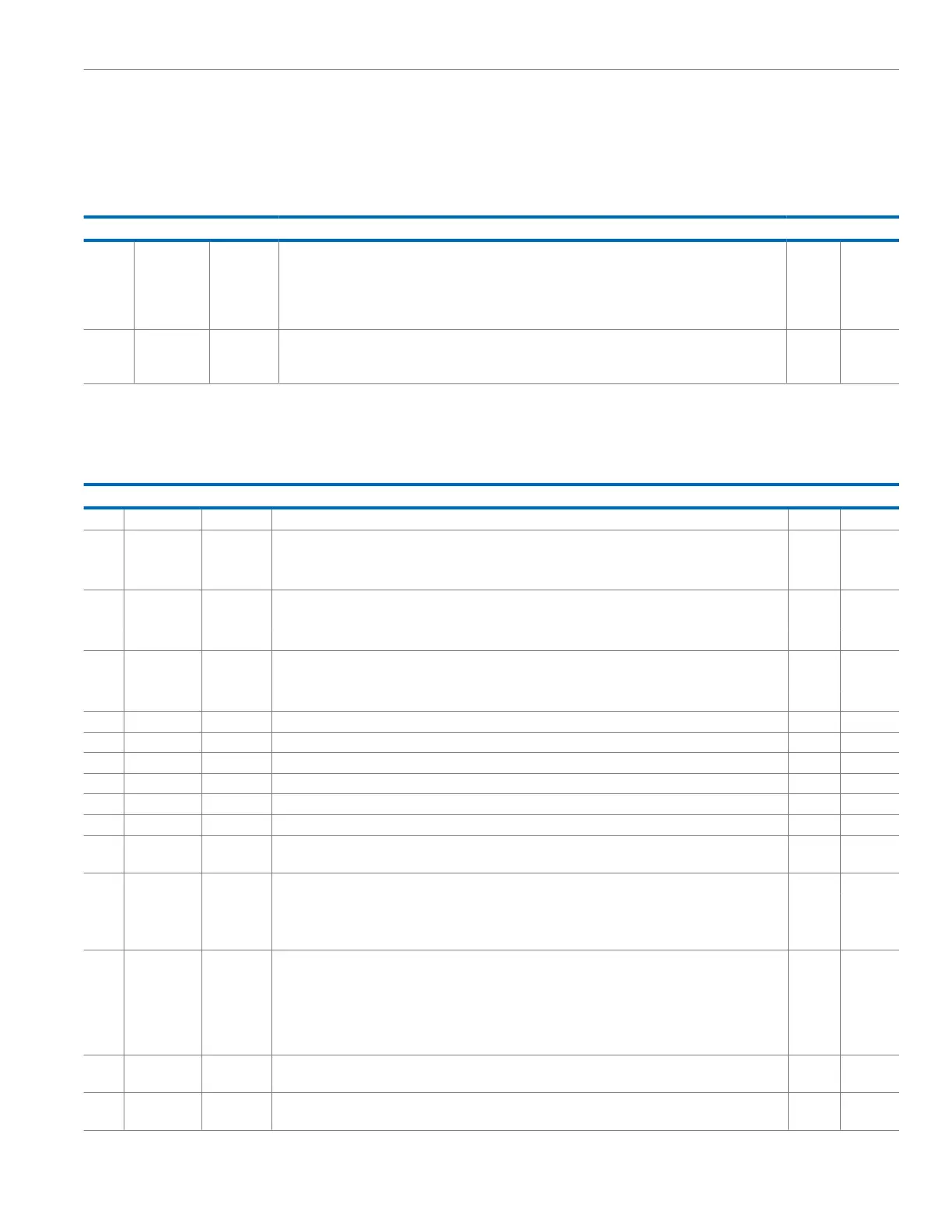

SERIAL CLOCK PERIOD DIVISOR REGISTER

Address: 0x40003024, Reset: 0x1F1F, Name: DIV

Table 291. Bit Descriptions for DIV

Bits Bit Name Settings Description Reset Access

[15:8] HIGH Serial Clock High Time. This register controls the clock high time. The PCLK drives the timer. To derive the

required high time, calculate: High = (REQD_HIGH_TIME/PCLK_PERIOD) – 2. For example, to generate a

400 kHz I2C_SCL with a low time of 1300 ns and a high time of 1200 ns, with a core clock frequency of 26

MHz, Low = 1300 ns/38 ns − 1 = 0x21 (33 decimal). High = 1200 ns/38 ns − 2 = 0x1D (29 decimal). This

register is reset to 0x1F, which gives an I2C_SCL high time of 33 PCLK cycles.

0x1F R/W

[7:0] LOW Serial Clock Low Time. This register controls the clock low time. The PCLK drives the timer. To derive the

required low time, calculate: Low = (REQD_LOW_TIME/PCLK_PERIOD) – 1. This register is reset to 0x1F,

which gives an I2C_SCL low time of 32 PCLK cycles.

0x1F R/W

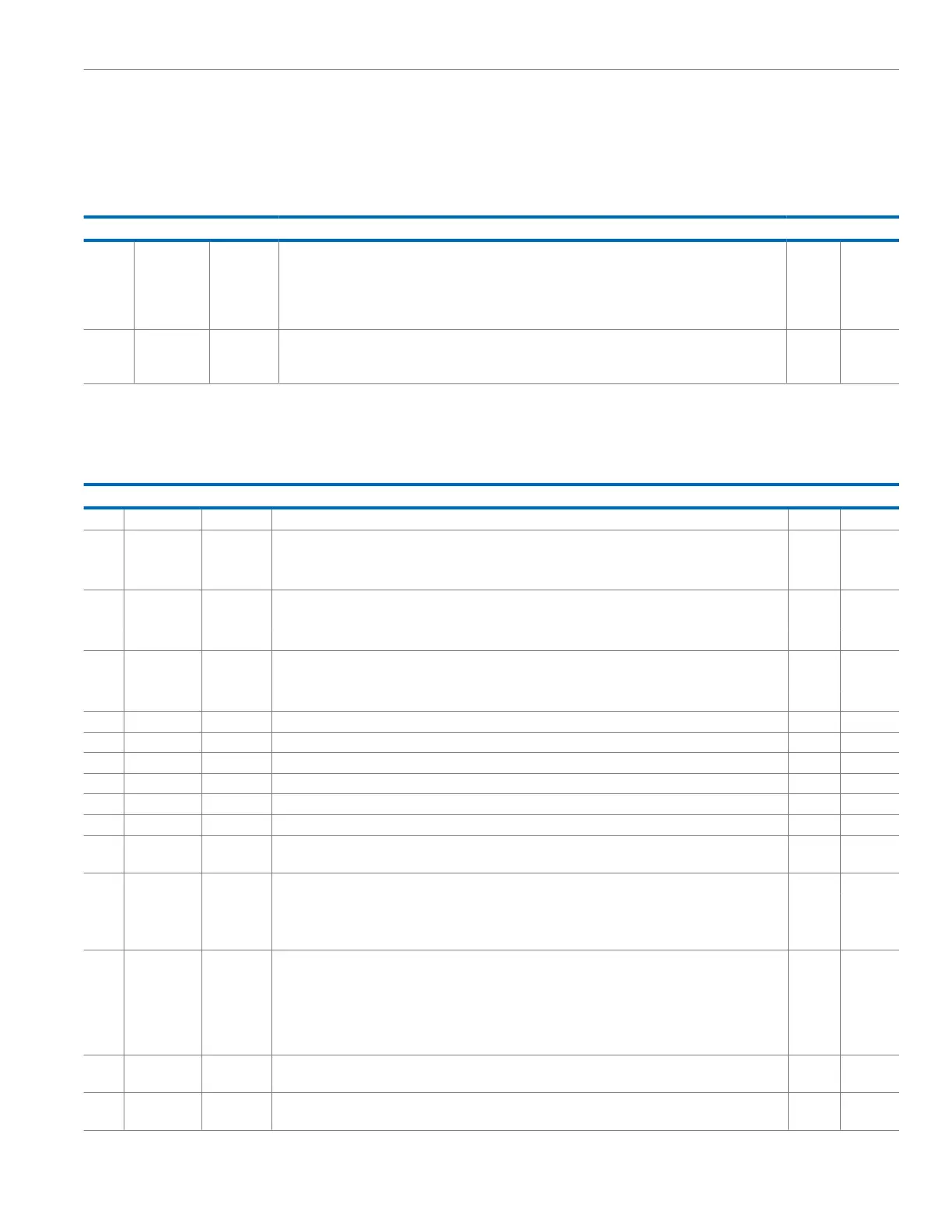

TARGET CONTROL REGISTER

Address: 0x40003028, Reset: 0x0000, Name: SCTL

Table 292. Bit Descriptions for SCTL

Bits Bit Name Settings Description Reset Access

15 Reserved Reserved. 0x0 R

14 STXDMA Enable Target Transmit DMA Request. 0x0 R/W

0 Disable DMA mode.

1 Enable I

2

C target DMA receive requests.

13 SRXDMA Enable target Receive DMA Request. 0x0 R/W

0 Disable DMA mode.

1 Enable I

2

C target DMA receive requests.

12 IENREPST Repeated Start Interrupt Enable. 0x0 R/W

0 Interrupt not generated when the SSTAT, Bit 13 asserts.

1 Generate interrupt when the SSTAT, Bit 13 asserts.

11 Reserved Reserved. 0x0 R/W

10 IENSTX Target Transmit Request Interrupt Enable. 0x0 R/W

9 IENSRX Target Receive Request Interrupt Enable. 0x0 R/W

8 IENSTOP Stop Condition Detected Interrupt Enable. 0x0 R/W

7 NACK No Acknowledge Next Communication. If this bit is set, the next communication is not acknowledged. 0x0 R/W

6 Reserved Reserved. Write 0 to this bit. 0x0 R/W

5 EARLYTXR Early Transmit Request Mode. Setting this bit enables a transmit request immediately after the positive edge

of the direction bit I2C_SCL clock pulse.

0x0 R/W

4 GCSBCLR General Call Status Bit Clear. 0x0 W

0 Does not clear general call status and general call ID bits.

1 Clear general call status and general call ID bits. The general call status and general call ID bits are not reset

by anything other than a write to this bit or a full reset.

3 HGCEN Hardware General Call Enable. When this bit and the general call enable bit are set, after receiving a general

call, the device and a data byte check the contents of the ALT register against the receive shift register. If

these registers match, the device has received a hardware general call. This call is used if a device requires

urgent attention from an initiator device without knowing which initiator to which to turn. This is a to whom it

may concern call. The device that requires attention embeds its own address into the message. The LSB of

the ALT register must always be written to a 1, as per the I

2

C January 2000 specification.

0x0 R/W

2 GCEN General Call Enable. This bit enables the I

2

C target to acknowledge an I

2

C general call, Address 0x00

(write).

0x0 R/W

1 ADR10EN Enabled 10-Bit Addressing. If this bit is clear, the target can support four target addresses, programmed in

the ID0 register to the ID3 register. When this bit is set, 10-bit addressing is enabled. One 10-bit address is

0x0 R/W

Loading...

Loading...