Reference Manual ADuCM356

REGISTER DETAILS: I

2

C

analog.com Rev. A | 229 of 312

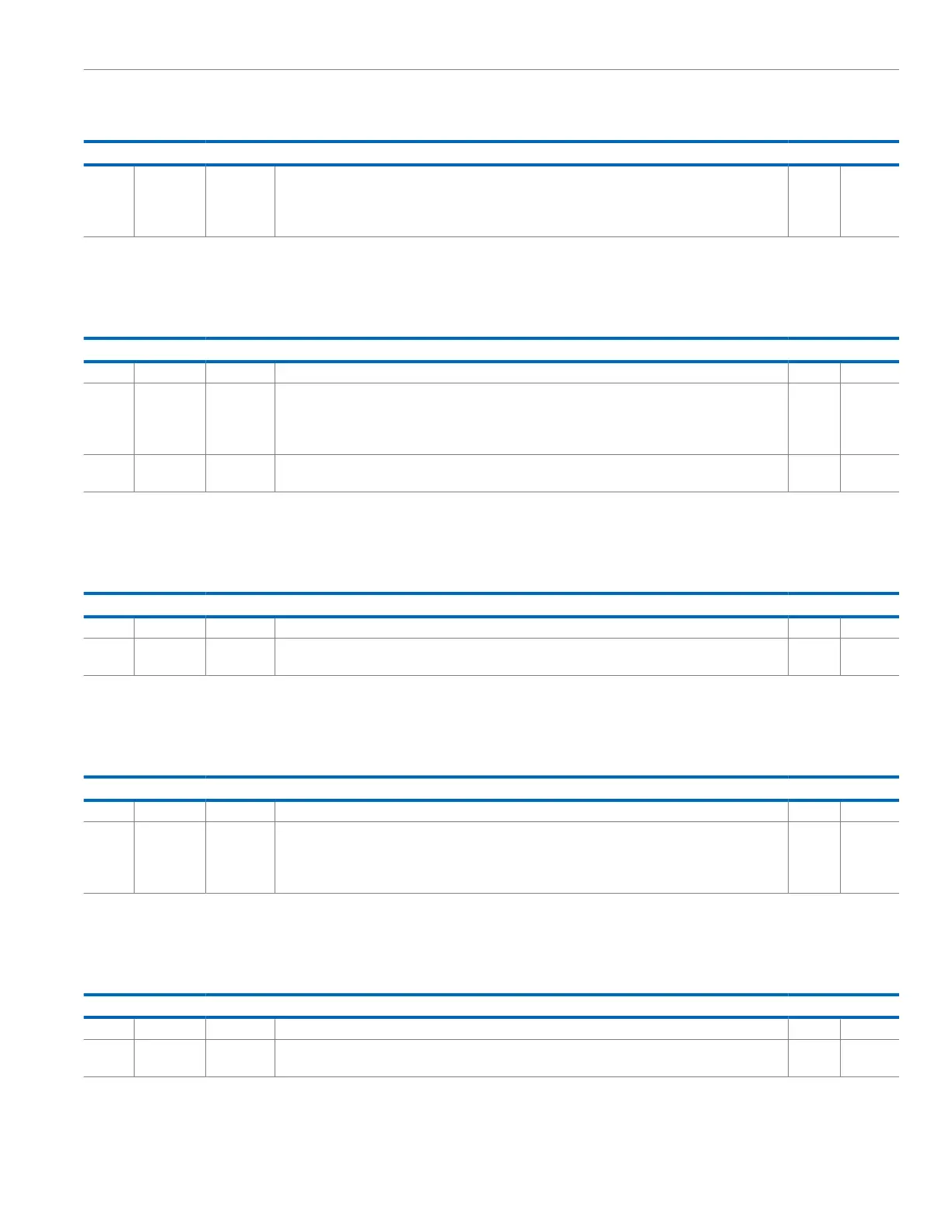

Table 286. Bit Descriptions for MTX (Continued)

Bits Bit Name Settings Description Reset Access

[7:0] VALUE Initiator Transmit. For test and debug purposes, when read, this register returns the byte that is currently

being transmitted by the initiator. A byte written to the transmit register can be read back later when that byte

is being transmitted on the line. This register allows access to the transmit data FIFO. The FIFO can hold

two bytes.

0x0 R/W

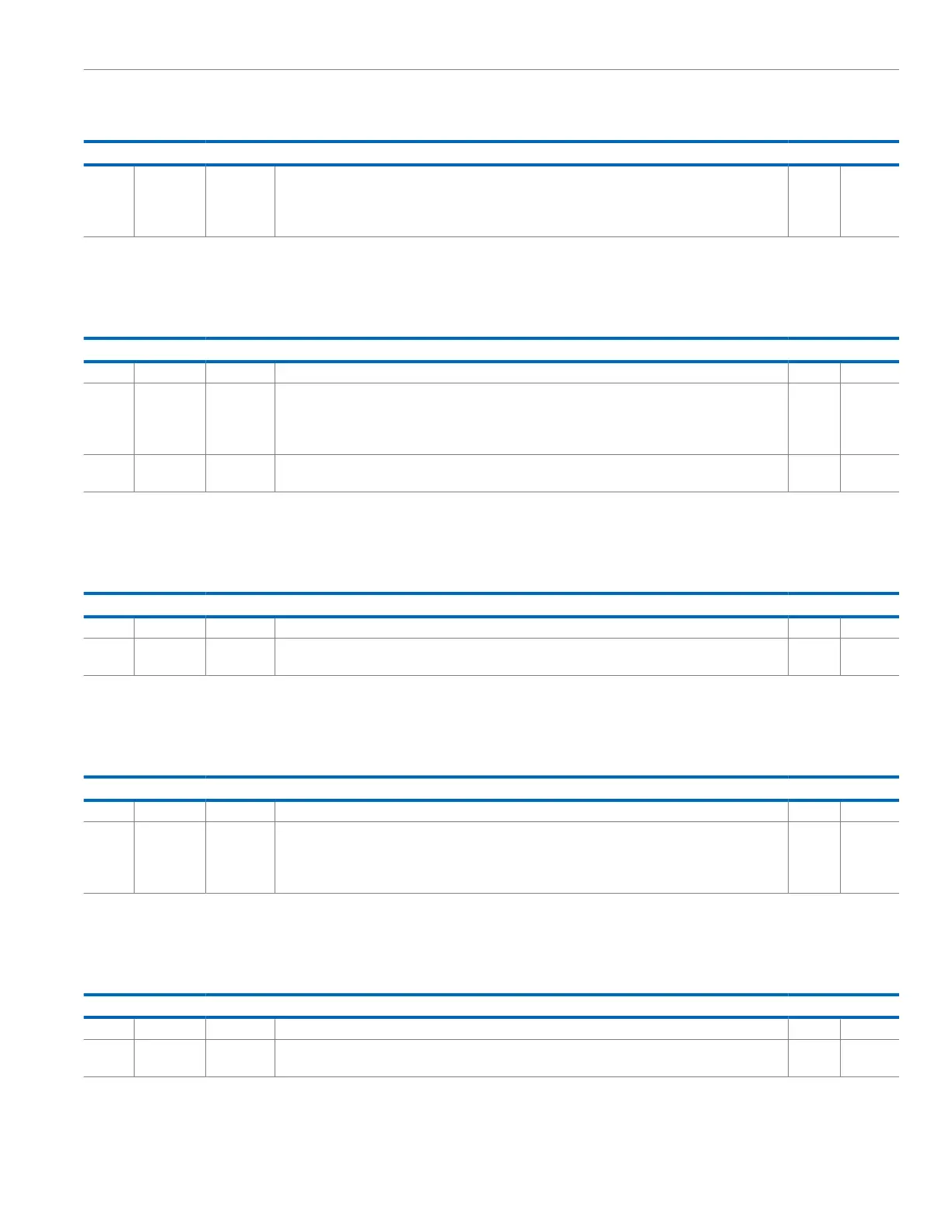

INITIATOR RECEIVE DATA COUNT REGISTER

Address: 0x40003010, Reset: 0x0000, Name: MRXCNT

Table 287. Bit Descriptions for MRXCNT

Bits Bit Name Settings Description Reset Access

[15:9] Reserved Reserved. 0x0 R

8 EXTEND Extended Read. Use this bit if more than 256 bytes are required on a read. For example, to receive 412

bytes, write 0x100 (this bit = 1). Wait for the first byte to be received, then check the register for every byte

received after. When the count bits in this register return to 0, 256 bytes have been received. Then write

0x09C to this register.

0x0 R/W

[7:0] COUNT Receive Count. Program the number of bytes required minus 1 to these bits. If 1 byte is required, write 0. If

more than 256 bytes are required, use the extend bit.

0x0 R/W

INITIATOR CURRENT RECEIVE DATA COUNT REGISTER

Address: 0x40003014, Reset: 0x0000, Name: MCRXCNT

Table 288. Bit Descriptions for MCRXCNT

Bits Bit Name Settings Description Reset Access

[15:8] Reserved Reserved. 0x0 R

[7:0] COUNT Current Receive Count. This register gives the total number of bytes received. If 256 bytes are requested,

this register reads 0 when the transaction has completed.

0x0 R

FIRST INITIATOR ADDRESS BYTE REGISTER

Address: 0x40003018, Reset: 0x0000, Name: ADR1

Table 289. Bit Descriptions for ADR1

Bits Bit Name Settings Description Reset Access

[15:8] Reserved Reserved. 0x0 R

[7:0] ADR1 Address Byte 0. If a 7-bit address is required, Bit 7 to Bit 1 of ADR1 are programmed with the address, and

Bit 0 of ADR1 is programmed with the direction (0 = write, 1 = read). If a 10-bit address is required, Bit 7 to

Bit 3 of ADR1 are programmed with 11110, Bit 2 to Bit 1 of ADR1 are programmed with the two MSBs of the

address, and Bit 0 of ADR1 is programmed to 0.

0x0 R/W

SECOND INITIATOR ADDRESS BYTE REGISTER

Address: 0x4000301C, Reset: 0x0000, Name: ADR2

Table 290. Bit Descriptions for ADR2

Bits Bit Name Settings Description Reset Access

[15:8] Reserved Reserved. 0x0 R

[7:0] ADR2 Address Byte 1. This register is only required when addressing a target with a 10-bit address. Bit 7 to Bit 0

of ADR2 are programmed with the lower eight bits of the address.

0x0 R/W

Loading...

Loading...