Reference Manual ADuCM356

REGISTER DETAILS: UART

analog.com Rev. A | 259 of 312

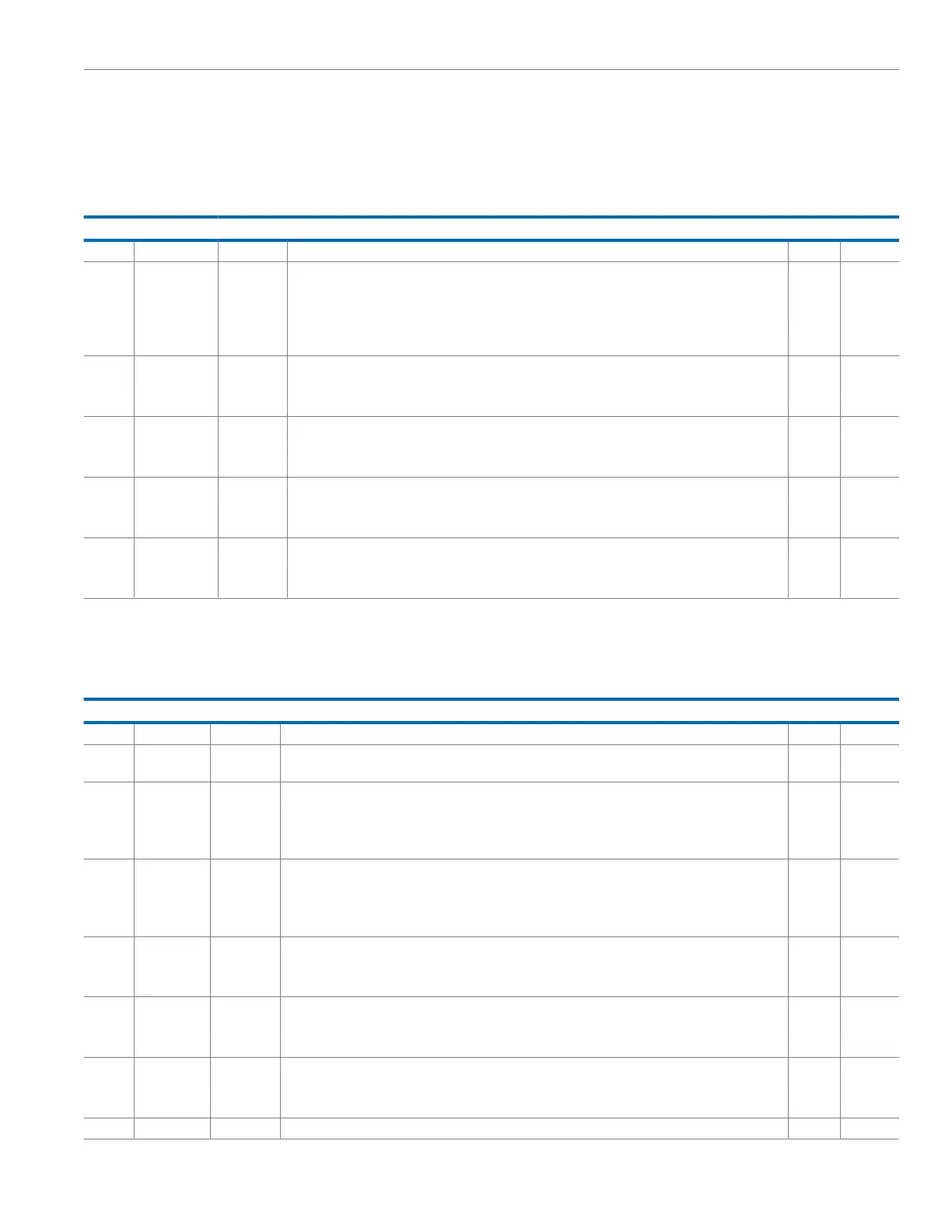

MODEM CONTROL REGISTER

Address: 0x40005010, Reset: 0x0000, Name: COMMCR

Table 326. Bit Descriptions for COMMCR

Bits Bit Name Settings Description Reset Access

[15:5] Reserved Reserved. 0x0 R

4 LOOPBACK Loopback Mode. In loopback mode, the UART_SOUT is forced high. The modem signals are also directly

connected to the status inputs (RTS in COMMCR to CTS in COMMSR, DTR in COMMCR to DSR in

COMMSR, OUT1 in COMMCR to RI in COMMSR, and OUT2 in COMMCR to DCD in COMMSR).

0x0 R/W

0 Normal operation, loopback disabled.

1 Loop back enabled.

3 OUT2 Output 2. 0x0 R/W

0 Force OUT2 to a Logic 1.

1 Force OUT2 to a Logic 0.

2 OUT1 Output 1. 0x0 R/W

0 Force OUT1 to a Logic 1.

1 Force OUT1 to a Logic 0.

1 RTS Request to Send. 0x0 R/W

0 Force RTS to a Logic 1.

1 Force RTS to a Logic 0.

0 DTR Data Terminal Ready. 0x0 R/W

0 Force DTR to a Logic 1.

1 Force DTR to a Logic 0.

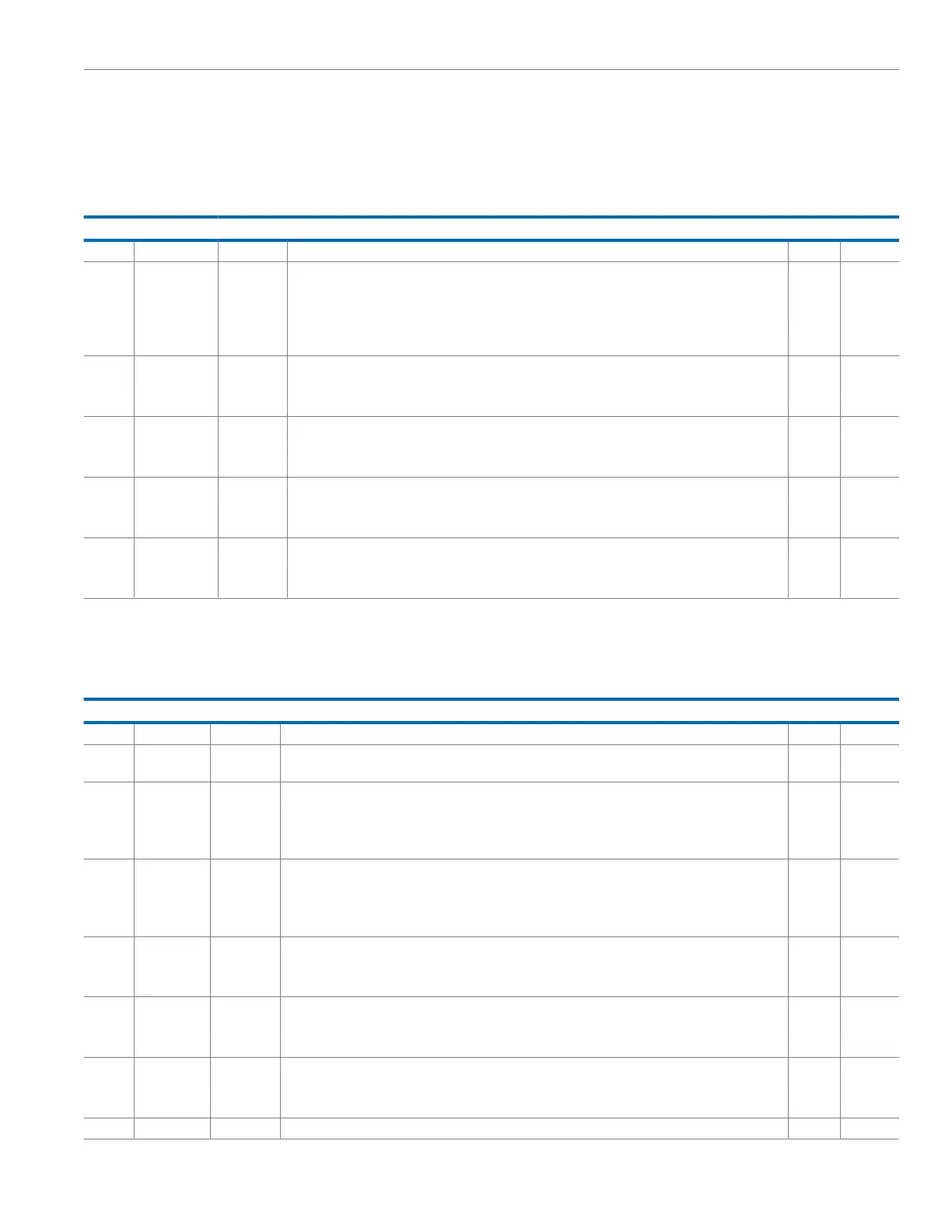

LINE STATUS REGISTER

Address: 0x40005014, Reset: 0x0060, Name: COMLSR

Table 327. Bit Descriptions for COMLSR

Bits Bit Name Settings Description Reset Access

[15:6] Reserved Reserved. 0x0 R

7 FIFOERR Data Byte(s) in Receive FIFO have Parity Error, Frame Error, or Break Indication. Only used in 16550

UART mode. This bit is cleared if there are no more errors in the receive FIFO.

0x0 RC

6 TEMT COMTX and Shift Register Empty Status. 0x1 R

0 COMTX has been written to and contains data to be transmitted. Take care not to overwrite its value.

1 COMTX and the transmit shift register are empty and it is safe to write new data to COMTX. Data has been

transmitted.

5 THRE COMTX Empty. This bit is cleared when COMRX is read. 0x1 R

0 COMTX has been written to and contains data to be transmitted. Take care not to overwrite its value.

1 COMTX is empty and it is safe to write new data to COMTX. The previous data may not have been

transmitted yet and can still be present in the shift register.

4 BI Break Indicator. If set, this bit self clears after COMLSR is read. 0x0 RC

0 UART_SIN was not detected to be longer than the maximum word length.

1 UART_SIN was held low for more than the maximum word length.

3 FE Framing Error. If set, this bit self clears after COMLSR is read. 0x0 RC

0 No invalid stop bit was detected.

1 An invalid stop bit was detected on a received word.

2 PE Parity Error. If set, this bit self clears after COMLSR is read. 0x0 RC

0 No parity error was detected.

1 A parity error occurred on a received word.

1 OE Overrun Error. If set, this bit self clears after COMLSR is read. 0x0 RC

Loading...

Loading...