Reference Manual ADuCM356

REGISTER DETAILS: UART

analog.com Rev. A | 262 of 312

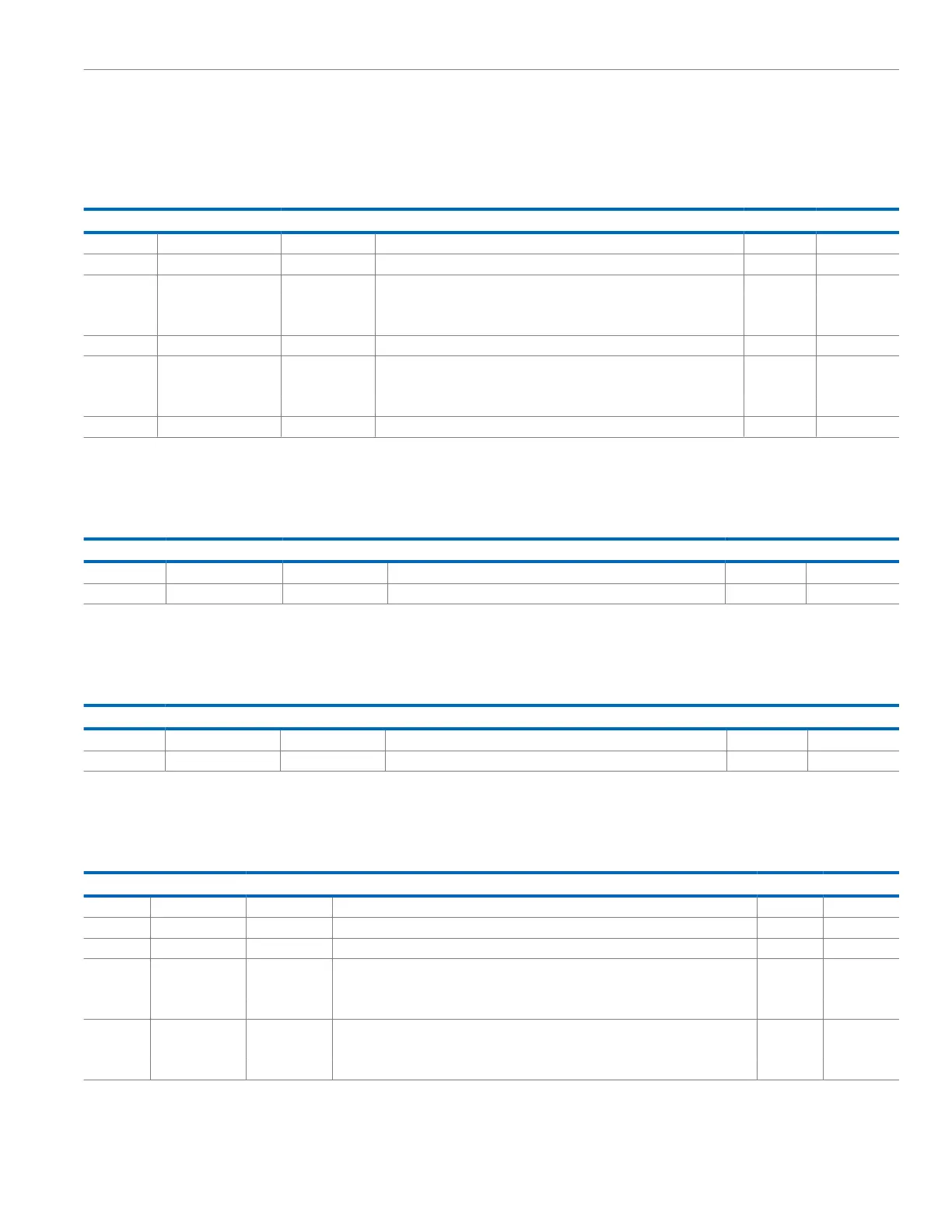

UART CONTROL REGISTER

Address: 0x40005030, Reset: 0x0100, Name: COMCTL

Table 334. Bit Descriptions for COMCTL

Bits Bit Name Settings Description Reset Access

[15:8] REV UART Revision ID. 0x1 R

[7:5] Reserved Reserved. 0x0 R

4 RXINV Invert Receiver Line. 0x0 R/W

0 Do not invert receiver line (idling high).

1 Invert receiver line (idling low).

[3:2] Reserved Reserved. 0x0 R

1 FORCECLKON Force PCLK to UART On All the Time. 0x0 R/W

0 PCLK to UART automatically clock gated.

1 PCLK to UART always on.

0 Reserved Reserved. 0x0 R

RECEIVE FIFO COUNT REGISTER

Address: 0x40005034, Reset: 0x0000, Name: COMRFC

Table 335. Bit Descriptions for COMRFC

Bits Bit Name Settings Description Reset Access

[15:5] Reserved Reserved. 0x0 R

[4:0] RFC Current Receive FIFO Data Bytes. 0x0 R

TRANSMIT FIFO COUNT REGISTER

Address: 0x40005038, Reset: 0x0000, Name: COMTFC

Table 336. Bit Descriptions for COMTFC

Bits Bit Name Settings Description Reset Access

[15:5] Reserved Reserved. 0x0 R

[4:0] TFC Current Transmit FIFO Data Bytes. 0x0 R

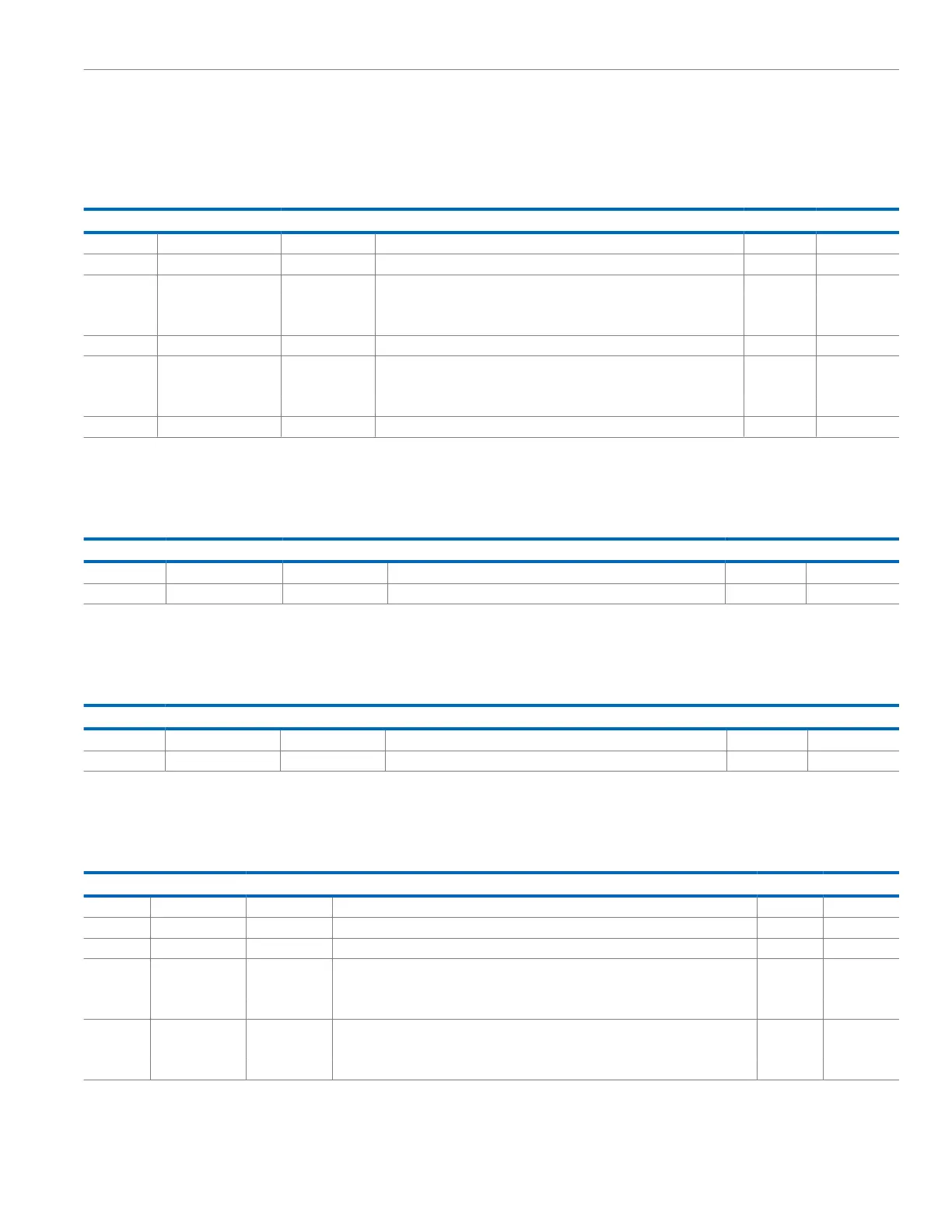

RS485 HALF-DUPLEX CONTROL REGISTER

Address: 0x4000503C, Reset: 0x0000, Name: COMRSC

Table 337. Bit Descriptions for COMRSC

Bits Bit Name Settings Description Reset Access

[15:4] Reserved Reserved. 0x0 R

3 DISTX Disable Transmit when Receiving. 0x0 R/W

2 DISRX Disable Receive when Transmitting. 0x0 R/W

1 OENSP UART_SOUT Deassert Before Full Stop Bits. 0x0 R/W

0 UART_SOUT deasserts at same time as full stop bits.

1 UART_SOUT deasserts half bit earlier than full stop bits.

0 OENP UART_SOUT Polarity. 0x0 R/W

0 High active.

1 Low active.

Loading...

Loading...