Reference Manual ADuCM356

REGISTER DETAILS: CLOCK ARCHITECTURE

analog.com Rev. A | 19 of 312

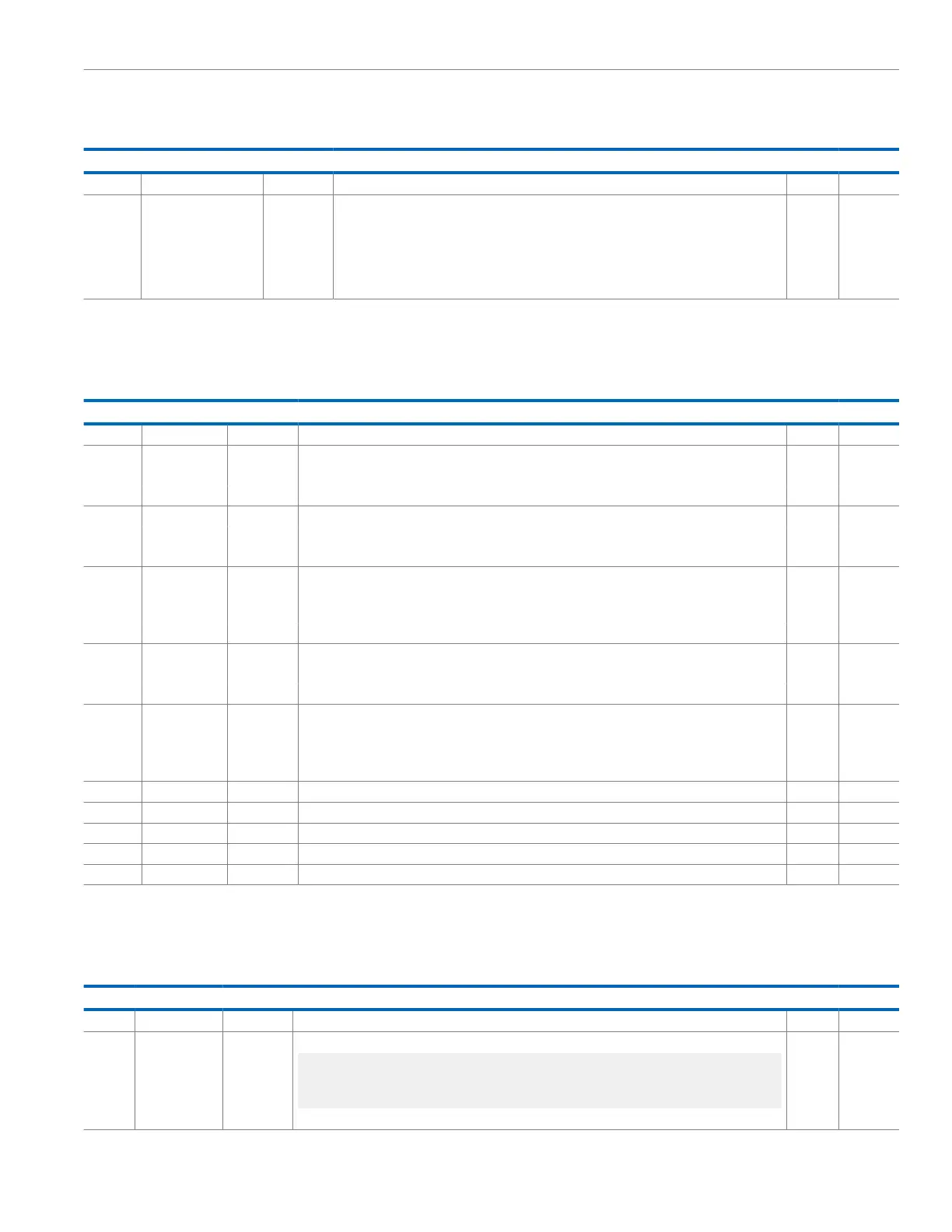

Table 11. Bit Descriptions for CLKCON0

Bits Bit Name Settings Description Reset Access

[15:6] Reserved Reserved. Do not write to this bit. 0x1 R/W

[5:0] SYSCLKDIV System Clock Divider Configuration. The system clock divider is used to provide a divided

clock from the root clock, which drives the peripheral bus, die to die interface, and most digital

peripherals. System clock frequency (f

SYS

) = root clock/SYSCLKDIV. Value range is from 1 to

32. Values larger than 32 are saturated to 32. Value 0 and Value 1 have the same results as

divide by 1. f

SYS

must be ≤16 MHz. Characterization is completed only with analog die system

clock of 4 MHz, 8 MHz, and 16 MHz.

0x1 R/W

CLOCK GATE ENABLE REGISTER

Address: 0x400C0410, Reset: 0x010A, Name: CLKEN1

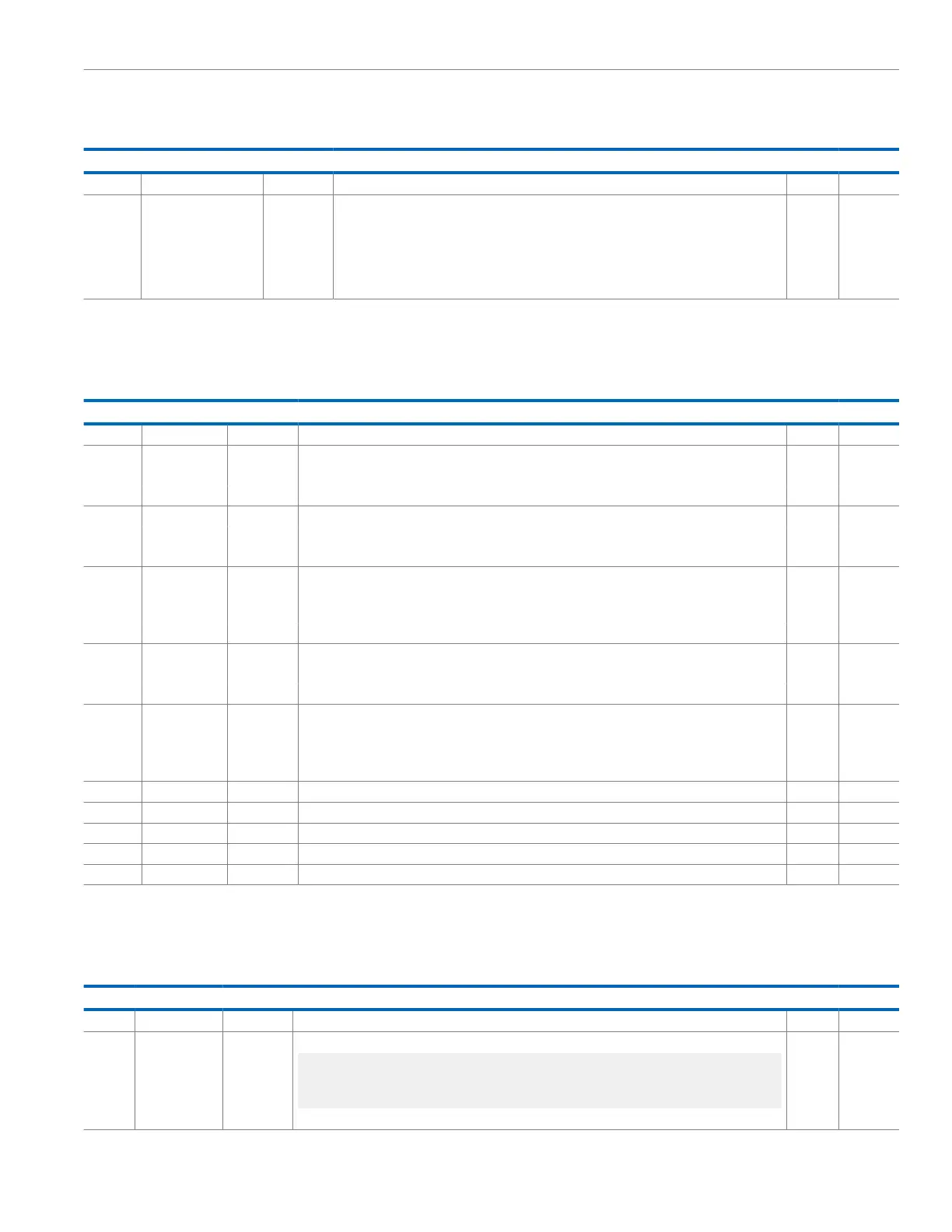

Table 12. Bit Descriptions for CLKEN1

Bits Bit Name Settings Description Reset Access

[15:10] Reserved Reserved. 0x0 R

9 AFECLKDIS AFE Die Clock Enable to AFE P2.2 Pad. 0x0 R/W

0 Connect AFE clock to AFE P2.2 pad.

1 Disconnect AFE clock from AFE P2.2 pad.

8 AFECLKSTA Reflects Status of CLKEN1 Bit, Read Only. 0x0 R

0 AFE clock connected to AFE die P2.2 pad.

1 AFE clock disconnected from AFE die P2.2 pad.

7 GPT1DIS General-Purpose Timer 1 (GPT1) Clock Enable. This bit controls pulse width modulation (PWM) Timer

1 clocks.

0x1 R/W

0 Turn on GTP1 clock.

1 Turn off GPT1 clock.

6 GPT0DIS General-Purpose Timer 0 (GPT0) Clock Enable. This bit controls PWM Timer 0 clocks. 0x1 R/W

0 Turn on GPT0 clock.

1 Turn off GPT0 clock.

5 ACLKDIS ACLK Clock Enable. This bit controls the clock to the DFT and the waveform generator blocks control

clock, including analog interface and digital signal processing.

0x0 R/W

0 Turn on ACLK clock.

1 Turn off ACLK clock.

4 Reserved Reserved. Never write to this bit. Leave this bit cleared to 0. 0x0 R/W

3 Reserved Reserved. Never write to this bit. 0x0 R/W

2 Reserved Reserved. Never write to this bit. Leave this bit cleared to 0. 0x0 R/W

1 Reserved Reserved. Never write to this bit. 0x0 R/W

0 Reserved Reserved. Never write to this bit. Leave this bit cleared to 0. 0x0 R/W

CLOCK SELECT REGISTER

Address: 0x400C0414, Reset: 0x0000, Name: CLKSEL

Table 13. Bit Descriptions for CLKSEL

Bits Bit Name Settings Description Reset Access

[15:4] Reserved Reserved. 0x0 R

[3:2] ADCCLKSEL Select ADC Clock Source. To configure the GPIO1 pin for an external clock, 0x0 R/W

pADI_AGPIO2->CON |= 3<<2; // EXT_CLK pADI_AGPIO2->IEN |=

1<<1; //AGPIO2.1(PWM1) input

0 Internal high frequency oscillator clock.

Loading...

Loading...