Reference Manual ADuCM356

REGISTER DETAILS: ANALOG DIE GENERAL-PURPOSE TIMERS

analog.com Rev. A | 274 of 312

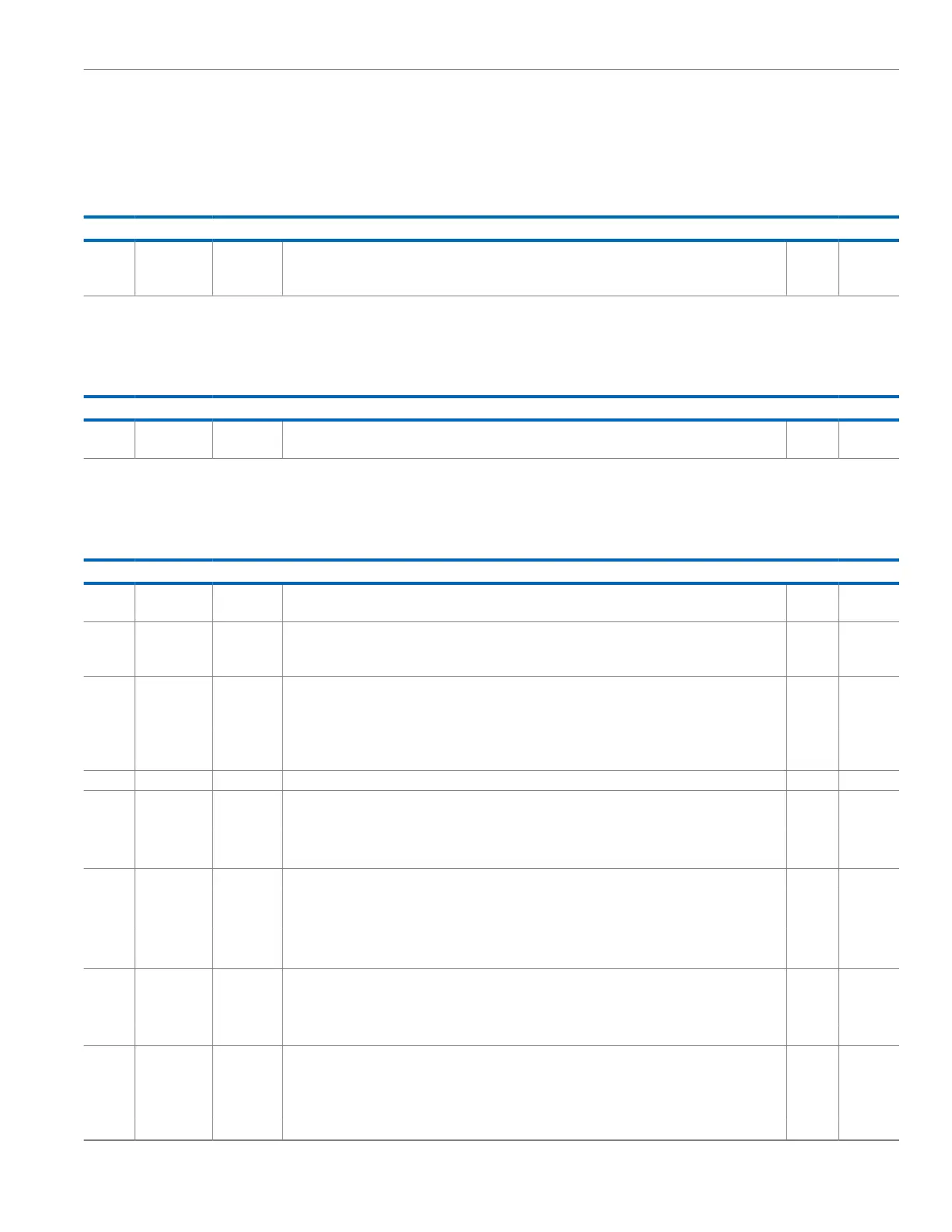

16-BIT LOAD VALUE REGISTER

Address: 0x400C0D00, Reset: 0x0000, Name: LD0

Table 353. Bit Descriptions for LD0

Bits Bit Name Settings Description Reset Access

[15:0] LOAD Load Value. The up or down counter is periodically loaded with this value if periodic mode is selected

(CON0, Bit 3 = 1). LD0 writes during up or down counter timeout events are delayed until the event has

passed.

0x0 R/W

16-BIT TIMER VALUE REGISTER

Address: 0x400C0D04, Reset: 0x0000, Name: VAL0

Table 354. Bit Descriptions for VAL0

Bits Bit Name Settings Description Reset Access

[15:0] VAL Current Count. Reflects the current up or down counter value. Value delayed two PCLK cycles due to

clock synchronizers.

0x0 R

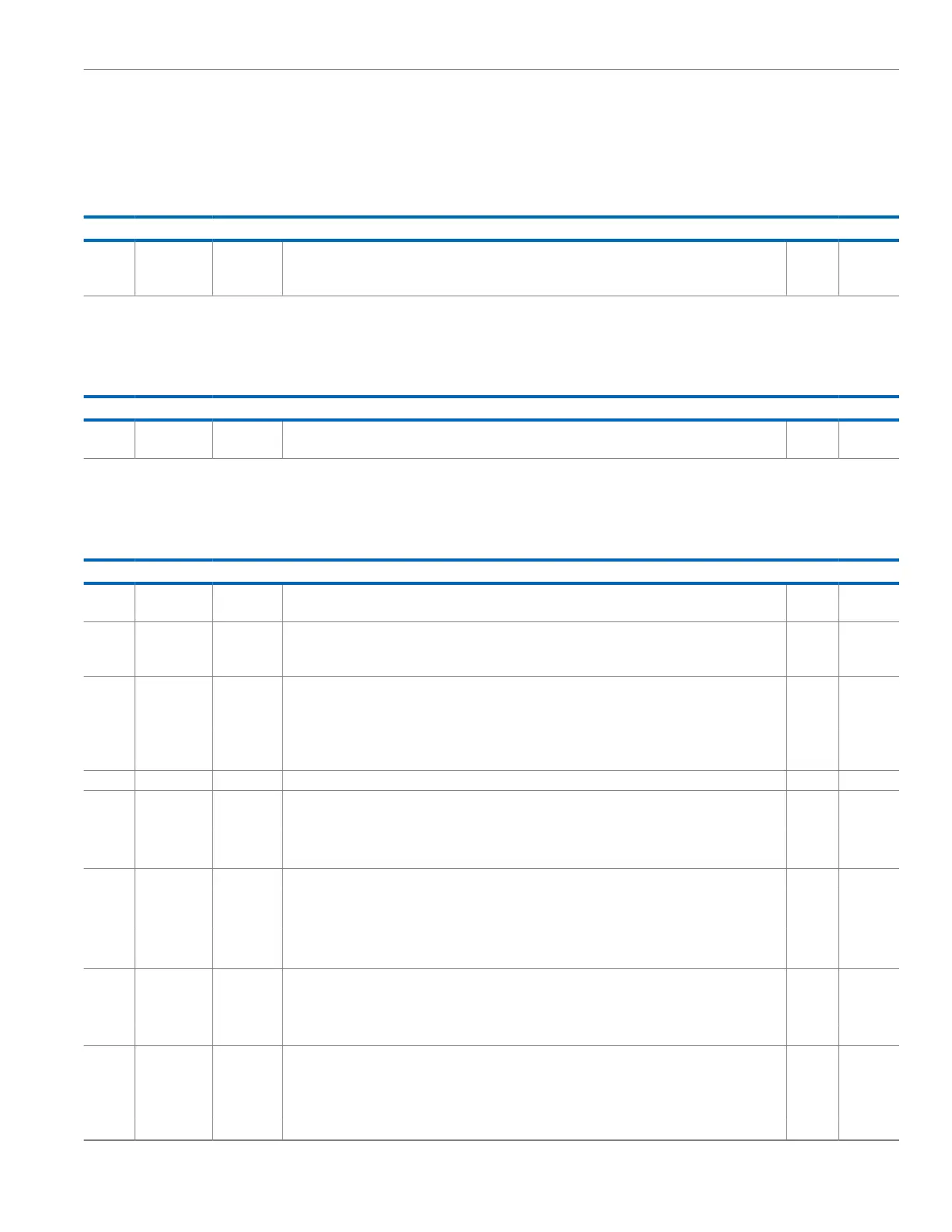

CONTROL REGISTER

Address: 0x400C0D08, Reset: 0x000A, Name: CON0

Table 355. Bit Descriptions for CON0

Bits Bit Name Settings Description Reset Access

15 SYNCBYP Synchronization Bypass. Used to bypass the synchronization logic within the block. Use only with

synchronous clocks. This bit field also changes the CON0, Bits[1:0] maximum prescaler count from 3 to 0.

0x0 R/W

14 RSTEN Counter and Prescale Reset Enable. Used to enable and disable the reset feature. Used in conjunction

with the EVTEN and EVENT select range. When a selected event occurs, the 16-bit counter and 8-bit

prescale are reset. This reset is required in PWM demodulation mode.

0x0 R/W

13 EVTEN Event Select. Used to enable and disable the capture of events. Used in conjunction with the event

select range. When a selected event occurs, the current value of the up or down counter is captured in

GPTx_CAPTURE.

0x0 R/W

0 Events are not captured.

1 Events are captured.

[12:8] EVENT Event Select Range. Timer event select range (0 to 31). 0x0 R/W

7 RLD Reload Control. This bit is only used for periodic mode. This bit allows the user to select whether the up or

down counter is reset only on a timeout event or when CLRI0, Bit 0 is set.

0x0 R/W

1 Resets the up or down counter when the clear timeout interrupt bit is set.

0 Up or down counter is only reset on a timeout event.

[6:5] CLK Clock Select. Used to select a timer clock from the four available clock sources. 0x0 R/W

00 AFE PCLK.

01 AFE high-power oscillator.

10 AFE low frequency oscillator.

11 External clock.

4 ENABLE Timer Enable. Used to enable and disable the timer. Clearing this bit resets the timer, including the VAL0

register.

0x0 R/W

0 Timer is disabled. Default.

1 Timer is enabled.

3 MOD Timer Mode. This bit is used to control whether the timer runs in periodic or free running mode. In periodic

mode, the up or down counter starts at the defined load value. In free running mode, the up or down

counter starts at 0x0000 or 0xFFFF, depending on whether the timer is counting up or down.

0x1 R/W

1 Timer runs in periodic mode. Default.

0 Timer runs in free running mode.

Loading...

Loading...