Reference Manual ADuCM356

I

2

C SERIAL INTERFACE

analog.com Rev. A | 221 of 312

I

2

C FEATURES

The I

2

C interface features an initiator or target mode with 2-byte

transmit and receive FIFOs. The I

2

C interface supports 7-bit and

10-bit addressing modes, either as four 7-bit device addresses or

a combination of one 10-bit address and two 7-bit addresses in

the target with repeated starts in initiator and target modes. Other

devices on the bus can enable clock stretching without causing any

issues with the ADuCM356. Initiator arbitration, continuous read

mode for the initiator or up to 512 bytes, fixed read, and internal

and external loopback are also available.

Support for DMA in initiator and target modes is provided by the

DMA controller, as well as software control on the target of the no

acknowledge signal.

I

2

C OVERVIEW

The I

2

C data transfer uses a serial clock pin (I2C_SCL) and a serial

data pin (I2C_SDA). These pins are configured in a wire-AND’ed

gated format that allows arbitration in a multiinitiator system.

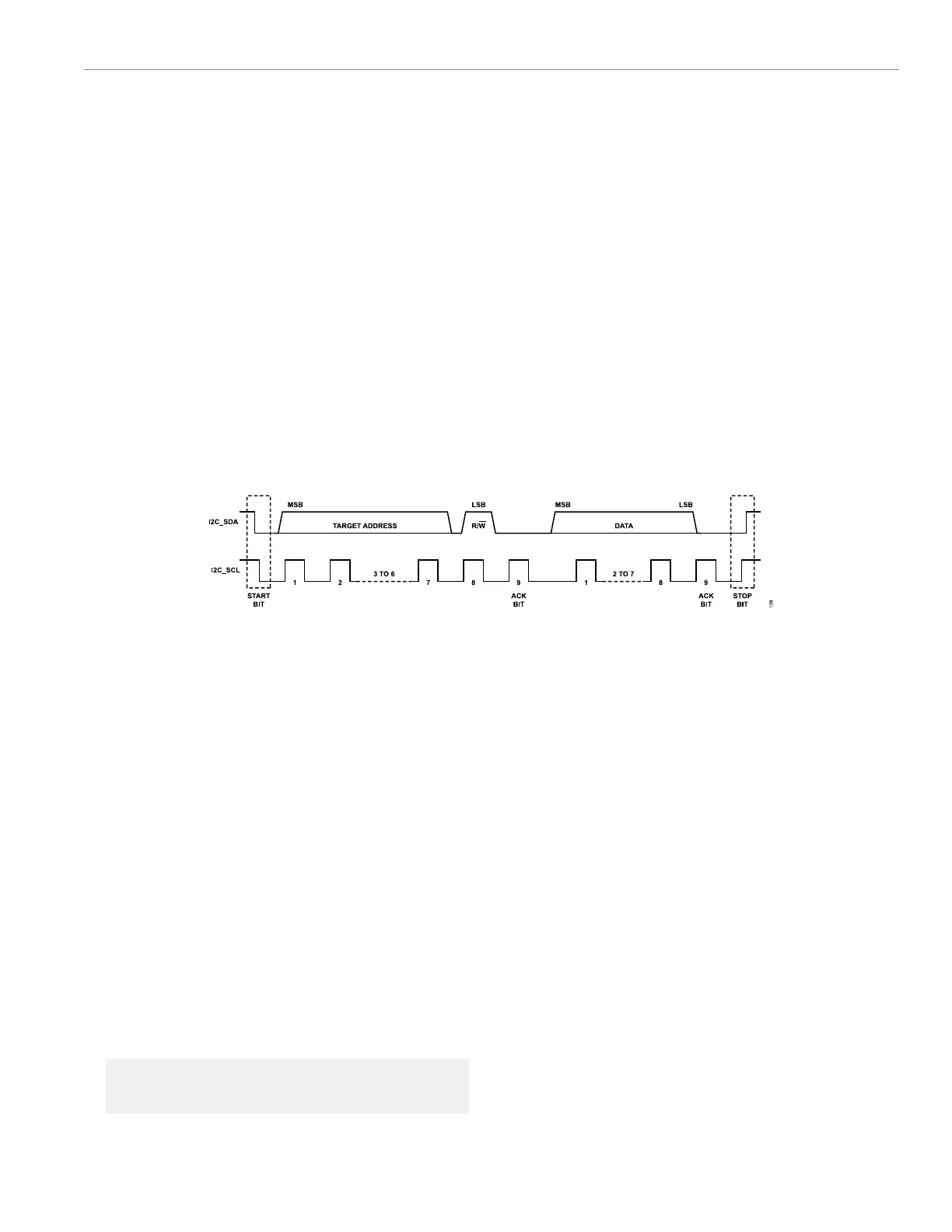

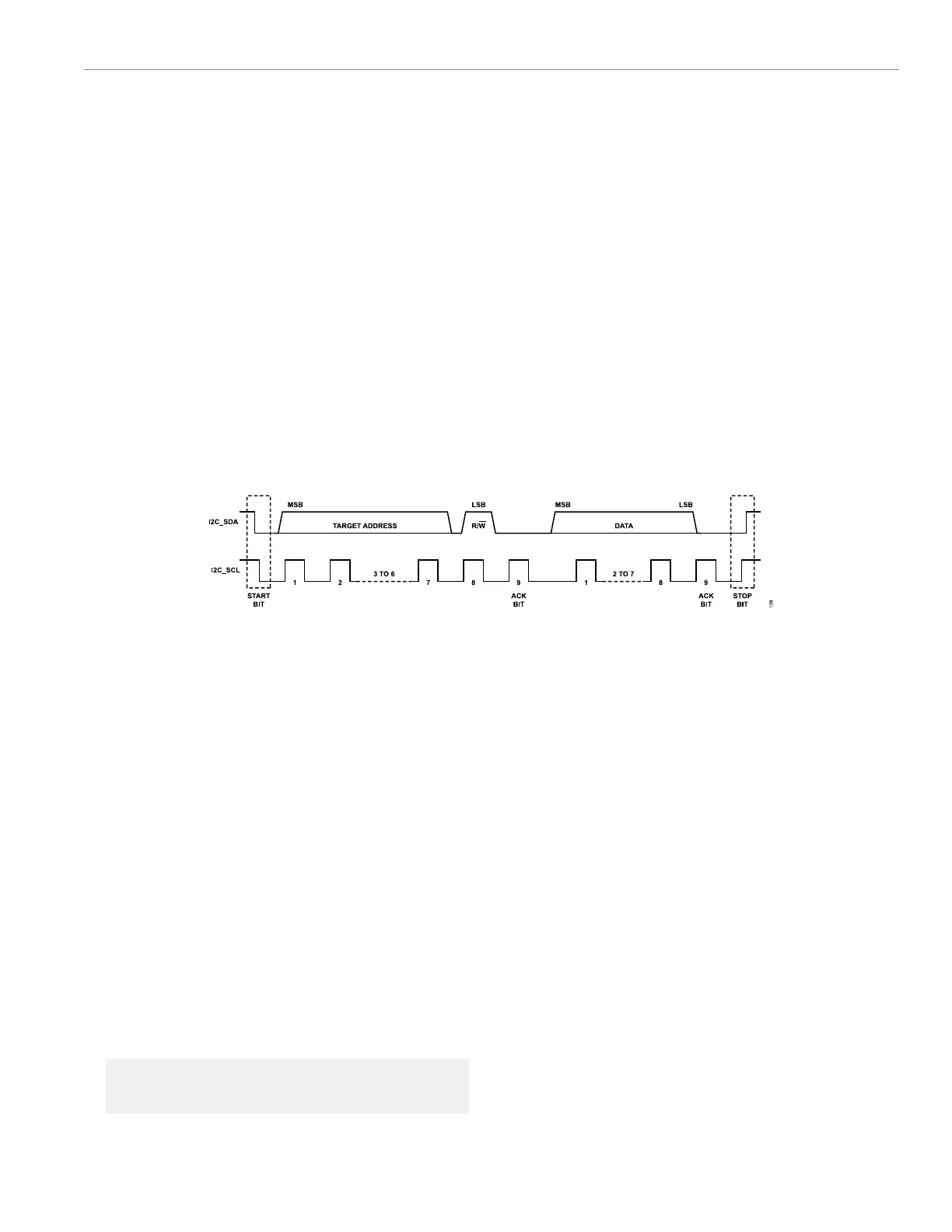

The transfer sequence of the I

2

C system is initiated by an initiator

device, which generates a start condition while the bus is idle. The

initiator transmits the target device address and the direction of the

data transfer during the initial address transfer. If the initiator does

not lose arbitration and the target acknowledges the initial address

transfer, the data transfer is initiated. This transfer continues until

the initiator issues a stop condition and the bus becomes idle.

Figure 57 shows a typical I

2

C transfer.

An initiator device can be configured to generate the serial clock.

The frequency is programmed by the user in the serial clock divisor

register, DIV. The initiator channel can be set to operate in fast

mode (400 kHz) or standard mode (100 kHz).

Figure 57. Typical I

2

C Transfer Sequence

The user programs the I

2

C bus peripheral address in the I

2

C bus

system. This ID can be modified any time a transfer is not in

progress. The user can set up to four target addresses that are

recognized by the peripheral. The peripheral is implemented with a

2‑byte FIFO for each transmit and receive shift register. The IRQ

and status bits in the control registers are available to signal to the

processor core when the FIFOs need to be serviced.

I

2

C OPERATION

I

2

C Startup

The following steps are required to run the I

2

C peripheral:

1. Enable PCLK to the I

2

C peripheral by setting CTL5, Bit 5

and CTL5, Bit 3 = 0. PCLK frequency is controlled via CTL1,

Bits[13:8].

2. Configure the digital pins (P0.4/I2C_SCL and P0.5/I2C_SDA)

for I

2

C operation via the GP0CON register.

3. Ensure the drive strength for the P0.4/I2C_SCL pin and P0.5/

I2C_SDA pin is increased to ensure reliable I

2

C communica-

tions, as detailed in the following example code:

GP0DS = 0x30; // Increase drive strength

of I2C pins.

4. Configure the I

2

C registers as required for target or initiator

operation.

5. Enable the I

2

C target or initiator interrupt source as required.

When using I

2

C, the user must disable the internal pull-up resistors

on the I

2

C pins via the GP0POL register. The GPIO multiplexed

configuration mode is I2C_SCL for P0.4/I2C_SCL and is I2C_SDA

for P0.5/I2C_SDA.

7-Bit Addressing

The ID0 register, ID1 register, ID2 register, and ID3 register contain

the target device IDs. The ADuCM356 compares the four IDx

registers to the address byte. To be correctly addressed, the seven

MSBs of IDx registers must be identical to that of the seven MSBs

of the first received address byte. The LSB of the IDx registers

(R/W or the transfer directional bit) is ignored in the process of

address recognition. The initiator addresses a device using the

ADR1 register.

10-Bit Addressing

This feature is enabled by setting SCTL, Bit 1 for initiator and

target mode. The 10-bit address of the target is stored in the

ID0 register and ID1 register, where the ID0 register contains the

first byte of the address, and the R/W bit and the upper five bits

must be programmed to 11110, as shown in Figure 58. The ID1

Loading...

Loading...