Reference Manual ADuCM356

REGISTER DETAILS: ADC CIRCUIT

analog.com Rev. A | 63 of 312

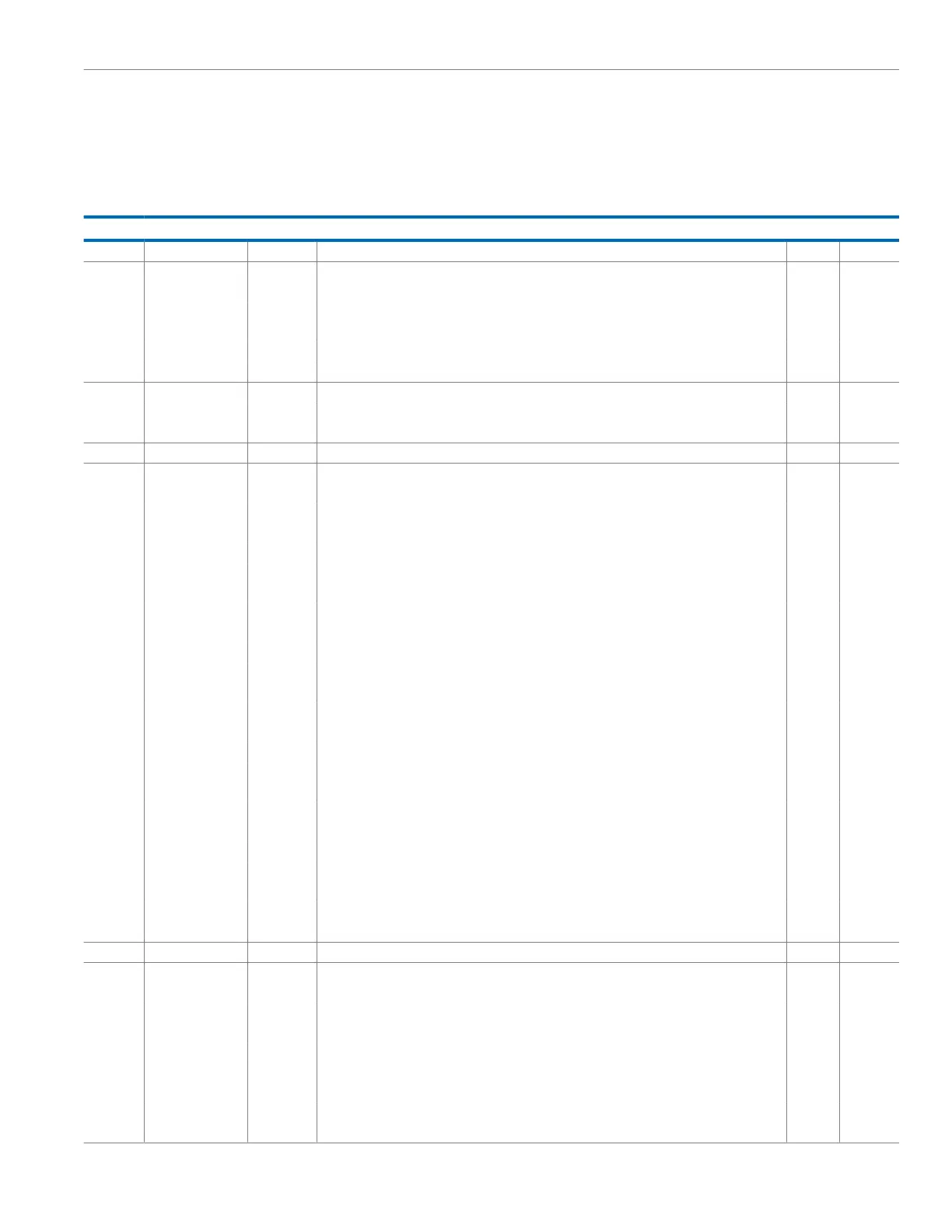

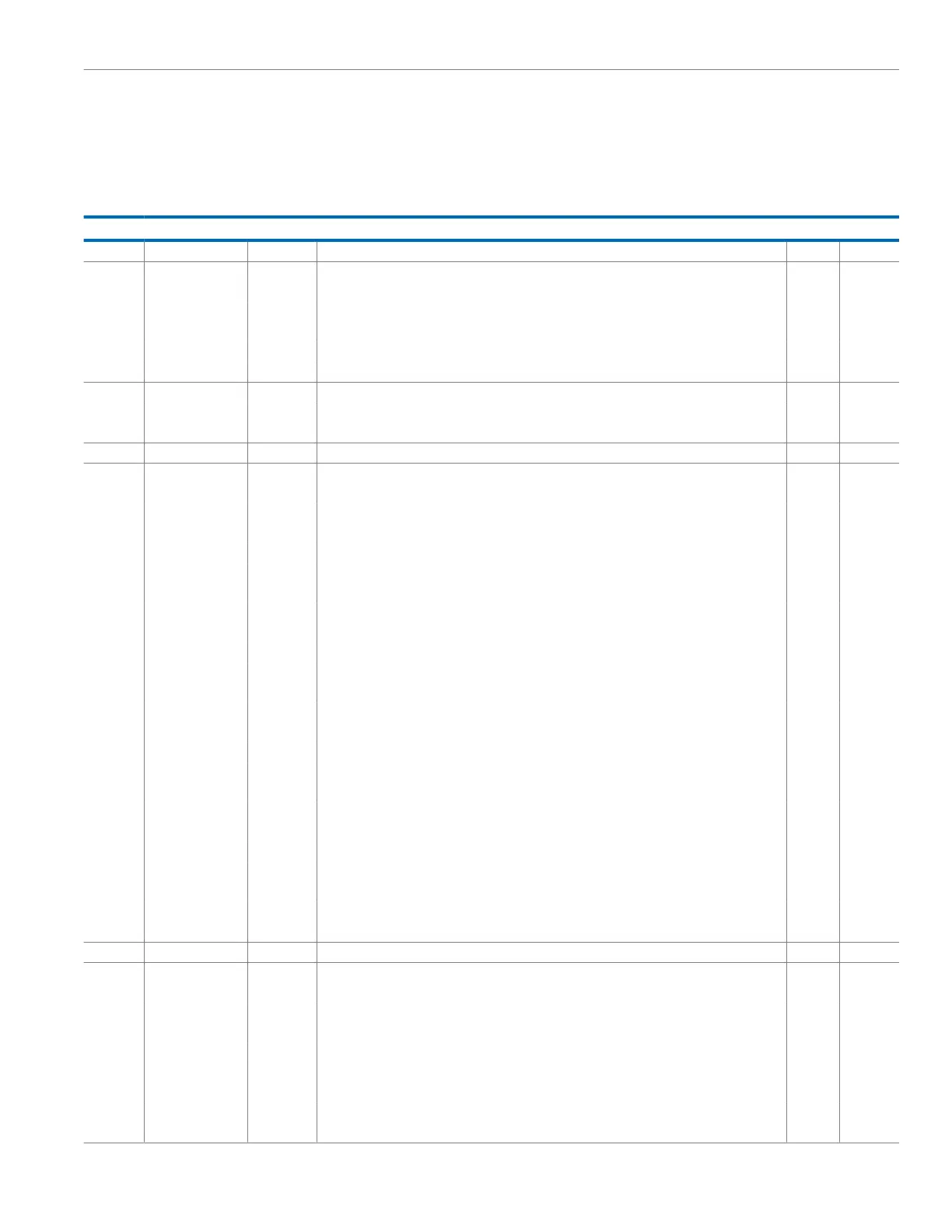

ADC CONFIGURATION REGISTER

Address: 0x400C21A8, Reset: 0x00000000, Name: ADCCON

Table 63. Bit Descriptions for ADCCON

Bits Bit Name Settings Description Reset Access

[31:19] Reserved Reserved. 0x0 R

[18:16] GNPGA PGA Gain Setup. 0x0 R/W

000 Gain = 1.

001 Gain = 1.5.

010 Gain = 2.

011 Gain = 4.

1XX Gain = 9.

15 GNOFSELPGA Internal Offset/Gain Cancellation. 0x0 R/W

0 DC offset cancellation disabled.

1 Enable DC offset cancellation. When PGA is enabled, only gain = 4 supported.

[14:13] Reserved Reserved. 0x0 R/W

[12:8] MUXSELN Select Signals for the ADC Input Multiplexer N Input (Negative Input Signal). 0x0 R/W

00000 Floating input.

00001 High-speed TIA inverting input.

00010 Low-power TIA0 inverting input.

00011 Low-power TIA1 inverting input.

00100 AIN0.

00101 AIN1.

00110 AIN2.

00111 AIN3/BUF_VREF1V8.

01000 ADCVBIAS_CAP.

01001 Reserved.

01010 Reserved.

01011 Temperature Sensor 0 negative input.

01100 AIN4_LPF0.

01101 AIN5.

01110 AIN6.

01111 Reserved.

10000 VZERO0.

10001 VBIAS0.

10010 VZERO1.

10011 VBIAS1.

10100 N node of excitation amplifier.

10101 Temperature Sensor 1 negative input.

10110 Test signal.

[7:6] Reserved Reserved. 0x0 R

[5:0] MUXSELP Select Positive Mux (Positive ADC Input). 0x0 R/W

00000 Floating input.

00001 High-speed TIA output.

00010 Low-power TIA0 output after the low-pass filter.

00011 Low-power TIA1 output after the low-pass filter.

00100 AIN0.

00101 AIN1.

00110 AIN2.

00111 AIN3/BUF_VREF1V8.

Loading...

Loading...