Reference Manual ADuCM356

REGISTER DETAILS: DMA

analog.com Rev. A | 172 of 312

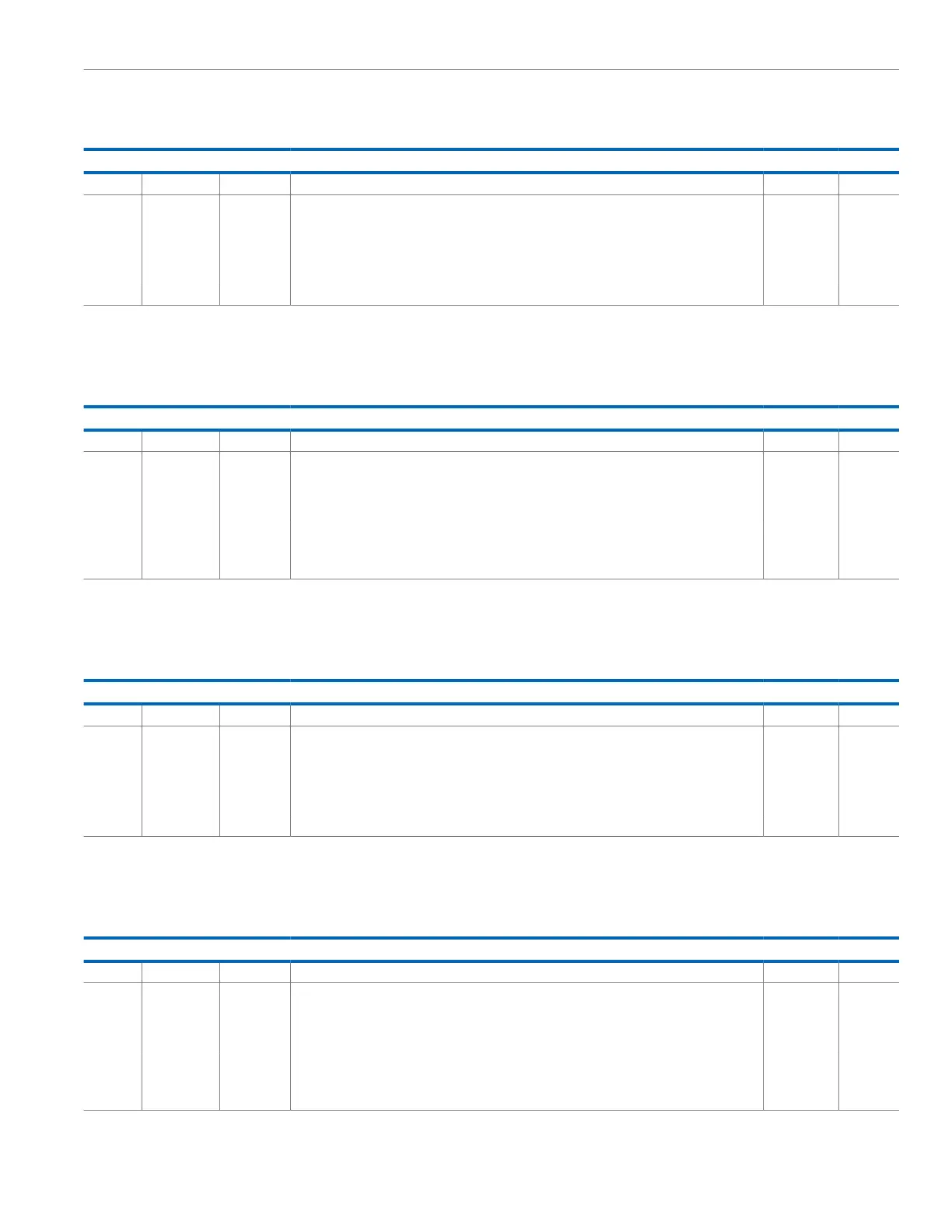

Table 201. Bit Descriptions for SWREQ

Bits Bit Name Settings Description Reset Access

[31:24] Reserved Reserved. 0x00 R

[23:0] CHAN Generate Software Request. Set the appropriate bit to generate a software DMA request on the

corresponding DMA channel. Bit 0 corresponds to DMA Channel 0. Bit M − 1 corresponds to the

DMA Channel M – 1. These bits are automatically cleared by the hardware after the corresponding

software request completes.

0x000000 W

0 DMA request is not created for Channel C.

1 DMA request is created for Channel C.

CHANNEL REQUEST MASK SET REGISTER

Address: 0x40010020, Reset: 0x00000000, Name: RMSK_SET

Table 202. Bit Descriptions for RMSK_SET

Bits Bit Name Settings Description Reset Access

[31:24] Reserved Reserved. 0x00 R

[23:0] CHAN Mask Requests from DMA Channels. This register disables DMA requests from peripherals. Each

bit of the register represents the corresponding channel number in the DMA controller. Set the

appropriate bit to mask the request from the corresponding DMA channel. Bit 0 corresponds to

DMA Channel 0. Bit M – 1 corresponds to DMA Channel M – 1.

0x000000 R/W

0 When read as 0, requests are enabled for Channel C. When written as 0, no effect.

1 When read as 1, requests are disabled for Channel C. When written as 1, peripherals associated

with Channel C are disabled from generating DMA requests.

CHANNEL REQUEST MASK CLEAR REGISTER

Address: 0x40010024, Reset: 0x00000000, Name: RMSK_CLR

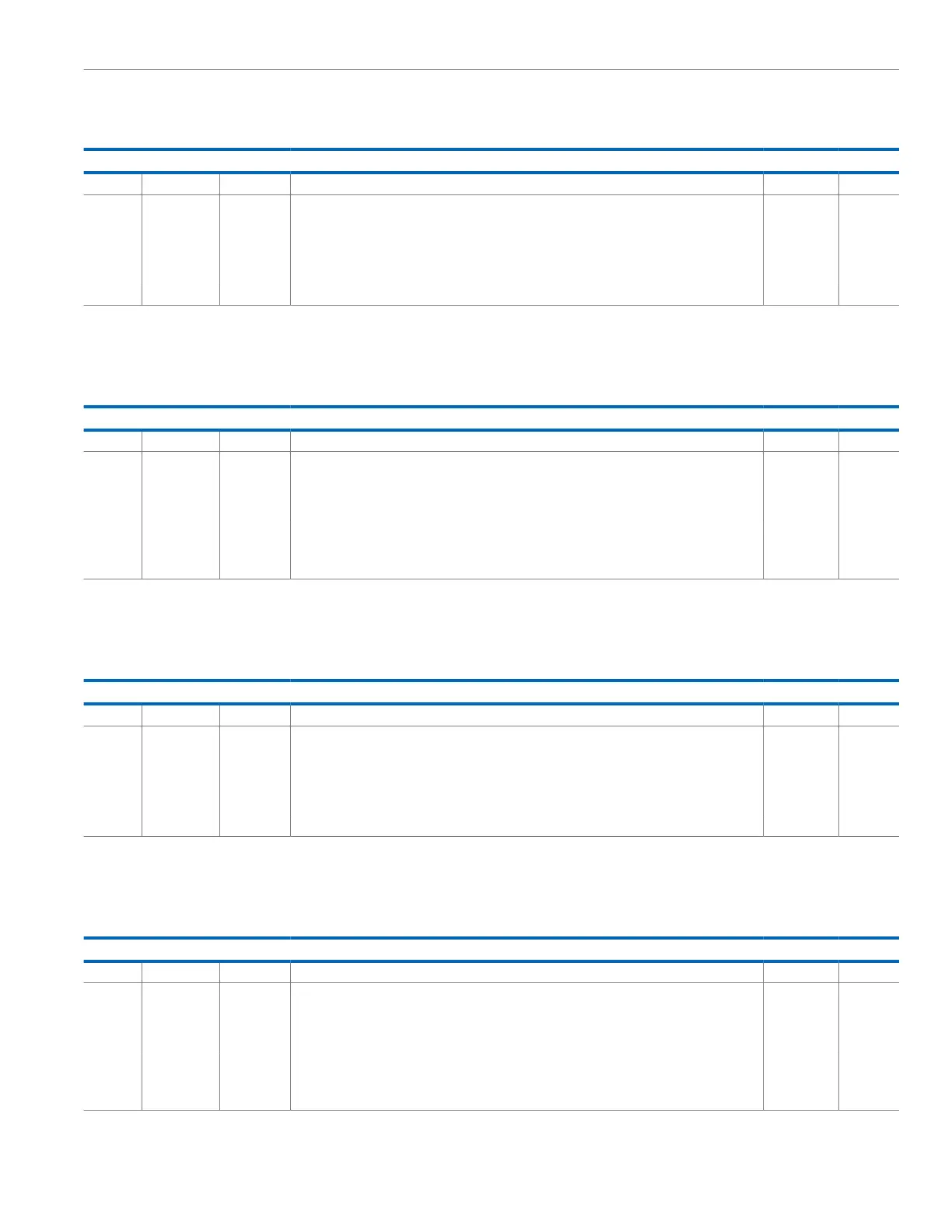

Table 203. Bit Descriptions for RMSK_CLR

Bits Bit Name Settings Description Reset Access

[31:24] Reserved Reserved. 0x00 R

[23:0] CHAN Clear Request Mask Set Bits. This register enables DMA requests from peripherals by clearing the

mask set in the RMSK_SET register. Each bit of the register represents the corresponding channel

number in the DMA controller. Set the appropriate bit to clear the corresponding bit in RMSK_SET,

Bits[23:0]. Bit 0 corresponds to DMA Channel 0. Bit M – 1 corresponds to DMA Channel M – 1.

0x000000 W

0 No effect. Use the RMSK_SET register to disable DMA requests.

1 Peripherals associated with Channel C are enabled to generate DMA requests.

CHANNEL ENABLE SET REGISTER

Address: 0x40010028, Reset: 0x00000000, Name: EN_SET

Table 204. Bit Descriptions for EN_SET

Bits Bit Name Settings Description Reset Access

[31:24] Reserved Reserved. 0x00 R

[23:0] CHAN Enable DMA Channels. This register allows the enabling of DMA channels. Reading the register

returns the enable status of the channels. Each bit of the register represents the corresponding

channel number in the DMA controller. Set the appropriate bit to enable the corresponding channel.

Bit 0 corresponds to DMA Channel 0. Bit M – 1 corresponds to DMA Channel M – 1.

0x000000 R/W

0 When read as 0, Channel C is disabled. When written as 0, no effect. Use the EN_CLR register to

disable this channel.

1 When read as 1, Channel C is enabled. When written as 1, Channel C is enabled.

Loading...

Loading...