Reference Manual ADuCM356

REGISTER DETAILS: SPI0/SPI1

analog.com Rev. A | 250 of 312

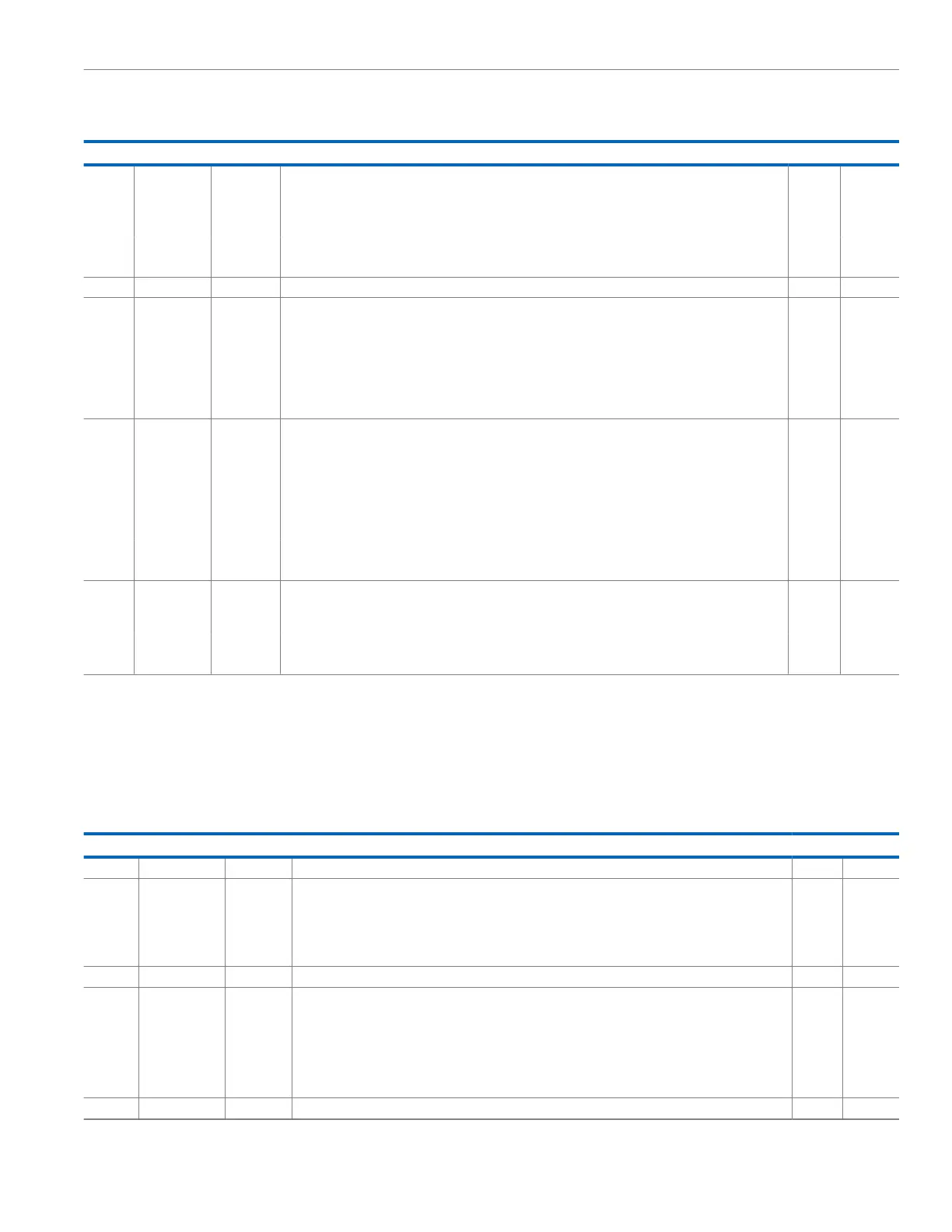

Table 315. Bit Descriptions for SPI0_RD_CTL, SPI1_RD_CTL (Continued)

Bits Bit Name Settings Description Reset Access

is driven by the initiator during the transmit phase. After a wait time of SPI_WAIT_TMR SCLK cycles, the

target is expected to drive the same MOSI pin. Program SPI_FLOW_CTL, Bits[1:0] to 01 to introduce wait

states for allowing turnaround time. Otherwise, the target only has a turnaround time of a half SCLK period

(between sampling and driving edges of SCLK). If this mode is used, set the OVERLAP bit = 0.

0 SPI is a 4-pin interface.

1 SPI is a 3-pin interface.

[7:6] Reserved Reserved. 0x0 R

[5:2] TXBYTES Transmit Byte Count Minus 1 for Read Command. This field specifies the number of bytes to be

transmitted minus 1 before reading data from a target. This field can accept values from 0 to 15,

corresponding to 1 to 16 transmit bytes. Accepted bytes include all the bytes that must be sent out to

the target, such as command and address (if required). The design does not differentiate between the

command and address, but transmits the specified number of bytes from the transmit FIFO. If there is a

latency between the command transmission and data reception, account for the number of transmit bytes

(mostly 0s) to be padded for that delay.

0x0 R/W

1 OVERLAP Transmit and Receive Overlap Mode. This bit specifies if the start of transmit and receive overlap. In

most of the targets, the read data starts only after the initiator completes the transmission of command

and address. This transfer is nonoverlapping. In some targets, there may be status bytes sent out while

the command is being received, called overlapping mode. Therefore, start receiving the bytes from the

beginning of the chip select frame. In case of overlapping mode, SPIx_CNT, Bits[13:0] refer to the total

number of bytes to be received. Account for the extra status bytes (in addition to the actual read bytes)

while programming SPIx_CNT, Bits[13:0].

0x0 R/W

0 Transmit receive overlap is disabled.

1 Transmit receive overlap is enabled.

0 CMDEN Read Command Enable. SPI read command mode where a command and address are transmitted

and read data is expected in the same chip select frame. If this bit is cleared, all other fields of the

SPIx_RD_CTL register, SPIx_FLOW_CTL register, and SPIx_WAIT_TMR register have no effect.

0x0 R/W

0 Read command mode is disabled.

1 Read command mode is enabled.

FLOW CONTROL REGISTERS

Address: 0x40004028, Reset: 0x0000, Name: SPI0_FLOW_CTL

Address: 0x40024028, Reset: 0x0000, Name: SPI1_FLOW_CTL

This register is only used in initiator mode.

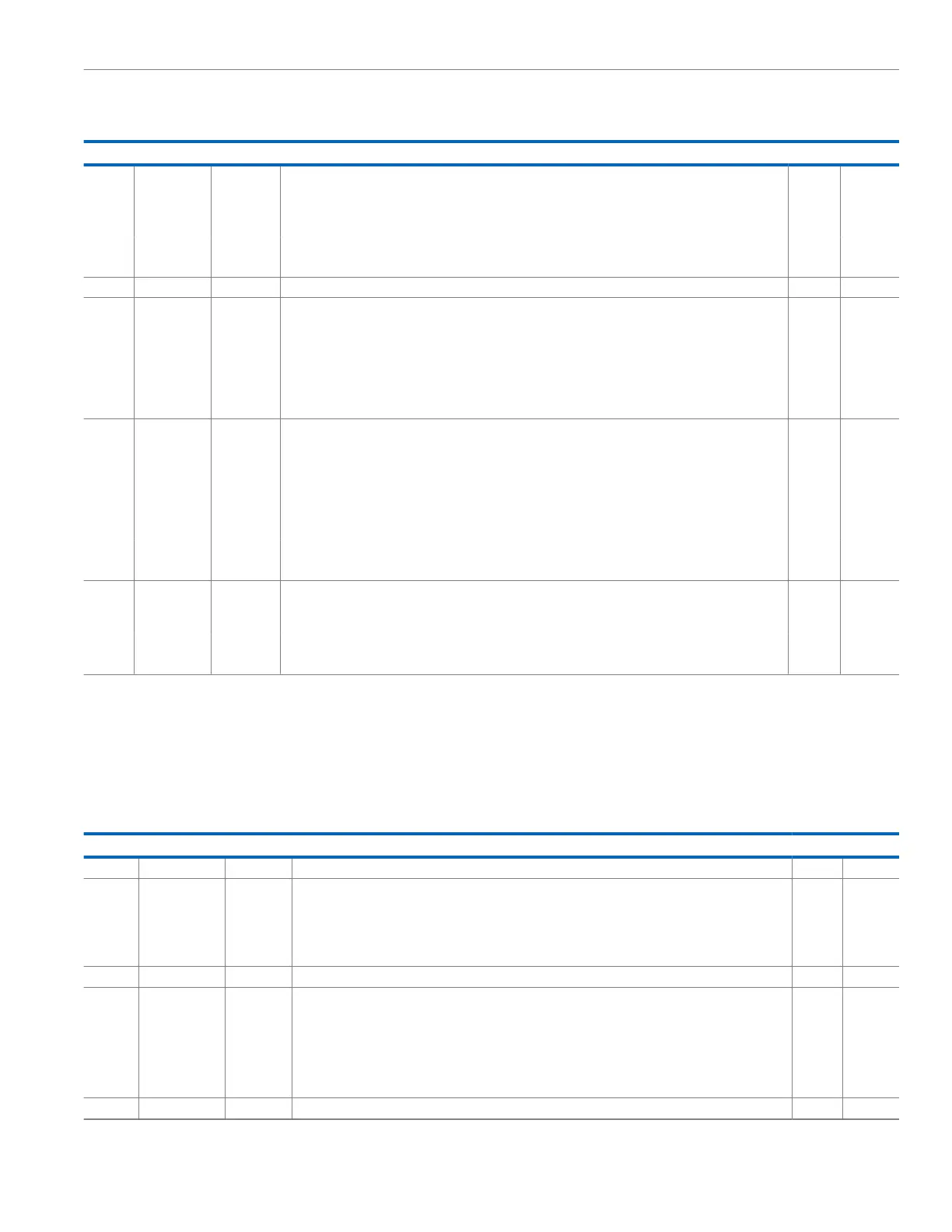

Table 316. Bit Descriptions for SPI0_FLOW_CTL, SPI1_FLOW_CTL

Bits Bit Name Settings Description Reset Access

[15:12] Reserved Reserved. 0x0 R

[11:8] RDBURSTSZ Read Data Burst Size Minus 1. This field specifies the number of bytes to be received minus 1 in a single

burst from a target before waiting for flow control. This bit is not valid if SPIx_FLOW_CTL, Bits[1:0] =

0b00. For all other values of SPIx_FLOW_CTL, Bits[1:0], this field is valid. This field can take values from

0 to 15, implying a read burst of 1 byte to 16 bytes. This mode is useful for reading fixed width conversion

results periodically.

0x0 R/W

[7:5] Reserved Reserved. 0x0 R

4 RDYPOL Polarity of P0.3 Line. This field specifies the polarity of the P0.3 pin, which indicates that the read data of

the target is ready. If SPIx_FLOW_CTL, Bits[1:0] = 0b10, this field refers to the polarity of the P0.3 pin.

Otherwise, if SPIx_FLOW_CTL, Bits[1:0] = 0b11, this field refers to the polarity of the MISO line. For all

other values of SPIx_FLOW_CTL, Bits[1:0], this bit is ignored.

0x0 R/W

0 Polarity is active high. SPI initiator waits until P0.3 becomes high.

1 Polarity is active low. SPI initiator waits until P0.3 becomes low.

[3:2] Reserved Reserved. 0x0 R

Loading...

Loading...