Reference Manual ADuCM356

REGISTER DETAILS: SPI0/SPI1

analog.com Rev. A | 251 of 312

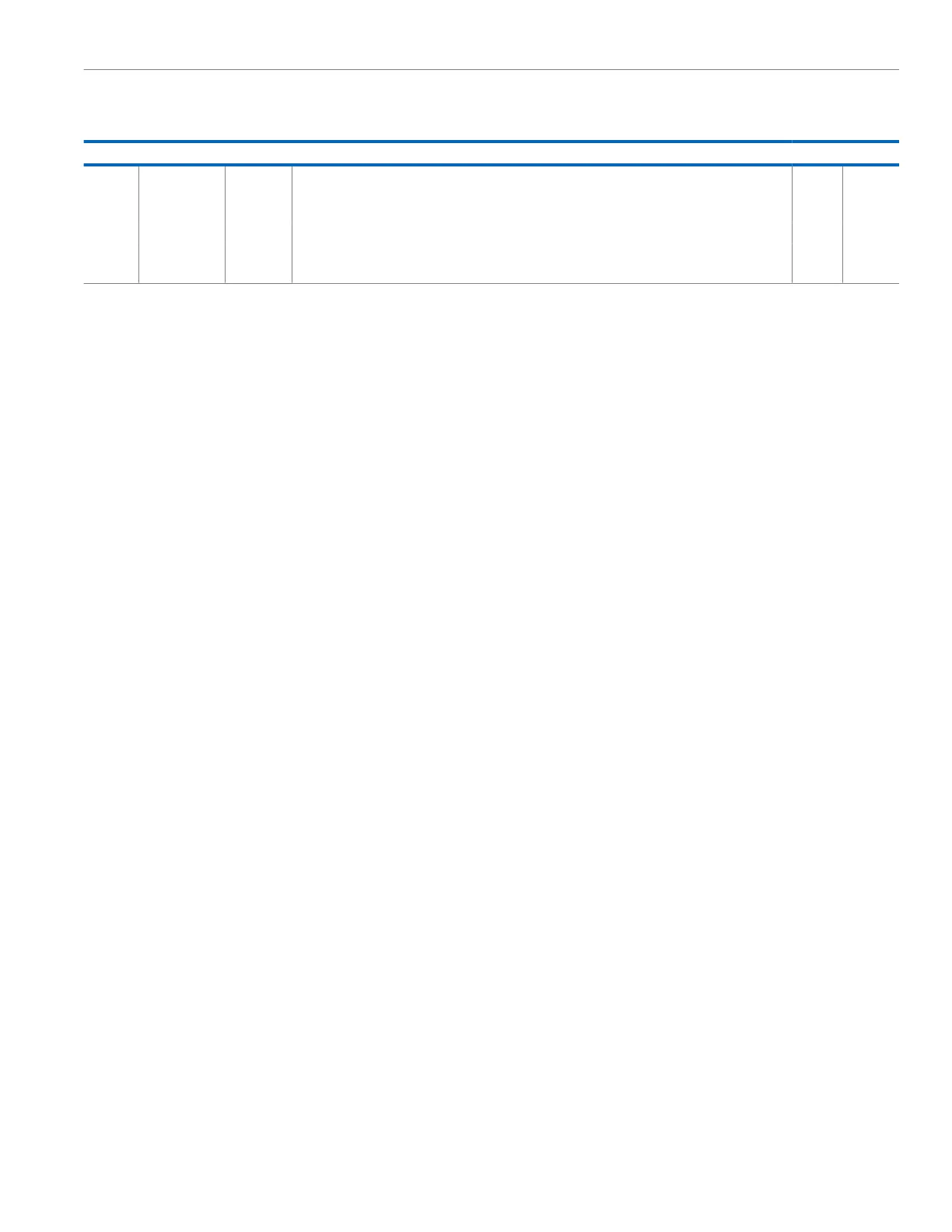

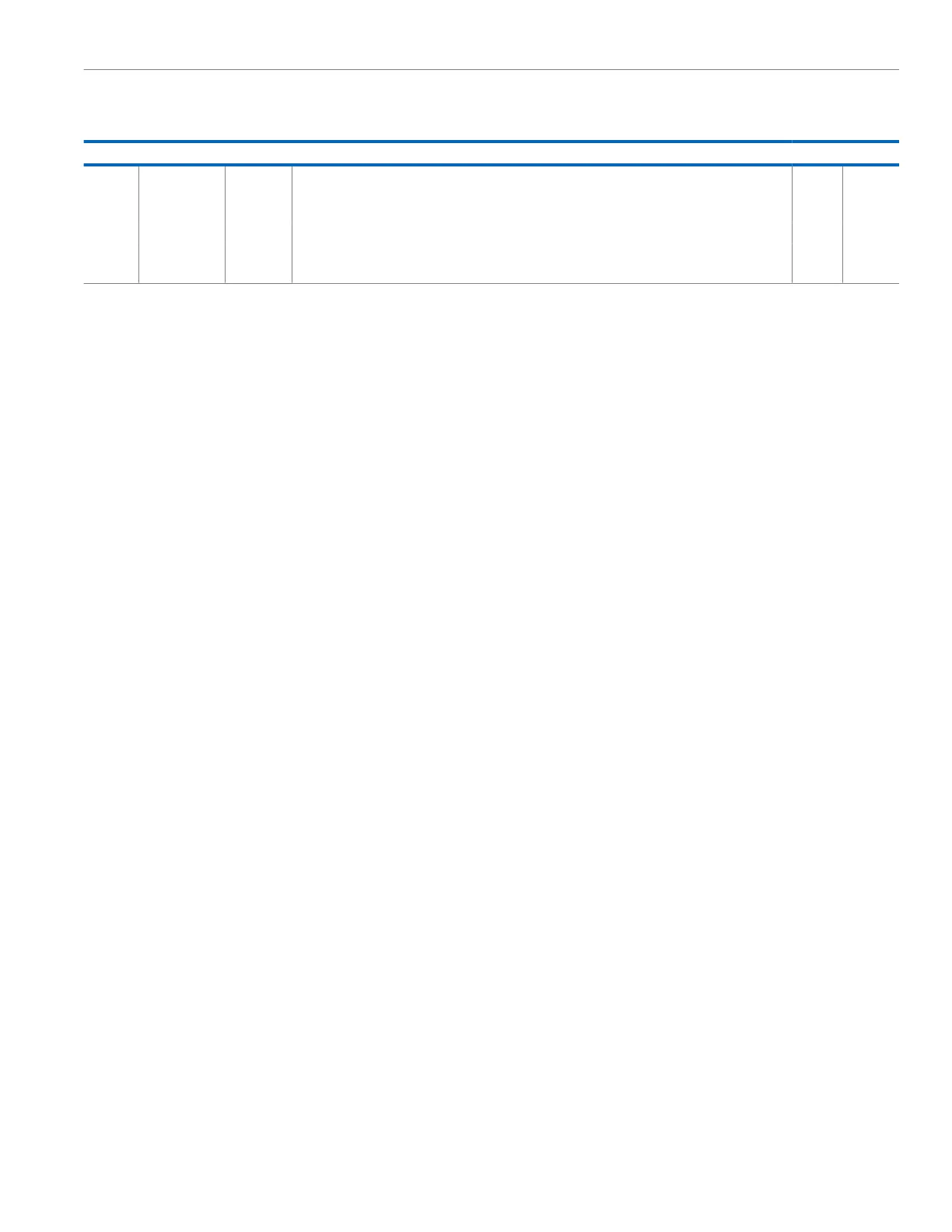

Table 316. Bit Descriptions for SPI0_FLOW_CTL, SPI1_FLOW_CTL (Continued)

Bits Bit Name Settings Description Reset Access

[1:0] MODE Flow Control Mode. Flow control configuration for data reads. When the P0.3 signal is used for flow

control, P0.3 can be any control signal that is tied to this P0.3 input of the SPI module.

0x0 R/W

00 Flow control is disabled.

01 Flow control is based on timer SPIx_WAIT_TMR.

10 Flow control is based on P0.3 signal.

11 Flow control is based on MISO pin.

Loading...

Loading...