Reference Manual ADuCM356

REGISTER DETAILS: ANALOG DIE GENERAL-PURPOSE TIMERS

analog.com Rev. A | 278 of 312

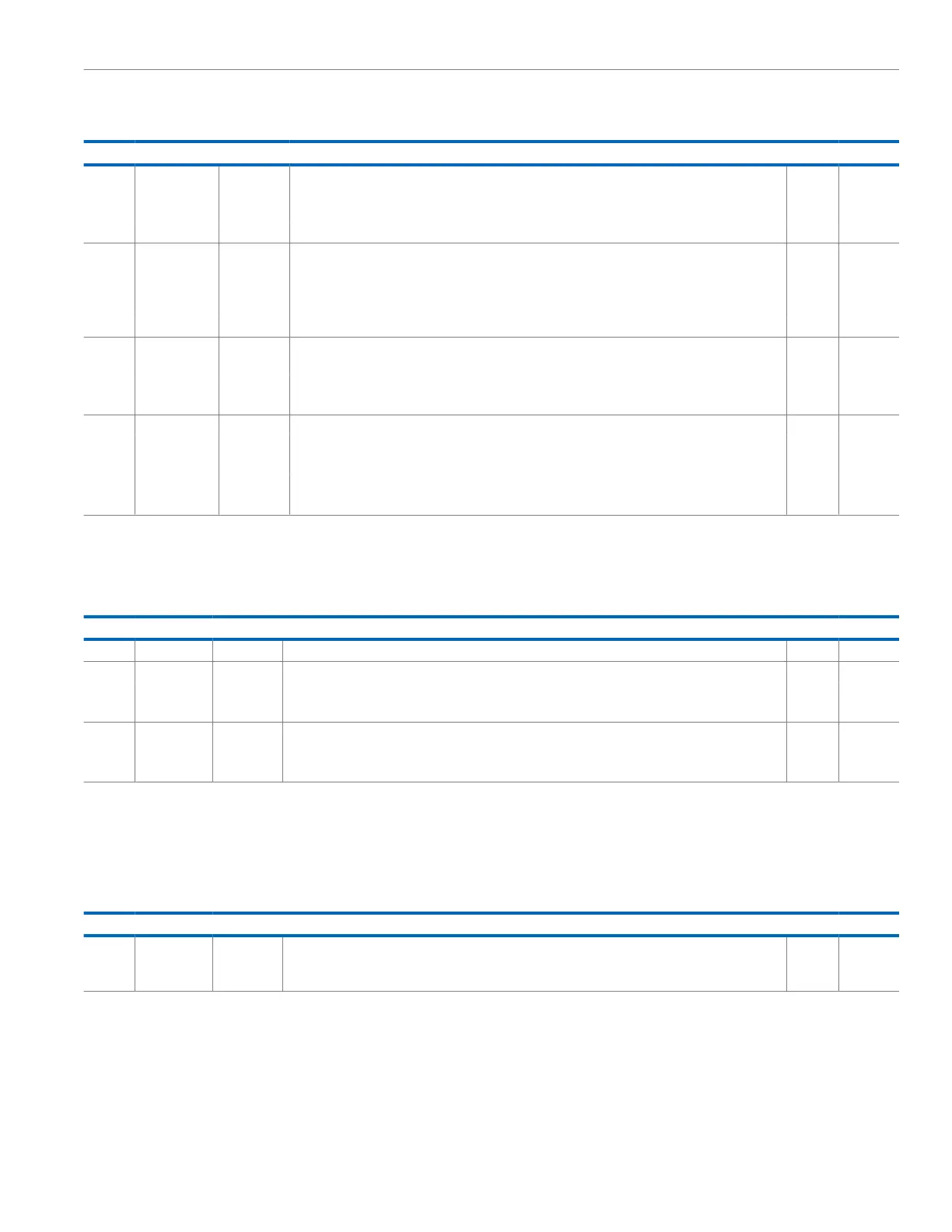

Table 365. Bit Descriptions for CTL (Continued)

Bits Bit Name Settings Description Reset Access

4 EN Timer Enable. Used to enable and disable the timer. Clearing this bit resets the timer, including the

CURCNT register.

0x0 R/W

0 Timer is disabled. Default.

1 Timer is enabled.

3 MODE Timer Mode. This bit is used to control whether the timer runs in periodic or free running mode. In

periodic mode, the up or down counter starts at the defined ALOAD, Bits[15:0]. In free running mode, the

up or down counter starts at 0x0000 or 0xFFFF, depending on whether the timer is counting up or down.

0x1 R/W

1 Timer runs in periodic mode. Default.

0 Timer runs in free running mode.

2 UP Count Up. Used to control whether the timer increments (counts up) or decrements (counts down) the up

or down counter.

0x0 R/W

1 Timer is set to count up.

0 Timer is set to count down. Default.

[1:0] PRE Prescaler. Controls the prescaler division factor applied to the selected clock of the timer. 0x2 R/W

00 Source clock/1 or source clock/4. When CTL, Bit 15 is set, source clock/1. When cleared, source clock/4.

01 Source clock/16.

10 Source clock/64.

11 Source clock/256.

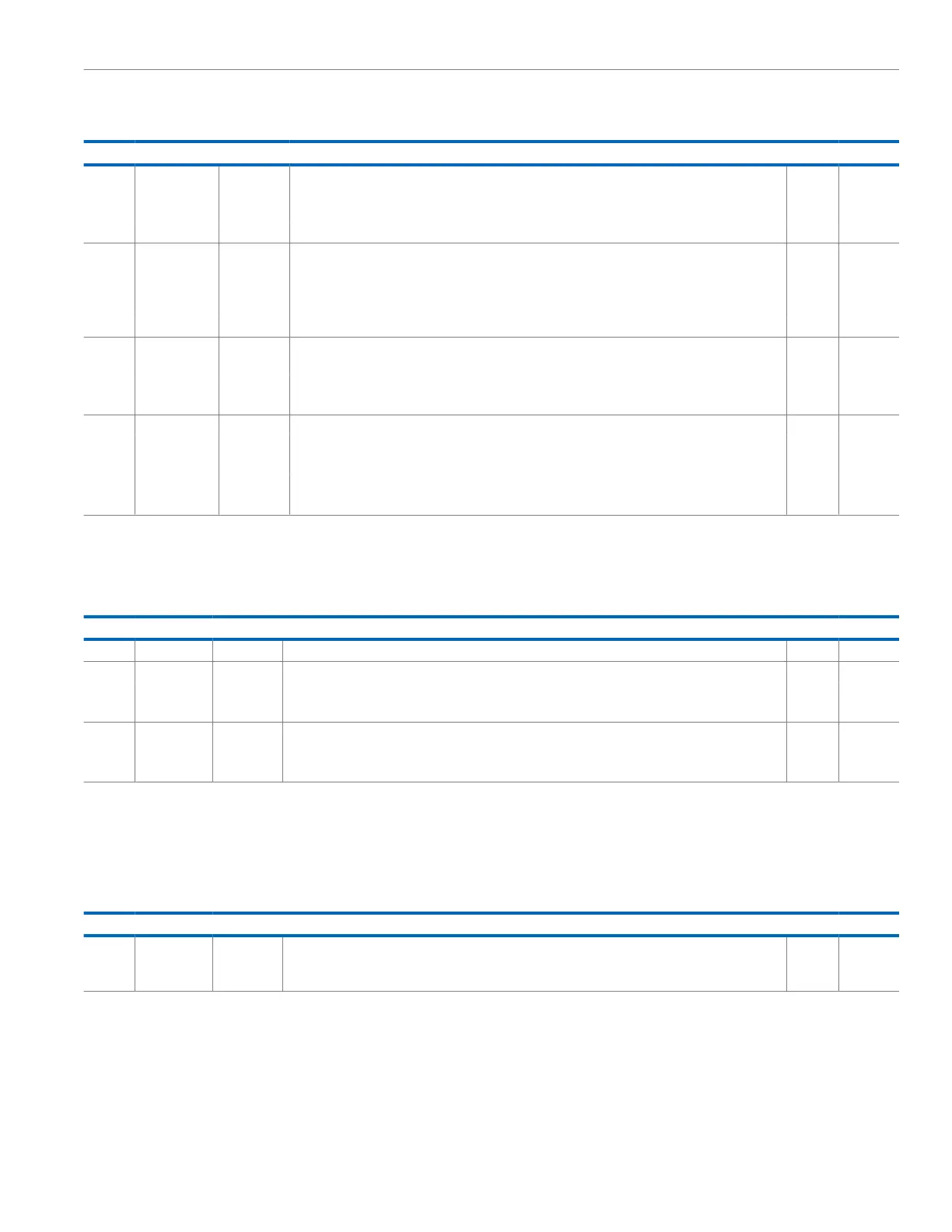

CLEAR INTERRUPT REGISTER

Address: 0x400C0E0C, Reset: 0x0000, Name: CLRINT

Table 366. Bit Descriptions for CLRINT

Bits Bit Name Settings Description Reset Access

[15:2] Reserved Reserved. 0x0 R

1 EVTCAPT Clear Captured Event Interrupt. This bit is used to clear a capture event interrupt. 0x0 W1C

1 Clear the capture event interrupt.

0 No effect.

0 TIMEOUT Clear Timeout Interrupt. This bit is used to clear a timeout interrupt. 0x0 W1C

1 Clears the timeout interrupt.

0 No effect.

16-BIT LOAD VALUE, ASYNCHRONOUS REGISTER

Address: 0x400C0E14, Reset: 0x0000, Name: ALOAD

Only use when a synchronous clock source is selected (CTL, Bits[6:5] = 00).

Table 367. Bit Descriptions for ALOAD

Bits Bit Name Settings Description Reset Access

[15:0] VALUE Load Value, Asynchronous. The up or down counter is periodically loaded with this value if periodic mode

is selected (CTL, Bit 5 = 1). Writing this register takes advantage of having the timer run on PCLK by

bypassing clock synchronization logic that is otherwise required.

0x0 R/W

16-BIT TIMER VALUE, ASYNCHRONOUS REGISTER

Address: 0x400C0E18, Reset: 0x0000, Name: ACURCNT

Only use when a synchronous clock source is selected (CTL, Bits[6:5] = 00).

Loading...

Loading...