Reference Manual ADuCM356

REGISTER DETAILS: CLOCK ARCHITECTURE

analog.com Rev. A | 16 of 312

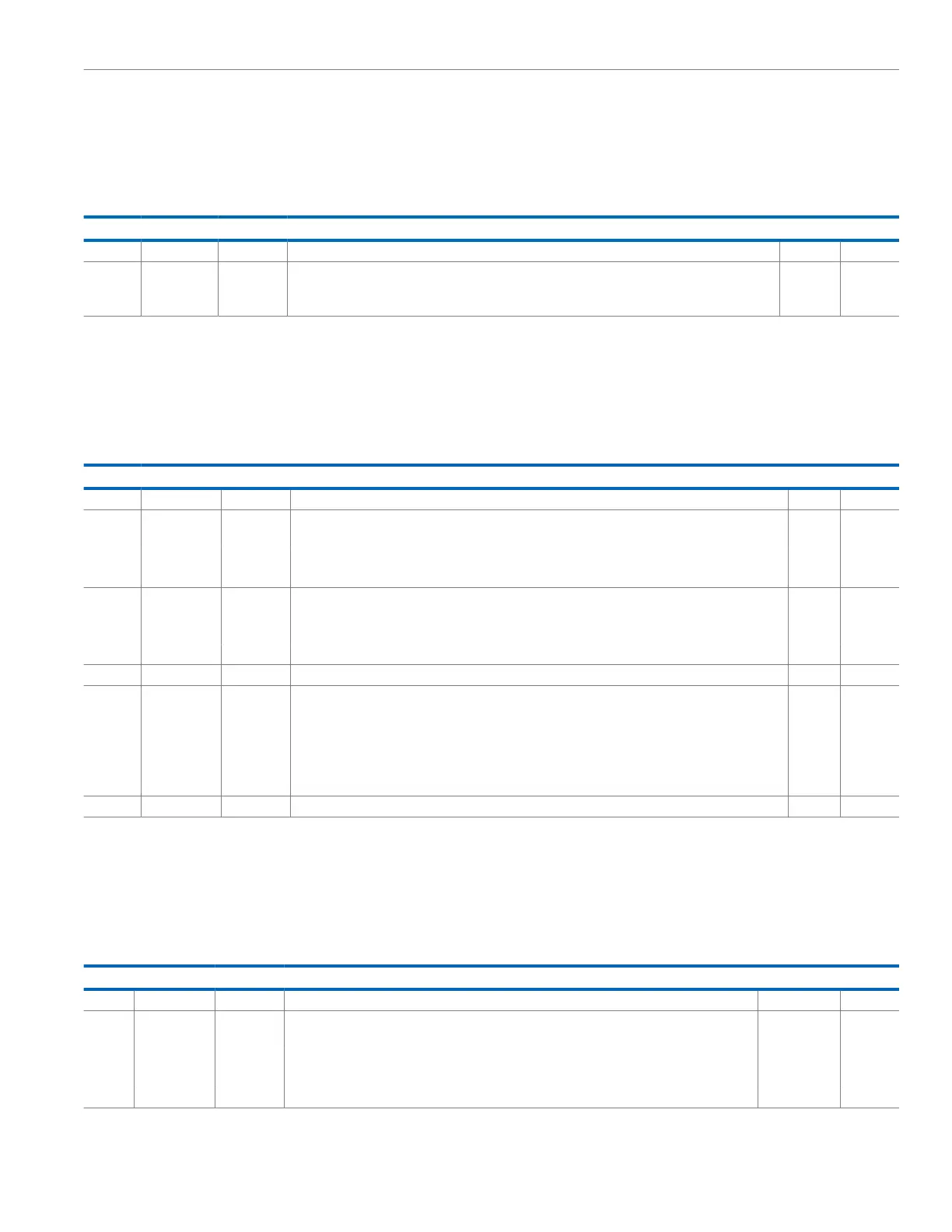

KEY PROTECTION FOR CTL REGISTER

Address: 0x4004C10C, Reset: 0x00000000, Name: KEY

Table 5. Bit Descriptions for KEY

Bits Bit Name Settings Description Reset Access

[31:16] Reserved Reserved. 0x0000 R

[15:0] VALUE 0xCB14 Oscillator Key. The CTL register is key protected. To unlock this protection, write 0xCB14 to KEY before

writing to CTL. A write to any other register on the Arm peripheral bus before writing to CTL returns the

protection to the lock state.

0x0000 W

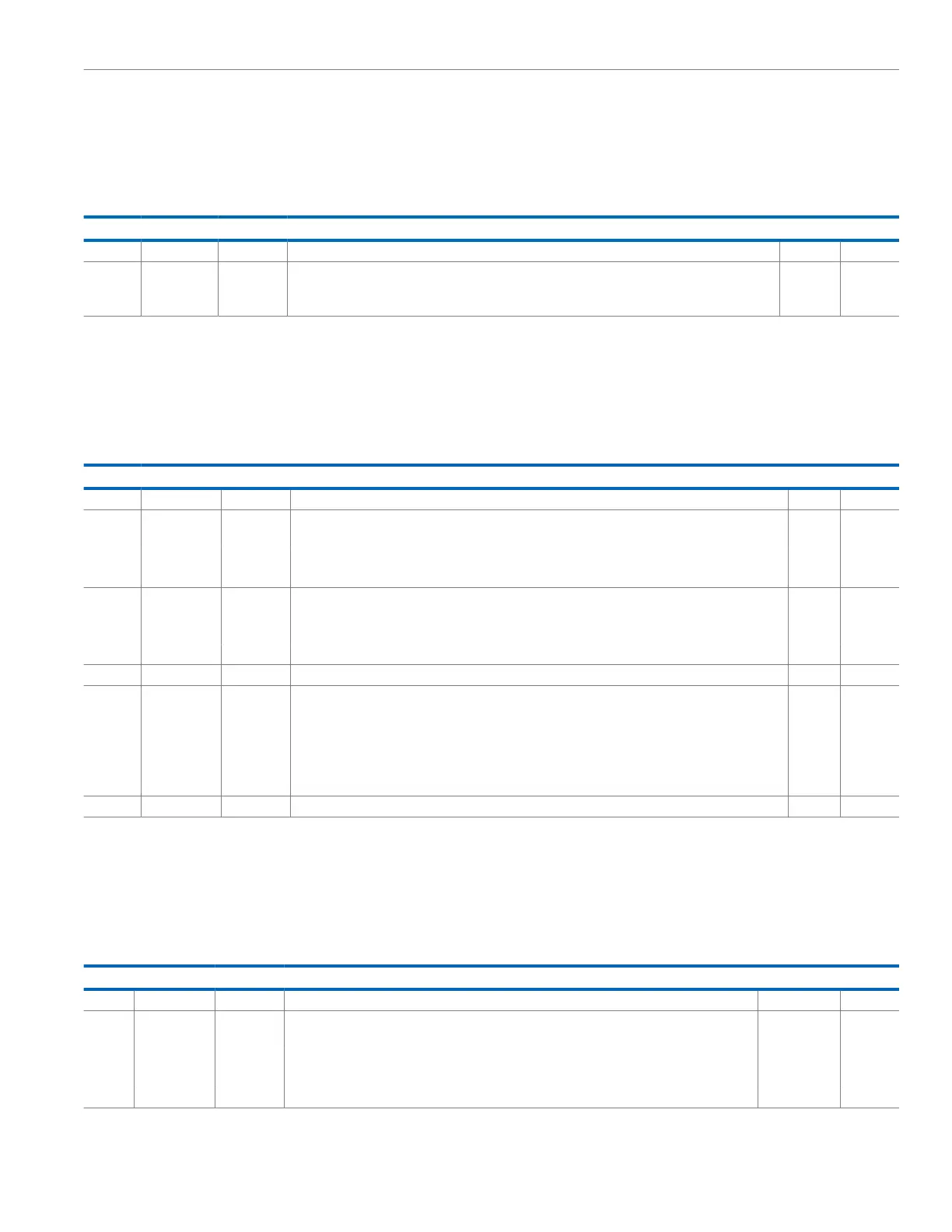

OSCILLATOR CONTROL REGISTER

Address: 0x4004C110, Reset: 0x00000302, Name: CTL

The CTL register is key protected. To unlock this protection, write 0xCB14 to KEY before writing to the CTL register. A write to any other register

on the Arm peripheral bus before writing to the CTL register returns the protection to the lock state.

Table 6. Bit Descriptions for CTL

Bits Bit Name Settings Description Reset Access

[31:10] Reserved Reserved. 0x0 R

9 HFOSCOK Status of High Frequency Oscillator on Digital Die. This bit indicates when the oscillator is stable after it

is enabled. This bit is not a monitor and does not indicate a subsequent loss of stability.

0x1 R

0 Oscillator is not yet stable or is disabled.

1 Oscillator is enabled, stable, and ready for use.

8 LFOSCOK Status of Low Frequency Oscillator on Digital Die. This bit indicates when the oscillator is stable after it is

enabled. This bit is not a monitor and does not indicate a subsequent loss of stability.

0x1 R

0 Oscillator is not yet stable or is disabled.

1 Oscillator is enabled, stable, and ready for use.

[7:2] Reserved Reserved. 0x0 R

1 HFOSCEN High Frequency Internal Oscillator Enable. This bit is used to enable and disable the high frequency

oscillator on the digital die. The oscillator must be stable before use. This bit must be set before the

SYSRESETREQ system reset can be initiated. SYSRESETREQ is a bit in the Arm Cortex-M3 AIRCR

register.

0x1 R/W

0 The high frequency oscillator is disabled and placed in a low-power state.

1 The high frequency oscillator is enabled.

0 Reserved Reserved. This bit must always be 0. 0x0 R/W

CLOCK CONTROL 0 REGISTER

Address: 0x4004C300, Reset: 0x00000078, Name: CTL0

The Clock Control 0 register is used to configure clock sources used by various systems, such as the core, memories, and peripherals. All

unused bits are read only and return a value of 0. Writing unused bits has no effect.

Table 7. Bit Descriptions for CTL0

Bits Bit Name Settings Description Reset Access

[31:2] Reserved Reserved. 0x0000000 R

[1:0] CLKMUX Clock Mux Select. Determines which single shared clock source is used by the gated system clock

(peripheral clock (PCLK) on digital die) and high-speed clock (HCLK) dividers.

0x0 R/W

00 High frequency internal oscillator is selected.

01, 10 Reserved.

11 External clock routed from analog die. Can be external crystal or clock source.

Loading...

Loading...