Reference Manual ADuCM356

REGISTER DETAILS: SPI0/SPI1

analog.com Rev. A | 248 of 312

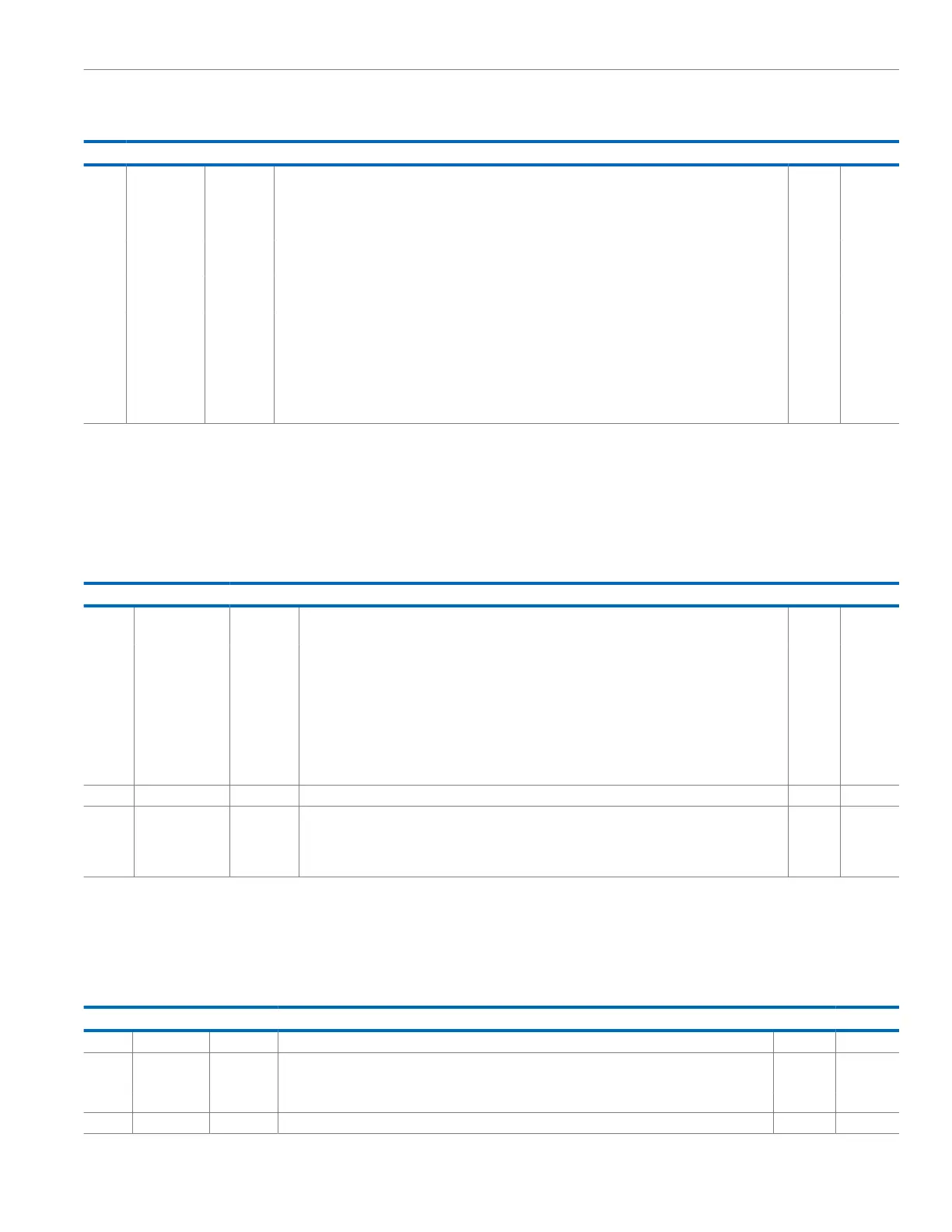

Table 311. Bit Descriptions for SPI0_IEN, SPI1_IEN (Continued)

Bits Bit Name Settings Description Reset Access

001 Transmit interrupt occurs when 2 bytes have been transferred. Receive interrupt occurs when 2 or more

bytes have been received into the FIFO.

010 Transmit interrupt occurs when 3 bytes have been transferred. Receive interrupt occurs when 3 or more

bytes have been received into the FIFO.

011 Transmit interrupt occurs when 4 bytes have been transferred. Receive interrupt occurs when 4 or more

bytes have been received into the FIFO.

100 Transmit interrupt occurs when 5 bytes have been transferred. Receive interrupt occurs when 5 or more

bytes have been received into the FIFO.

101 Transmit interrupt occurs when 6 bytes have been transferred. Receive interrupt occurs when 6 or more

bytes have been received into the FIFO.

110 Transmit interrupt occurs when 7 bytes have been transferred. Receive interrupt occurs when 7 or more

bytes have been received into the FIFO.

111 Transmit interrupt occurs when 8 bytes have been transferred. Receive interrupt occurs when the FIFO is

full.

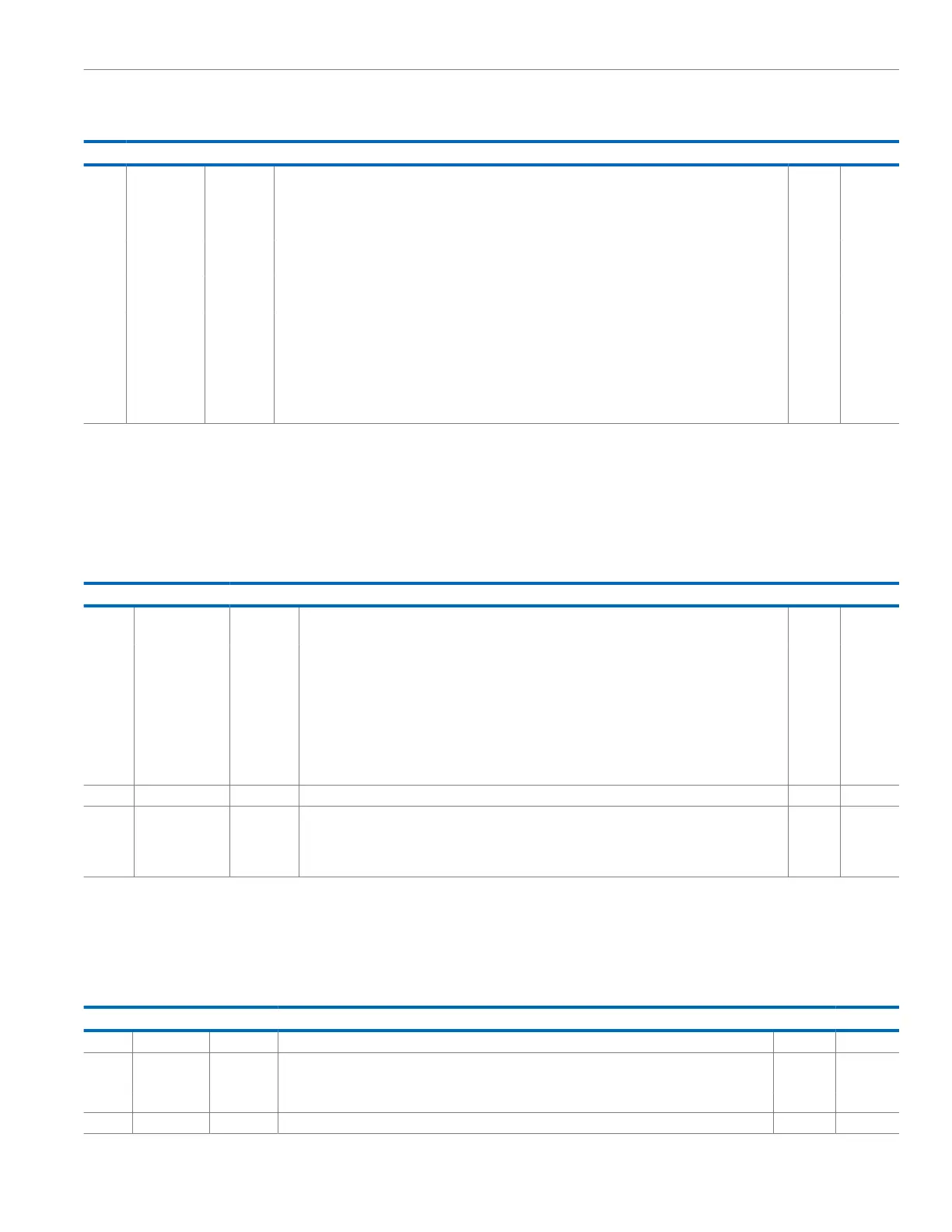

TRANSFER BYTE COUNT REGISTERS

Address: 0x40004018, Reset: 0x0000, Name: SPI0_CNT

Address: 0x40024018, Reset: 0x0000, Name: SPI1_CNT

This register is only used in initiator mode.

Table 312. Bit Descriptions for SPI0_CNT, SPI1_CNT

Bits Bit Name Settings Description Reset Access

15 FRAMECONT Continue Frame. Use this bit in conjunction with the SPIx_CTL, Bit 11 and SPIx_CNT, Bits[13:0] fields.

This bit is used to control SPI data framing.

0x0 R/W

0 When writing to this bit, if this bit is cleared, the SPI initiator transfers only one frame of SPIx_CNT,

Bits[13:0]. When reading this bit, if the value bits > 0, stop SPI transfers after the specified number of

bytes.

1 When writing to this bit, the SPI initiator transfers data in frames of SPIx_CNT, Bits[13:0] bytes per

frame. If SPIx_CNT, Bits[13:0] = 0, this field has no effect because the SPI initiator continues with

transfers as long as the transmit or receive FIFO is ready. If SPIx_CTL, Bit 11 = 0, this field has no

effect because all SPI frames are a single byte wide, irrespective of other control fields. When reading

this bit, continue SPI transfers as long as the transmit or receive FIFO is ready.

14 Reserved Reserved. 0x0 R

[13:0] VALUE Transfer Byte Count. This field specifies the number of bytes to be transferred. It is used in both

receive and transmit transfer types. This value ensures that an initiator mode transfer terminates at the

proper time and that 16-bit SPIx_DMA transfers are byte padded or discarded as required to match

odd transfer counts. Reset by clearing SPIx_CTL, Bit 0 to 0.

0x0 R/W

DMA ENABLE REGISTERS

Address: 0x4000401C, Reset: 0x0000, Name: SPI0_DMA

Address: 0x4002401C, Reset: 0x0000, Name: SPI1_DMA

Table 313. Bit Descriptions for SPI0_DMA, SPI1_DMA

Bits Bit Name Settings Description Reset Access

[15:3] Reserved Reserved. 0x0 R

2 RXEN Enable Receive DMA Request. 0x0 R/W

0 Disable receive DMA interrupt.

1 Enable receive DMA interrupt.

1 TXEN Enable Transmit DMA Request. 0x0 R/W

Loading...

Loading...