Reference Manual ADuCM356

REGISTER DETAILS: I

2

C

analog.com Rev. A | 235 of 312

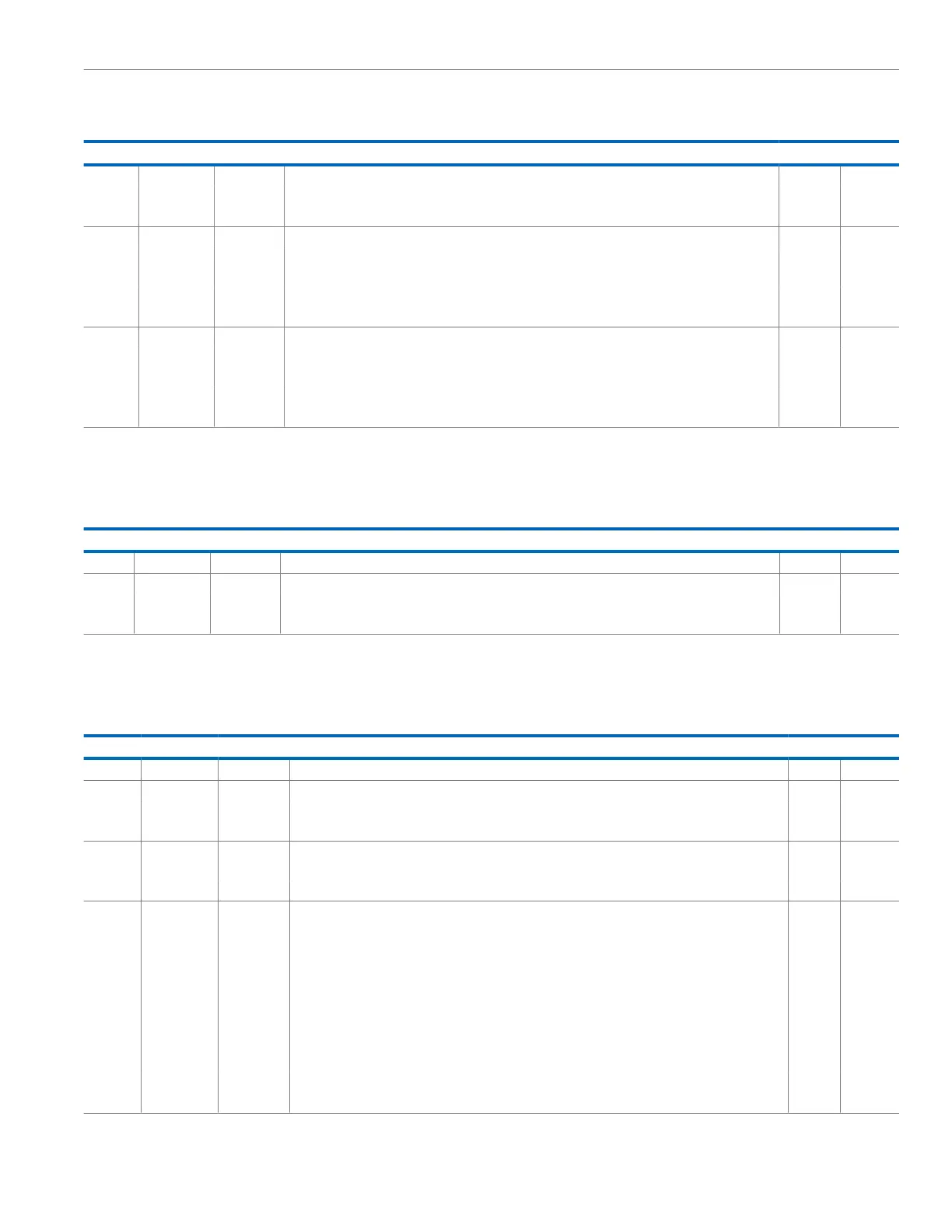

Table 301. Bit Descriptions for FSTAT (Continued)

Bits Bit Name Settings Description Reset Access

01 1 byte in the FIFO.

10 2 bytes in the FIFO.

11 Reserved.

[3:2] SRXF Target Receive FIFO Status. The status is a count of the number of bytes in a FIFO. 0x0 R

00 FIFO empty.

01 1 byte in the FIFO.

10 2 bytes in the FIFO.

11 Reserved.

[1:0] STXF Target Transmit FIFO Status. The status is a count of the number of bytes in a FIFO. 0x0 R

00 FIFO empty.

01 1 byte in the FIFO.

10 2 bytes in the FIFO.

11 Reserved.

INITIATOR AND TARGET SHARED CONTROL REGISTER

Address: 0x40003050, Reset: 0x0000, Name: SHCTL

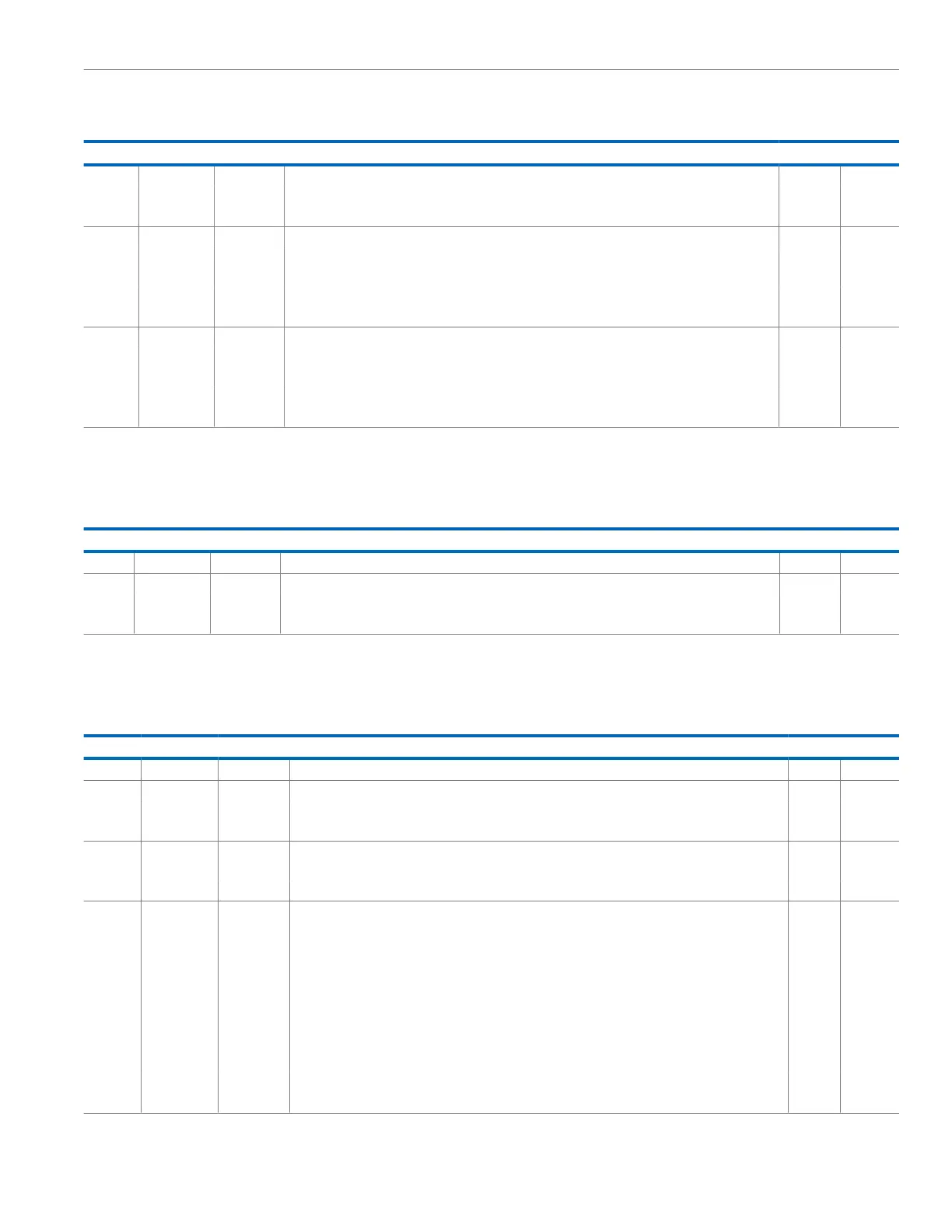

Table 302. Bit Descriptions for SHCTL

Bits Bit Name Settings Description Reset Access

[15:1] Reserved Reserved. 0x0000 R/W

0 RST Reset LINEBUSY. Setting this bit resets the LINEBUSY status bit (Bit 10 in the MSTAT register). 0x0 W

0 No effect.

1 Reset the I

2

C start and stop detection circuits.

AUTOMATIC STRETCH CONTROL FOR INITIATOR AND TARGET MODE REGISTER

Address: 0x40003058, Reset: 0x0000, Name: ASTRETCH_SCL

Table 303. Bit Descriptions for ASTRETCH_SCL

Bits Bit Name Settings Description Reset Access

[15:10] Reserved Reserved. 0x0 R

9 SLVTMO Stretch Timeout Status Bit for Target. 0x0 R

0 Cleared when this bit is read.

1 Set when target automatic stretch mode has timed out.

8 MSTTMO Stretch Timeout Status Bit for Initiator. 0x0 R

0 Cleared when this bit is read.

1 Set when initiator automatic stretch mode has timed out.

[7:4] SLV Automatic Stretch Mode Control for Target. These bits control automatic stretch mode for target

operation. These bits allow the target to hold the I2C_SCL line low and gain more time to service an

interrupt, load a FIFO, or read a FIFO. Use the timeout feature to avoid a bus lockup condition where the

target indefinitely holds I2C_SCL low. As a target transmitter, I2C_SCL is automatically stretched from

the negative edge of I2C_SCL (if the target transmit FIFO is empty) before sending an acknowledge or

a no acknowledge for an address byte, or before sending data for a data byte. Stretching stops when

the target transmit FIFO is no longer empty or a timeout occurs. As a target receiver, the I2C_SCL clock

is automatically stretched from the negative edge of I2C_SCL before sending an acknowledge or a no

acknowledge when the target receive FIFO is full. Stretching stops when the target receive FIFO is no

longer in an overflow condition or a timeout occurs.

0x0 R/W

0000 Automatic target clock stretching disabled.

0001 to 1110 Automatic target clock stretching enabled. The timeout period is defined as follows:

Loading...

Loading...