Reference Manual ADuCM356

REGISTER DETAILS: FLASH CACHE CONTROLLER (FLCC)

analog.com Rev. A | 192 of 312

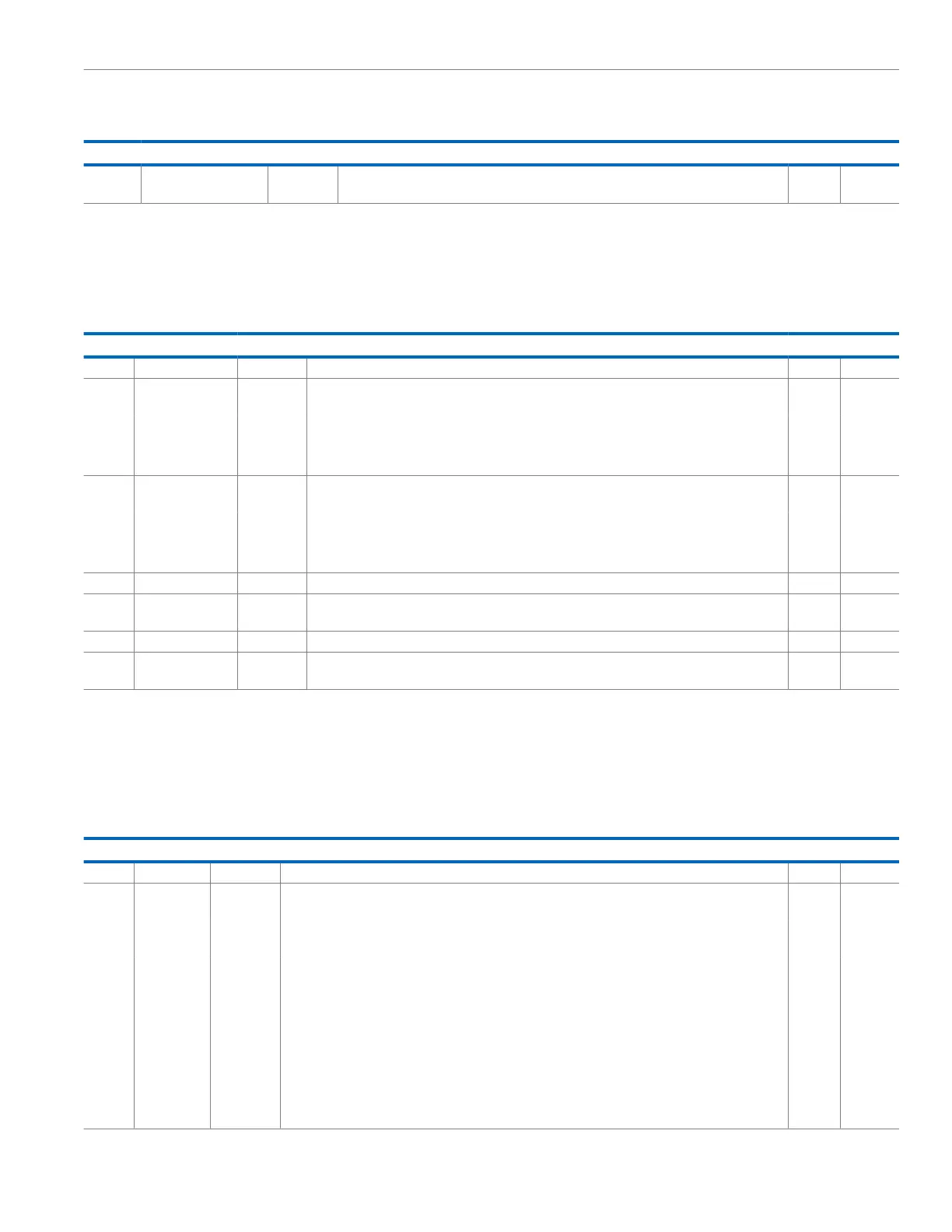

Table 224. Bit Descriptions for STAT (Continued)

Bits Bit Name Settings Description Reset Access

and this bit asserting. Watch the CMDCOMP bit rather than this bit when polling for command

completion.

INTERRUPT ENABLE REGISTER

Address: 0x40018004, Reset: 0x40, Name: IEN

Used to specify when interrupts are generated.

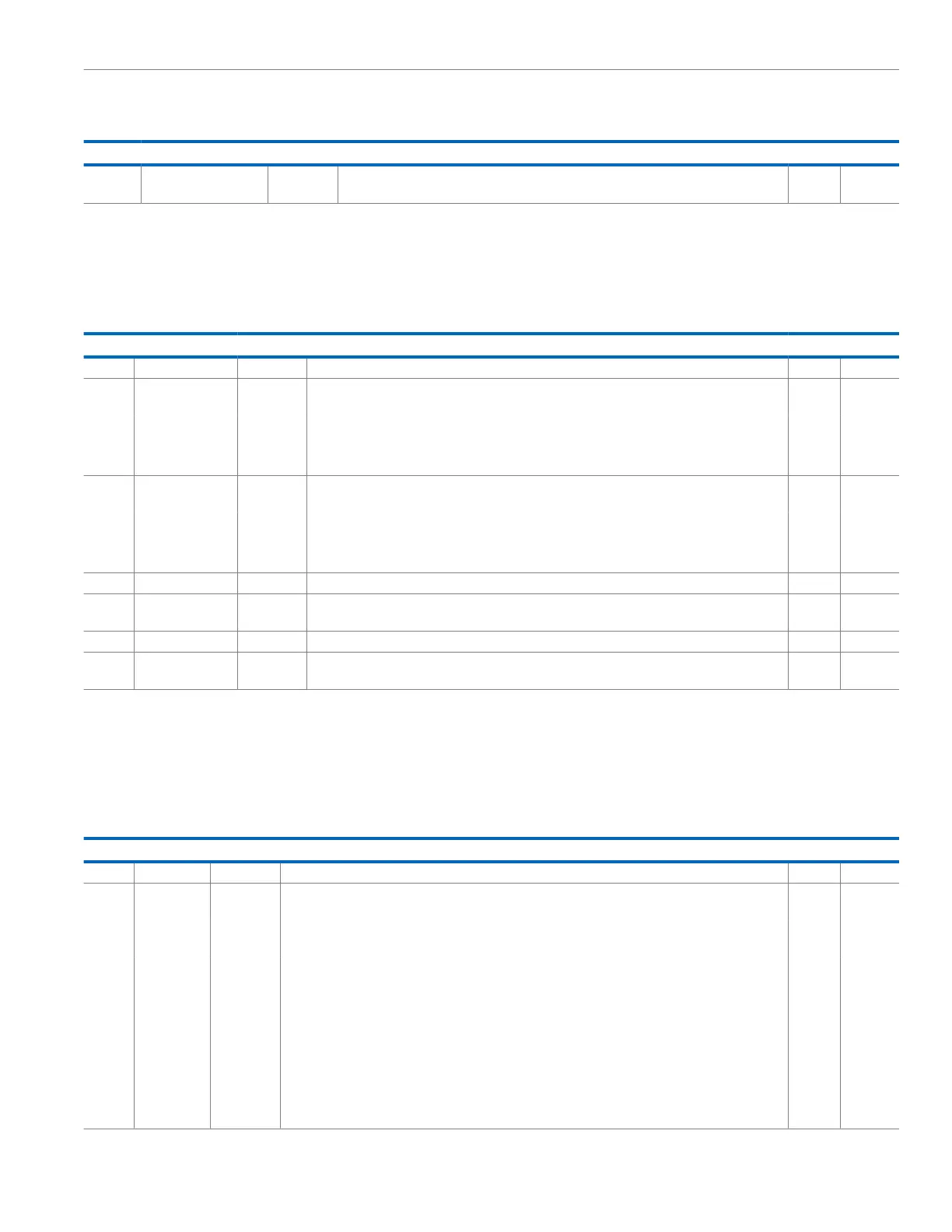

Table 225. Bit Descriptions for IEN

Bits Bit Name Settings Description Reset Access

[31:8] Reserved Reserved. 0x0 R

[7:6] ECC_ERROR Control Whether to Generate Bus Errors, Interrupts, or Neither in Response to 2-Bit ECC Error

Events.

0x1 R/W

0 Do not generate a response to ECC events.

1 Generate bus errors in response to ECC events.

10 Generate IRQs in response to ECC events.

[5:4] ECC_CORRECT Control Whether to Generate Bus Errors, Interrupts, or Neither in Response to 1-Bit ECC Correction

Events.

0x0 R/W

0 Do not generate a response to ECC events.

1 Generate bus errors in response to ECC events.

10 Generate IRQs in response to ECC events.

3 Reserved Reserved. 0x0 R

2 CMDFAIL Command Fail Interrupt Enable. If this bit is set, an interrupt is generated when a command or flash

write completes with an error status.

0x0 R/W

1 WRALCMPLT Write Almost Complete Interrupt Enable. 0x0 R/W

0 CMDCMPLT Command Complete Interrupt Enable. When set, an interrupt is generated when a command or flash

write completes.

0x0 R/W

COMMAND REGISTER

Address: 0x40018008, Reset: 0x00000000, Name: CMD

Write this register to execute a specified command. The user key must first be written to the key register for most command requests to be

honored. See the Key Register section for details.

Table 226. Bit Descriptions for CMD

Bits Bit Name Settings Description Reset Access

[31:4] Reserved Reserved. 0x0 R

[3:0] VALUE Commands. Write command values to this register to begin a specific operation. All commands except

write and idle first require writing the user key to the key register.

0x0 R/W

0x0 Idle. No key is required. No command executed. If flash IP is in the sleep state, this command wakes the

flash by returning command complete and no error codes.

0x1 Abort. User key is required. Use the abort command sparingly to gain access to the flash IP during time

sensitive events. For example, a low voltage alarm can abort an ongoing flash write or erase command

to enable user code to shut down the device. The flash array can be damaged by overuse of the abort

command. If this command is issued, any command currently in progress stops abruptly, if possible. The

status indicates a command was completed with an abort error. Abort is the only command that can be

issued while another command is already in progress, with the exception of stacking one write command

on top of a single ongoing write command. All other overlapping command combinations are invalid unless

the new command is an abort. If a write or erase is aborted, some flash IP timing requirements can be

violated and it is not possible to determine if the write or erase completed. Read the affected locations to

determine the outcome of the aborted commands. An aborted command can result in a weak programmed

Loading...

Loading...