Reference Manual ADuCM356

REGISTER DETAILS: FLASH CACHE CONTROLLER (FLCC)

analog.com Rev. A | 191 of 312

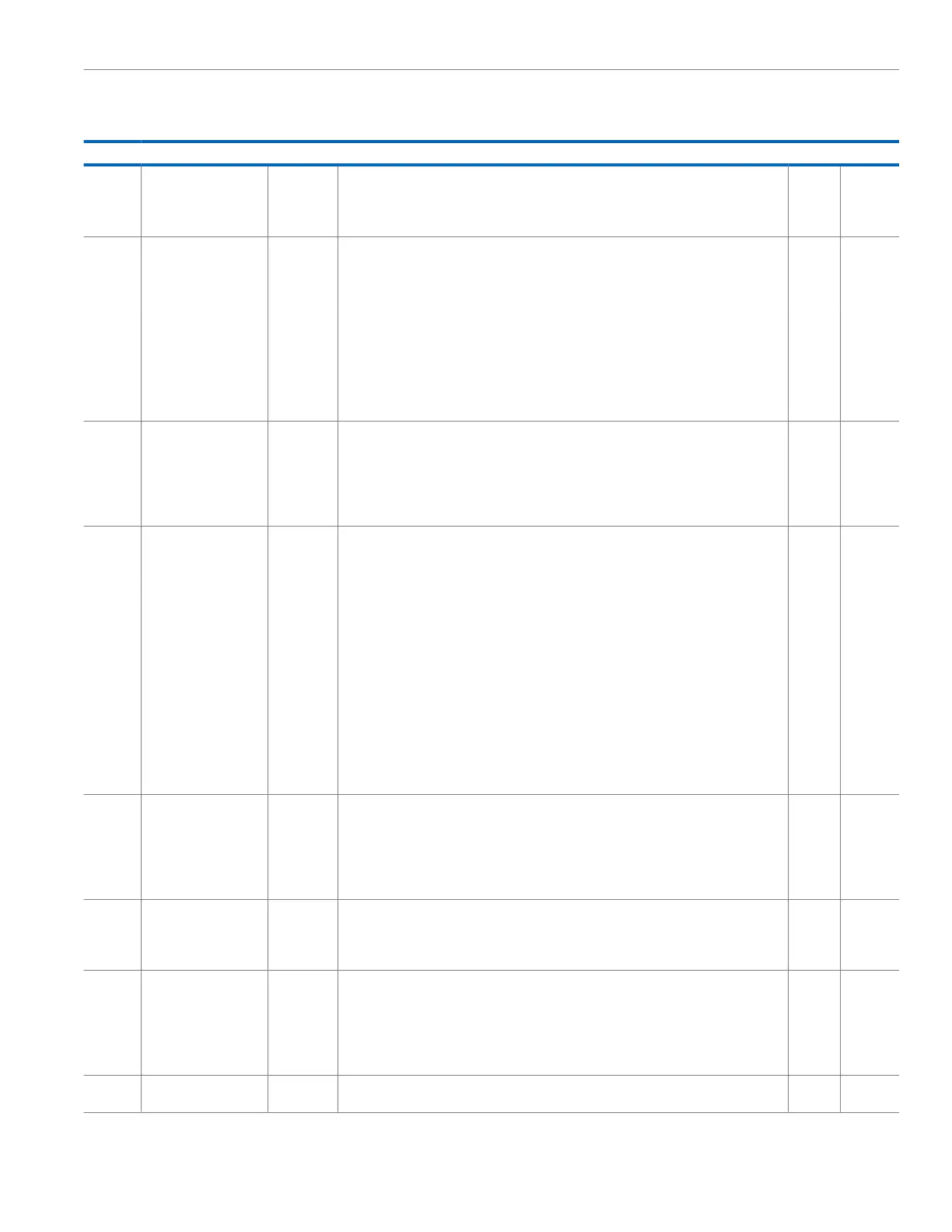

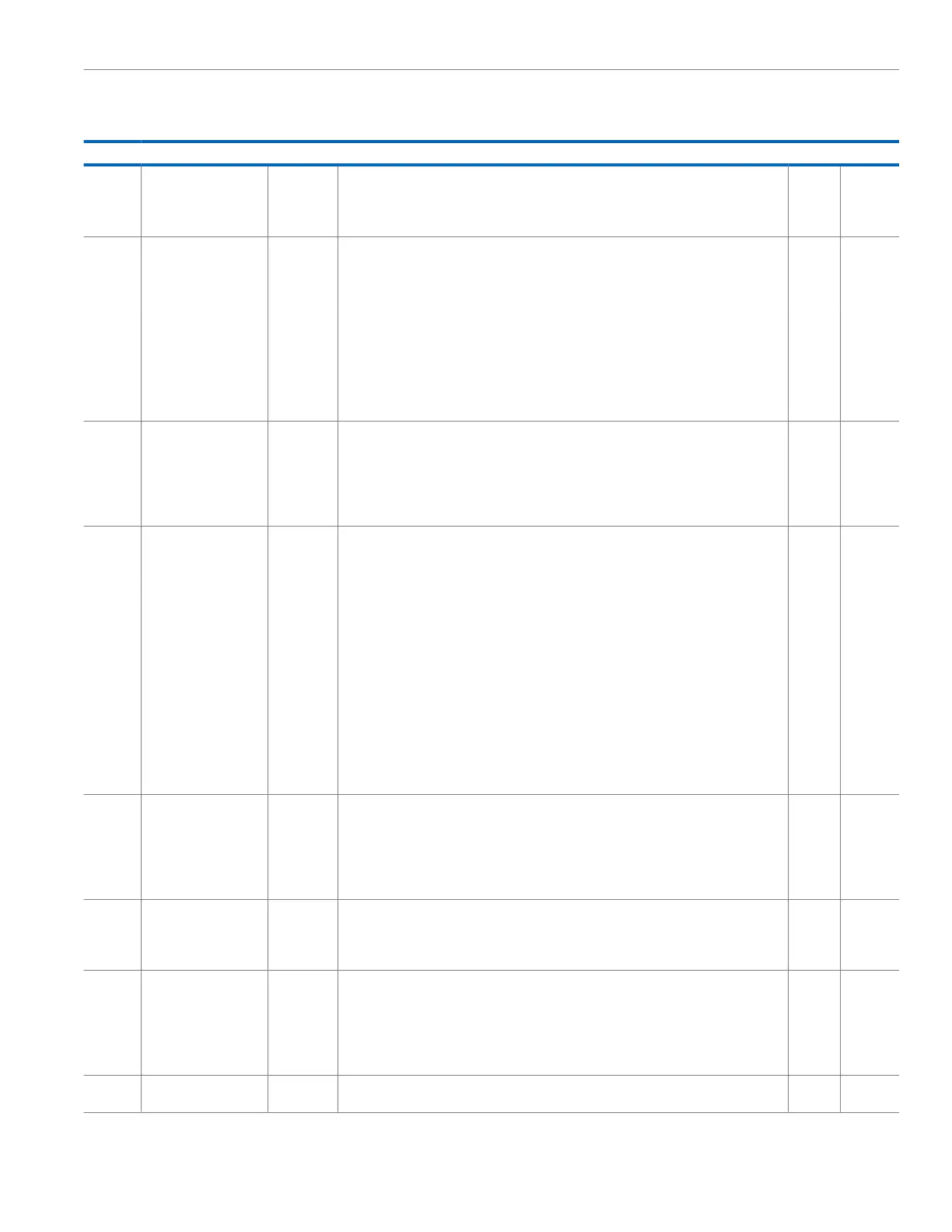

Table 224. Bit Descriptions for STAT (Continued)

Bits Bit Name Settings Description Reset Access

subsequent AHB read access incurred the alternate ECC error event. By default, 1-bit ECC

corrections are reported as IRQs and 2-bit ECC errors are reported as bus faults. It is not

recommended to report both types as IRQs, because the status bits become ambiguous when

trying to diagnose which fault came first.

[8:7] ECCERRCMD ECC Errors Detected During User Issued Sign Command. ECC errors, if produced during

signature commands, are reported by these bits. To generate interrupts based on these bits,

set the corresponding bits in the IEN register.

0x0 R/W1C

00 No error, completed flash read operation during signature check.

01 2-bit error. During signature commands, 2-bit error is detected on one or more flash locations,

not corrected.

10 1-bit error. 1-bit error is corrected for one or more flash locations while performing signature

commands.

11 1-bit or 2-bit error. During signature commands, 1-bit and 2-bit errors are detected on one or

more flash locations.

6 SLEEPING Flash Array is in Low-Power (Sleep) Mode. Indicates that the flash array is in a low-power

(sleep) mode. The flash controller automatically wakes the flash when required for another

data transaction. The user can wake the flash at any time by writing the idle command to the

CMD register. Flash wake-up times vary but are typically approximately 5 μs. When possible, it

is recommended that the user begin waking the flash approximately 5 μs before it is used for

performance optimization.

0x0 R

[5:4] CMDFAIL Provides Information on Command Failures. This field indicates the status of a command upon

completion. If multiple commands are executed without clearing these bits, only the first error

encountered is stored.

0x0 R/W1C

00 Complete. Completion of a command.

01 Ignored. Attempted access of a protected or out of memory location is ignored.

10 Verify error. Read verify error occurred. This status returns for both failed erasure and failed

signature check. In the case of failed erasure, after erasing flash page(s), the controller reads

the corresponding word(s) to verify that the erasure completed. If data persists, the erasure

has failed and this field reports the failure. In the case of a failed signature check, if the sign

command is executed and the resulting signature does not match the data stored in the most

significant 32-bit word of the sign checked block, the sign check has failed and this field reports

the failure.

11 Abort. Indicates a command was aborted either by user code or by a system interrupt. See

the IRQ Abort Enable (Lower Bits) Register section and the IRQ Abort Enable (Upper Bits)

Register section for more details.

3 WRALCOMP Write Almost Complete. Write data registers are reopened for access as an ongoing write

nears completion. Requesting another write operation before the CMDCOMP bit asserts

results in a burst write. Burst writes take advantage of low level protocols of the flash memory

and result in significant performance gains (approximately 15 μs saved from each write

operation). The performance gain of a burst write only applies to back to back writes within the

same row of the flash array.

0x0 R/W1C

2 CMDCOMP Command Complete. This bit asserts when a command completes. It automatically clears

when a new command is requested. Following a POR, the flash controller performs a number

of operations, such as verifying the integrity of code in information space. At the conclusion of

this process, the controller sets this bit to indicate that the process has completed.

0x0 R/W1C

1 WRCLOSE Write Registers are Closed. The write data registers (KH_DATA0 and KH_DATA1), address

register (KH_ADDR), and command register (CMD) are closed for access. This bit is asserted

part of the time while a write is in progress. If this bit is high, the related registers are in use

by the flash controller and cannot be written. This bit clears when the WRALCOMP flag goes

high, indicating that the ongoing write command has consumed the associated data and these

registers can now be overwritten with new data.

0x0 R

0 CMDBUSY Command Busy. This bit is asserted when the flash block is actively executing any command

entered via the command register. There is a slight delay between requesting a command

0x0 R

Loading...

Loading...