Reference Manual ADuCM356

REGISTER DETAILS: AFE WATCHDOG TIMER

analog.com Rev. A | 285 of 312

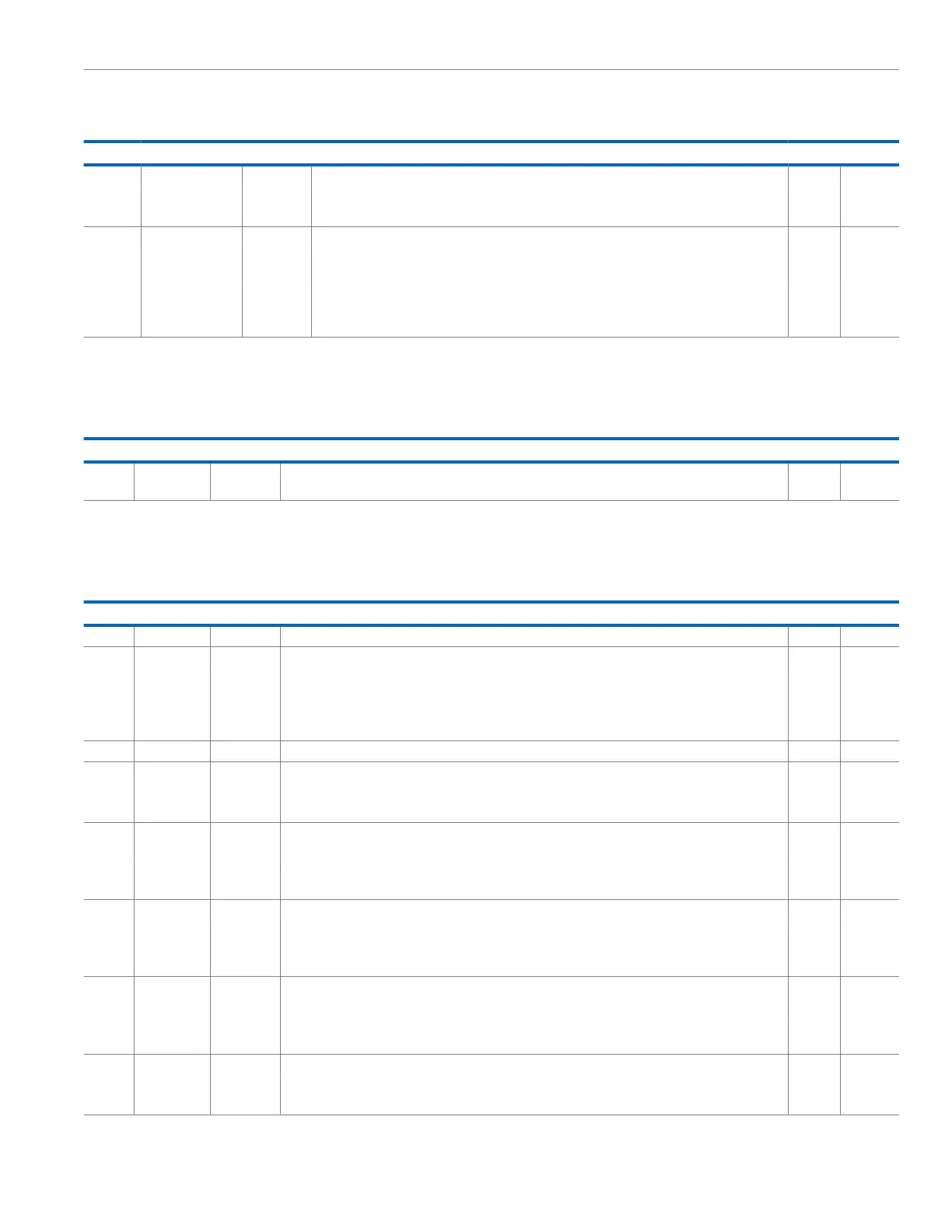

Table 375. Bit Descriptions for WDTCON (Continued)

Bits Bit Name Settings Description Reset Access

1 IRQ WDT Interrupt Enable. 0x0 R/W

0 Watchdog timer timeout creates a reset.

1 Watchdog timer timeout creates an interrupt instead of a reset.

0 PDSTOP Power Down Stop Enable. 0x1 R/W

0 Continue counting when in hibernate mode. The watchdog timer continues its count down while in

hibernate mode.

1 Stop counter when in hibernate mode. When hibernate mode is entered, the watchdog counter

suspends its countdown. As hibernate mode is exited, the countdown resumes from its current count

value (the count is not reset).

REFRESH WATCHDOG REGISTER

Address: 0x400C090C, Reset: 0x0000, Name: WDTCLRI

Table 376. Bit Descriptions for WDTCLRI

Bits Bit Name Settings Description Reset Access

[15:0] CLRWDG Refresh Register. User writes 0xCCCC to reset, reload, or restart the counter or clear the IRQ. A write of

any other value causes a watchdog reset or IRQ. Write only, reads 0.

0x0 W

TIMER STATUS REGISTER

Address: 0x400C0918, Reset: 0x0000, Name: WDTSTA

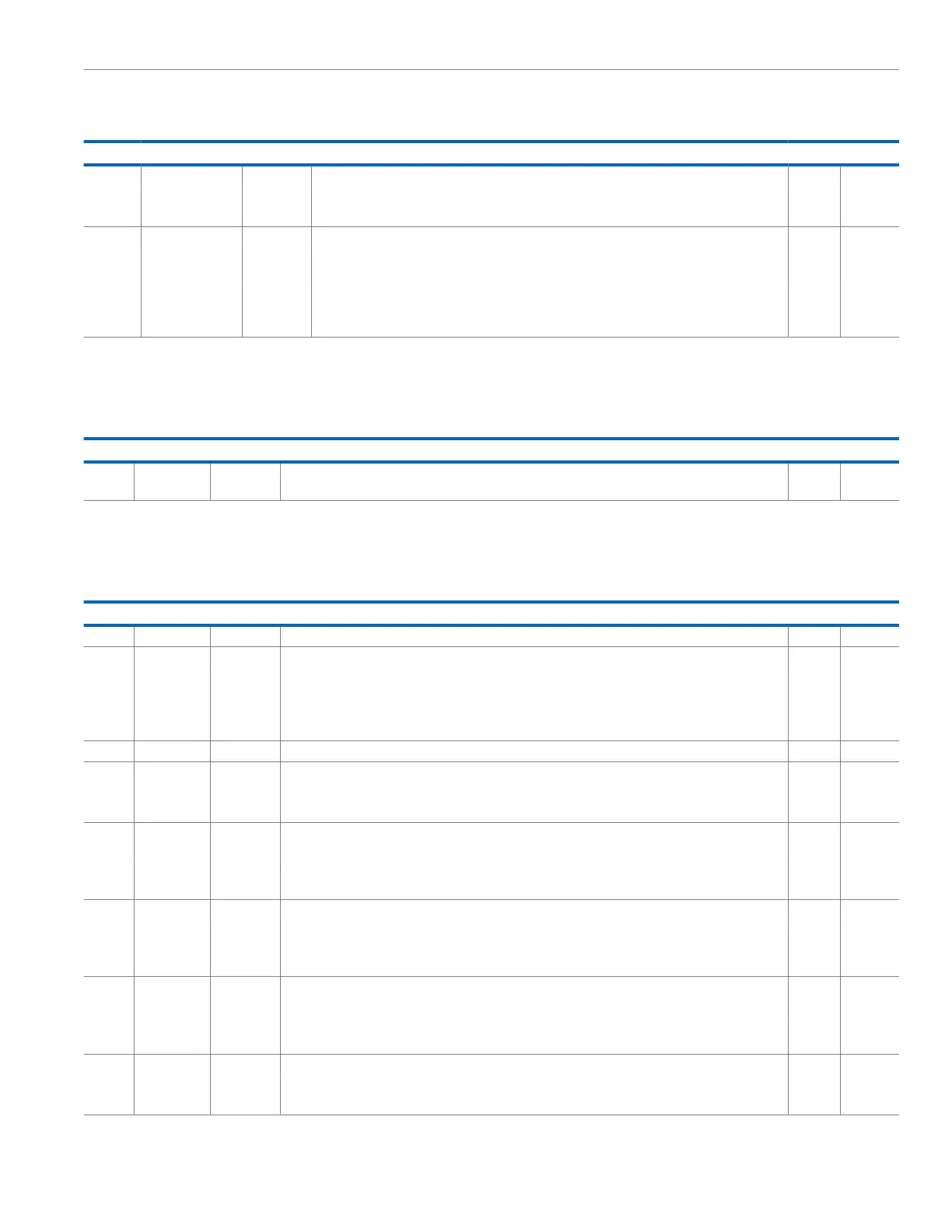

Table 377. Bit Descriptions for WDTSTA

Bits Bit Name Settings Description Reset Access

[15:7] Reserved Reserved. 0x0 R/W

6 TMINLD WDTMINLD Register Write Status. 0x0 R

0 The WDTMINLD value is fully updated. Arm and AFE watchdog clock domains and the WDTMINLD values

match.

1 WDTMINLD value update in progress. Arm peripheral bus and the WDTMINLD value are being

synchronized to the 32 kHz clock domain.

5 Reserved Reserved. 0x0 R

4 LOCK Lock Status. 0x0 R

0 Timer operation not locked.

1 Timer enabled and locked. Set automatically in hardware when WDTCON, Bit 5 has been set by user code.

3 CON WDTCON Write Status. 0x0 R

0 WDTCON is up to date. Arm peripheral bus and watchdog timer clock domains match WDTCON values.

1 WDTCON register synchronizing. The Arm peripheral bus and watchdog timer clock domains are in the

process of synchronizing with the WDTCON values.

2 TLD WDTVALS Write Status. 0x0 R

0 Arm and AFE watchdog clock WDTLD register values match.

1 Synchronize in progress. Arm peripheral bus WDTLD value is being synchronized to the 32 kHz clock

domain.

1 CLRI WDTCLRI Write Status. 0x0 R

0 Arm peripheral bus WDTCLRI write synchronization not complete.

1 Arm peripheral bus WDTCLRI write is being synchronized to WDT clock domain. WDT restarts (if 0xCCCC

was written) when latter synchronization is complete.

0 IRQ WDT Interrupt. Set to 1 when watchdog timer interrupt occurs. 0x0 R

0 Watchdog timer interrupt not pending.

1 Watchdog timer interrupt pending. Cleared by writing to WDTCLRI register.

Loading...

Loading...