Reference Manual ADuCM356

REGISTER DETAILS: SPI0/SPI1

analog.com Rev. A | 252 of 312

WAIT TIMER FOR FLOW CONTROL REGISTERS

Address: 0x4000402C, Reset: 0x0000, Name: SPI0_WAIT_TMR

Address: 0x4002402C, Reset: 0x0000, Name: SPI1_WAIT_TMR

This register is only used in initiator mode.

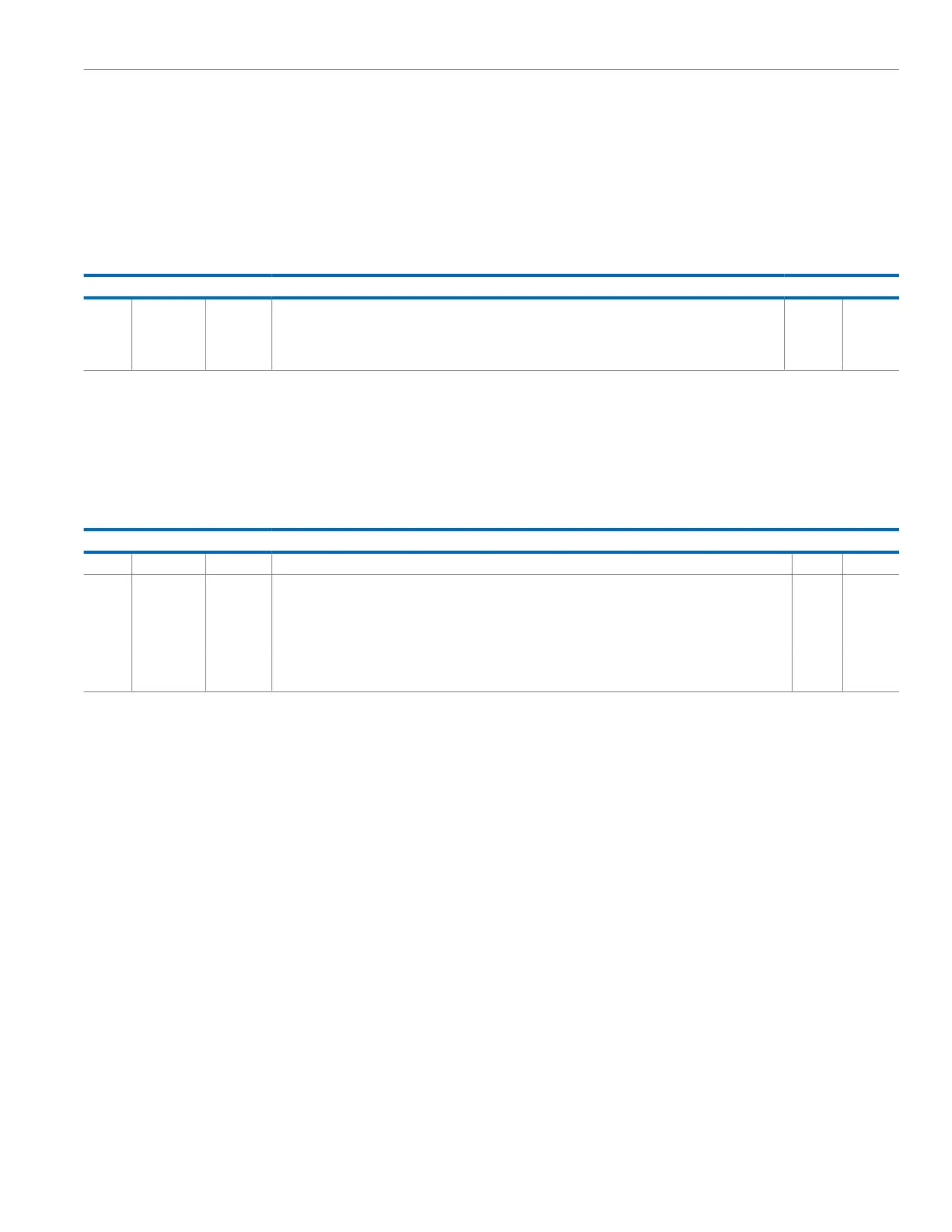

Table 317. Bit Descriptions for SPI0_WAIT_TMR, SPI1_WAIT_TMR

Bits Bit Name Settings Description Reset Access

[15:0] VALUE Wait Timer for Flow Control. This field specifies the number of SCLK cycles to wait before continuing the

SPI read. This field can take values of 0 to 65,535. This field is only valid if SPIx_FLOW_CTL, Bits[1:0] =

0b01b. For all other values of SPIx_FLOW_CTL, Bits[1:0], this field is ignored. A value of 0 implies a wait

time of 1 SCLK cycle.

0x0000 R/W

CHIP SELECT OVERRIDE REGISTERS

Address: 0x40004034, Reset: 0x0000, Name: SPI0_CS_OVERRIDE

Address: 0x40024034, Reset: 0x0000, Name: SPI1_CS_OVERRIDE

This register is only used in initiator mode.

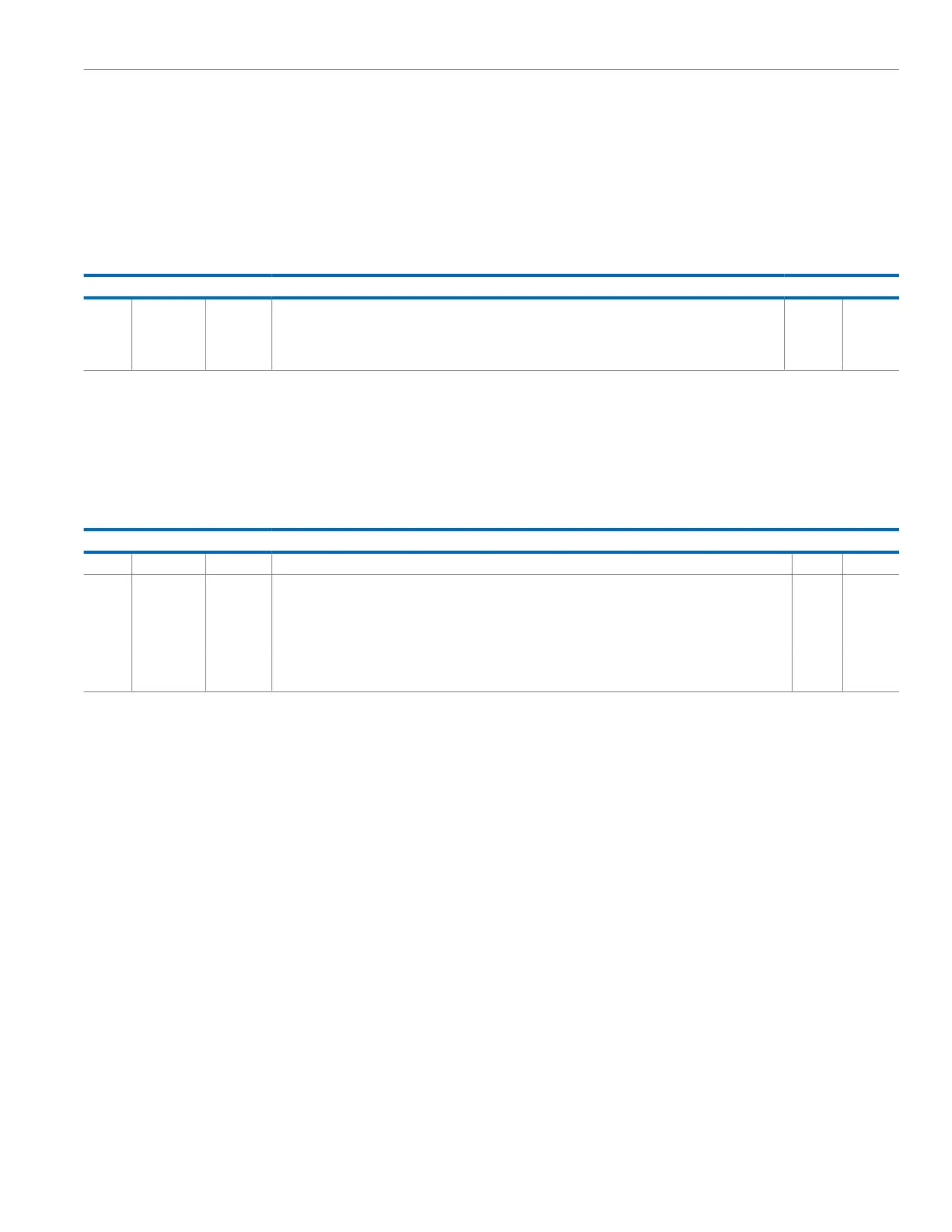

Table 318. Bit Descriptions for CS_OVERRIDE

Bits Bit Name Settings Description Reset Access

[15:2] Reserved Reserved. 0x0 R

[1:0] CTL Chip Select Override Control. This bit overrides the chip select output from the initiator state machine. This bit

may be needed for special SPI transfers. Do not use for normal SPI transfers.

0x0 R/W

00 Chip select is not forced.

01 Chip select is forced to drive 1.

10 Chip select is forced to drive 0.

11 Chip select is not forced.

Loading...

Loading...