Reference Manual ADuCM356

REGISTER DETAILS: FLASH CACHE CONTROLLER (FLCC)

analog.com Rev. A | 190 of 312

STATUS REGISTER

Address: 0x40018000, Reset: 0x00000000, Name: STAT

This register provides information on current command states, error detection, and correction.

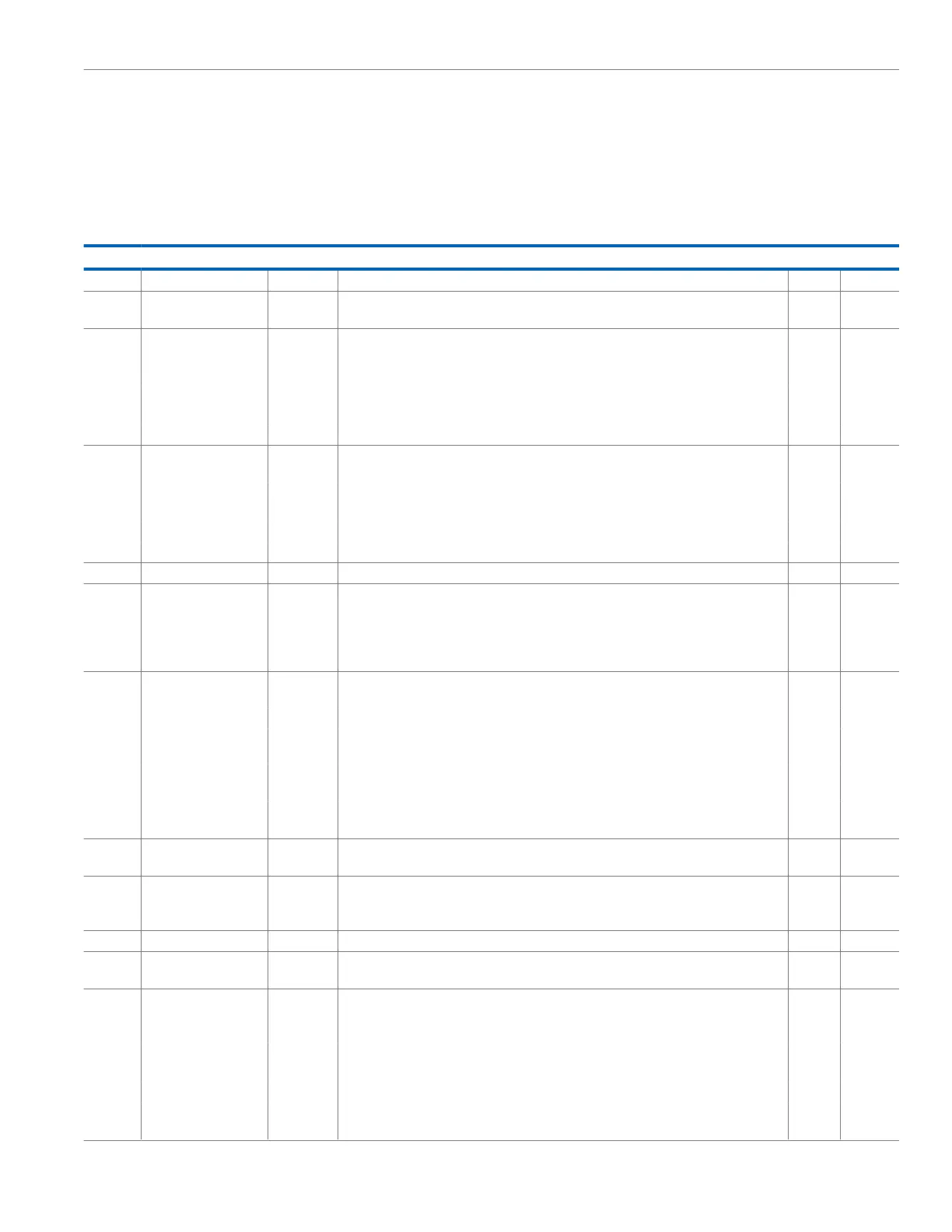

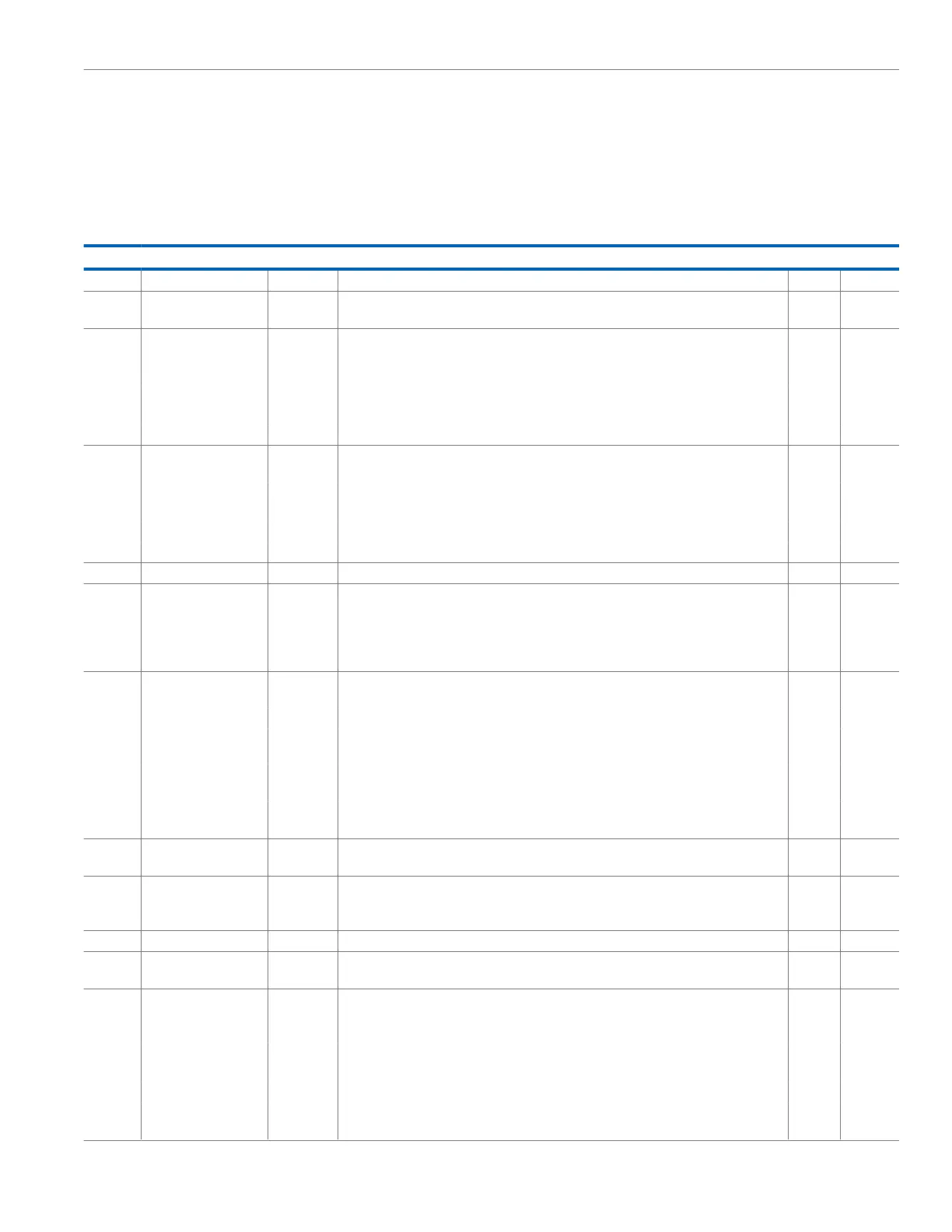

Table 224. Bit Descriptions for STAT

Bits Bit Name Settings Description Reset Access

[31:30] Reserved Reserved. 0x0 R

29 CACHESRAMPERR SRAM Parity Errors in Cache Controller. This register provides details for AHB errors

generated due to cache SRAM parity error on the ICode bus.

0x0 R

[28:27] ECCDCODE DCode AHB Error ECC Status. Provides details for AHB errors generated due to ECC errors

or corrections on the DCode bus.

0x0 R/W1C

00 No error. No errors or corrections reported since reset or the register was last cleared.

01 2-bit error. 2-bit ECC error has been detected and reported on AHB read access.

10 1-bit correction. 1-bit ECC correction has been detected and reported on AHB read access.

11 Reserved.

[26:25] ECCICODE ICode AHB Error ECC Status. Provides details for AHB errors generated due to ECC errors or

corrections on the ICode bus.

0x0 R/W1C

00 No error. No errors or corrections reported since reset or the register was last cleared.

01 2-bit error. 2-bit ECC error has been detected and reported on AHB read access.

10 1-bit correction. 1-bit ECC correction has been detected and reported on AHB read access.

11 Reserved.

[24:20] Reserved Reserved. 0x0 R

[19:17] ECCERRCNT ECC Correction Counter. This counter keeps track of overlapping ECC 1-bit correction reports.

When configured to generate IRQs or AHB errors in the event of an ECC correction event, this

field counts the number of ECC corrections that occur after the first reported correction. The

counter remains at full scale when it overflows and clears automatically when clearing either

the ECCICODE or ECCDCODE status bits.

0x0 R/W1C

[16:15] ECCINFOSIGN ECC Status of Flash Initialization. ECC status after the end of automatic signature check on

information space.

0x0 R

00 No error. No errors reported.

01 2-bit error. One or more 2-bit ECC errors detected during signature check. Signature check

has failed.

10 1-bit error. One or more 1-bit ECC corrections performed during signature check. Signature

check passes if checksum still matches.

11 1-bit and 2-bit error. At least one of each ECC event (1-bit correction and 2-bit error) were

detected during signature check. Signature check fails.

14 INIT Flash Controller Initialization in Progress. Flash controller initialization is in progress. Until this

bit deasserts, AHB accesses stall and APB commands are ignored.

0x0 R

13 SIGNERR Signature Check Failure During Initialization. Indicates an automatic signature check has failed

during flash controller initialization. The register value is valid only after the signature check

has completed.

0x0 R

12 Reserved Reserved. 0x0 R

11 OVERLAP Overlapping Command. This bit is set when a command is requested while another command

is busy. Overlapping commands are ignored.

0x0 R/W1C

[10:9] ECCRDERR ECC IRQ Cause. This field reports the cause of recently generated interrupts. The controller

can be configured to generate interrupts for 1-bit or 2-bit ECC events by writing the appropriate

values to IEN, Bits[7:6]. These bits are sticky high until cleared by user code.

0x0 R/W1C

00 No error.

01 2-bit error. ECC engine detected a noncorrectable 2-bit error during AHB read access.

10 1-bit correction. ECC engine corrected a 1-bit error during AHB read access.

11 1-bit and 2-bit events. ECC engine detected both 1-bit and 2-bit data corruptions, which

triggered IRQs. A single read can only report one type of event. This status indicates that a

Loading...

Loading...